Hardwarearchitekturen und Rechensysteme

Werbung

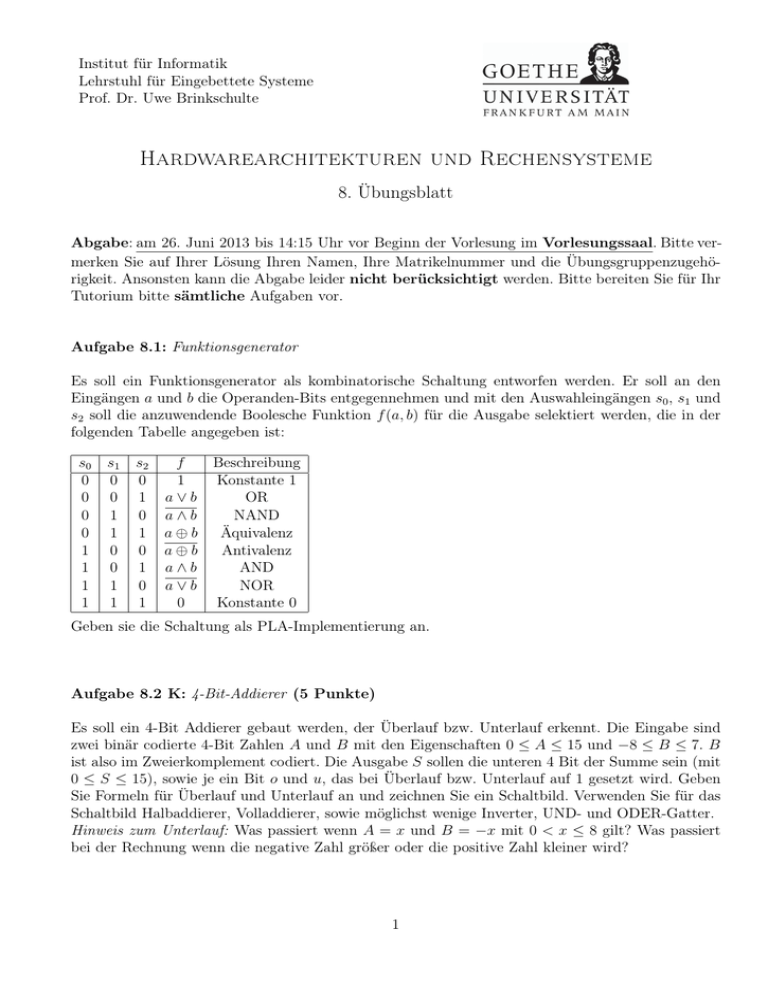

Institut für Informatik Lehrstuhl für Eingebettete Systeme Prof. Dr. Uwe Brinkschulte Hardwarearchitekturen und Rechensysteme 8. Übungsblatt Abgabe: am 26. Juni 2013 bis 14:15 Uhr vor Beginn der Vorlesung im Vorlesungssaal. Bitte vermerken Sie auf Ihrer Lösung Ihren Namen, Ihre Matrikelnummer und die Übungsgruppenzugehörigkeit. Ansonsten kann die Abgabe leider nicht berücksichtigt werden. Bitte bereiten Sie für Ihr Tutorium bitte sämtliche Aufgaben vor. Aufgabe 8.1: Funktionsgenerator Es soll ein Funktionsgenerator als kombinatorische Schaltung entworfen werden. Er soll an den Eingängen a und b die Operanden-Bits entgegennehmen und mit den Auswahleingängen s0 , s1 und s2 soll die anzuwendende Boolesche Funktion f (a, b) für die Ausgabe selektiert werden, die in der folgenden Tabelle angegeben ist: s0 0 0 0 0 1 1 1 1 s1 0 0 1 1 0 0 1 1 s2 0 1 0 1 0 1 0 1 f Beschreibung 1 Konstante 1 a∨b OR a∧b NAND a ⊕ b Äquivalenz a⊕b Antivalenz a∧b AND a∨b NOR 0 Konstante 0 Geben sie die Schaltung als PLA-Implementierung an. Aufgabe 8.2 K: 4-Bit-Addierer (5 Punkte) Es soll ein 4-Bit Addierer gebaut werden, der Überlauf bzw. Unterlauf erkennt. Die Eingabe sind zwei binär codierte 4-Bit Zahlen A und B mit den Eigenschaften 0 ≤ A ≤ 15 und −8 ≤ B ≤ 7. B ist also im Zweierkomplement codiert. Die Ausgabe S sollen die unteren 4 Bit der Summe sein (mit 0 ≤ S ≤ 15), sowie je ein Bit o und u, das bei Überlauf bzw. Unterlauf auf 1 gesetzt wird. Geben Sie Formeln für Überlauf und Unterlauf an und zeichnen Sie ein Schaltbild. Verwenden Sie für das Schaltbild Halbaddierer, Volladdierer, sowie möglichst wenige Inverter, UND- und ODER-Gatter. Hinweis zum Unterlauf: Was passiert wenn A = x und B = −x mit 0 < x ≤ 8 gilt? Was passiert bei der Rechnung wenn die negative Zahl größer oder die positive Zahl kleiner wird? 1 Aufgabe 8.3: PLA und PAL a) Wofür stehen die Abkürzungen PLA und PAL? b) Wie sieht die innere Struktur eines PLA- bzw. PAL-Bausteins aus? b) Wodurch unterscheidet sich ein ROM-Baustein von diesen Bausteinen? Aufgabe 8.4 K: Funktionsminimierung und PLA (5 Punkte) Es sollen folgende vier Funktionen möglichst kompakt in einem PLA realisiert werden. 1.) f1 (c, b, a) = 1 2.) f2 (c, b, a) = c 3.) f3 (c, b, a) = ac ∨ bc ∨ ab 4.) f4 (c, b, a) = ac ∨ ab ∨ bc Personalisieren Sie das gegebene PLA-Schema so, dass alle vier Funktionen in einer Schaltung realisiert werden. Hinweis: Die KV-Diagramme dienen als Hilfestellung um die zur Realisierung notwendigen Teilterme zu erkennen. c c c f2 : f3 : a 0 1 5 4 2 3 7 6 b f4 : a 0 1 5 4 2 3 7 6 b a 0 1 5 4 2 3 7 6 b 2