Übungsblatt 7 mit Musterlösung

Werbung

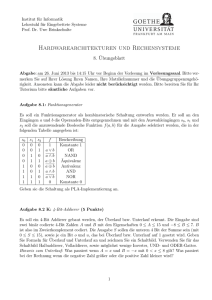

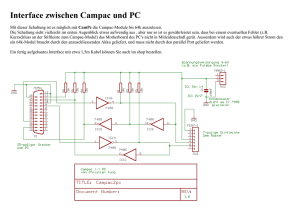

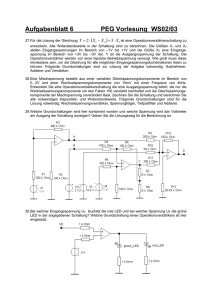

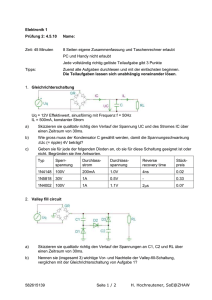

Musterlösung Übungsblatt 1 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 7 Prof. Baitinger / Lammert Aufgabe 1 Besprechung: 12.02.2001 DOMINO-CMOS Gegeben ist die DOMINO-CMOS-Schaltung in Abbildung 1-1 mit den Eingangssignalen x0, x1 und x2, dem Taktsignal φ sowie dem Ausgangssignal y. Die Eingangskapazität des Ausgangsinverters wird durch Cp dargestellt. U+ b) An die Schaltung werden nacheinander die in der Tabelle eingetragenen Eingangssignale angelegt. Tragen Sie die sich einstellenden Pegel für z und y ein und begründen sie das Ergebnis. φ x0 x1 x2 z y Begründung L L H H H L Da Tn sperrt und Tp leitet, lädt sich Cp auf H L H H L H Über T1, T2 und Tn entsteht ein leitender Kanal, wodurch sich Cp entlädt L L L H H L Da Tn sperrt und Tp leitet, lädt sich Cp auf H L L H H L Da T0 und T1 sperren, kann sich Cp nicht entladen c) Welche Schaltfunktion realisiert die Schaltung in positiver Logik? Logische Schaltfunktion: y = ( x 0 ∨ x 1 ) ∧ x 2 φ Tp x0 T0 T1 x2 z d) Wie viele Transistoren werden für die Realisierung eines Komplexgatters mit k Eingängen in DOMINO-CMOS-Schaltungstechnik benötigt, wie viele in statischer CMOS-Schaltungstechnik? y x1 T2 Anzahl der benötigten Transistoren : Cp DOMINO-CMOS: 2 + k + 2 = k + 4 (Tp+Tn+k NMOS-Transistoren+Inverter) Statisches CMOS: 2k (k NMOS-Transistoren+k PMOS-Transistoren) Tn e) Nennen Sie drei Vorteile der DOMINO-CMOS-Schaltungstechnik gegenüber der statischen CMOS-Schaltungstechnik. Abbildung: 1-1 a) Wie heißen die beiden Schaltphasen der DOMINO-CMOS-Schaltung? Welchen Spannunspegel (L=Low, H=High) nimmt φ jeweils an und wann leiten bzw. sperren die Transistoren Tp und Tn? Schaltphase φ Tp Tn Vorladephase L leitet sperrt Evaluierungsphase H sperrt leitet 1. Geringerer Flächenbedarf: Für größere Komplexgatter werden weniger Transistoren benötigt. 2. Höhere Geschwindigkeit: P-Kanal-Transistoren haben eine geringere Ladungsträgerbeweglichkeit und müssen daher größer dimensioniert werden als N-Kanal-Transistoren. Da bei DOMINO-CMOS-Schaltungen nur zwei P-Kanal-Transistoren verwendet werden, ist die Eingangskapazität kleiner und die Schaltung damit schneller. 3. Kleinere dynamische Verlustleistung: Wegen des geringeren Flächenbedarfs sind die Verbindungsleitungen kürzer und damit die parasitären Leitungskapazitäten kleiner. f) Welchen Nachteil ergibt sich bei DOMINO-CMOS-Schaltungen gegenüber statischen CMOS-Schaltungen? Seite 1 von 12 Seite 2 von 12 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Alle Ausgänge liefern nur während der Evaluierungsphase einen gültigen Wert. Daher ist möglicherweise eine Zwischenspeicherung der Ausgänge durch FlipFlops notwendig. b) Welche Schaltfunktion Y2 realisiert das nach Abb. 2-2 gegebene komplexe CMOS-Gatter in positiver Logik? U+ Aufgabe 2 Statische CMOS-Gatter E a) Gegeben sei die Schaltung in Abb. 2-1 aus statischem NMOS Schaltkreisen. Ermitteln Sie die Schaltfunktion Y1 (A, B, C, D, E) in positiver Logik . C D U+ A R B Y1 Y2 C A C A B D E B D E Abbildung: 2-1 Bei NMOS-Schaltungen gilt allgemein: Die Reihenschaltung von Transistoren ergibt eine UND-Verknüpfung, während die Parallelschaltung eine ODER-Verknüpfung darstellt. Durch einen Widerstand zur Betriebsspannung wird die gesamte Logikschaltung negiert: Y 1 = AB + C ( D + E ) Abbildung: 2-2 Eine CMOS-Schaltung besteht aus einem NMOS- und einem PMOS-Logikgatter, wobei beide Logikgatter diesselbe Schaltfunktion ergeben müssen. Das NMOS-Gatter ist identisch mit dem im Aufgabenteil a), nur der Widerstand zur Betriebsspannung ist durch ein PMOS-Gatter ersetzt worden: Y 2 = AB + C ( D + E ) Zur Kontrolle sollte noch das PMOS-Gatter untersucht werden: Hier bedeutet eine Reihenschaltung eine ODER-Verknüpfung, während eine Parallelschaltung eine UND-Verknüpfung darstellt. Ein Widerstand vom Ausgang des PMOS-Gatters zur Masse ergibt eine Negierung der gesamten Schaltfunktion. Dieser Widerstand wird bei CMOS-Schaltungen durch ein entsprechendes NMOS-Gatter realisiert: Y 2 = AB + C ( D + E ) Da sowohl NMOS- als auch PMOS-Gatter das gleiche Ergebnis liefern, stellt das gesamte CMOS-Gatter die oben angegebene Schaltfunktion dar. Seite 3 von 12 Seite 4 von 12 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 c) Realisieren Sie folgende Schaltfunktionen zuerst in NMOS- und dann in CMOS-Technologie. Die Eingangssignale A, B, C, D, E und F stehen auch negiert zur Verfügung. • Y 3 = AB + CD • Y 4 = AB + CD • Y 5 = AB ( C + D ) + E + F Hinweis: Y 3 = AB + CD , daher muß das Logikgatter noch durch einen Inverter negiert werden: U+ AB ↔ A UND B A + B ↔ A ODER B ↔ A Y4 NICHT A A C B D Abb. 2-3 zeigt die Realisierung der Schaltfunktion Y3: U+ Abbildung: 2-4 Y3 A Abb. 2-5 stellt die Schaltfunktion Y5 dar: C U+ B D Abbildung: 2-3 Y5 Abb. 2-4 stellt die Schaltfunktion Y4 dar. Der linke Teile der Schaltung realisiert A B E C F D Abbildung: 2-5 Seite 5 von 12 Seite 6 von 12 Elektrotechnische Grundlagen, WS 00/01 Musterlösung Übungsblatt 1 Für die CMOS-Gatter müssen alle Widerstände durch entsprechende PMOSGatter ersetzt werden: Abb. 2-6 zeigt die Realisierung von Y3 und Y4 in CMOS-Technologie: Abb. 2-7 zeigt Y5 in CMOS-Technologie: U+ U+ C A A B C D B D E F Y4 A C Y3 Y5 B A D B E Abbildung: 2-6 C F D Abbildung: 2-7 Seite 7 von 12 Seite 8 von 12 Elektrotechnische Grundlagen, WS 00/01 Aufgabe 3 Musterlösung Übungsblatt 1 c) Wie kann der ursprüngliche Zustand wieder hergestellt werden? Flipflop-Schaltungen Abb. 3-1 zeigt eine einfache Flipflop-Schaltung mit Transistoren. Zu Beginn der Betrachtung soll T2 leiten und T1 sperren; die Eingänge R und S liegen auf U = 0V . Die Versorgungsspannung sei U DD = 5V . UDD RC1 d) Was geschieht, wenn die Eingänge R und S zuerst gleichzeitig auf U = 5V und dann gleichzeitig auf U = 0V gelegt werden? RC2 RB1 RB2 Q Q T2 T1 R1 Der Ausgangszustand kann dadurch wieder hergestellt werden, daß der Eingang R auf 5V gelegt wird. Da die Schaltung symmetrisch ist, kippt die Schaltung wie unter (a) beschrieben wieder in ihren Ausgangszustand zurück. Dieser Zustand ist ebenfalls stabil, die Schaltung wird deshalb oft als bistabile Kippstufe bezeichnet, weil sie 2 stabile Zustände besitzt. Sie wird in statischen Halbleiterspeichern verwendet. Werden beide Eingänge auf 5V gelegt, leitet sowohl T1 als auch T2. Legt man daraufhin beide Eingänge auf 0V, kann nicht vorhergesagt werden, welchen der beiden stabilen Zustände die Schaltung einnimmt, es wird durch geringe Asymmetrien in der Schaltung (Bauteile-Toleranzen) bestimmt. Der Eingangszustand R = S = 5V wird deshalb verboten. Aufgabe 4 R2 Grundlagen von PAL, PLA und ROM a) Was bedeuten die Abkürzungen PAL, PLA und ROM ? S PAL = Programmable And-Array Logic PLA = Programmable Logic Array ROM = Read Only Memory R Abbildung: 3-1 a) Beschreiben Sie qualitativ das Verhalten der Schaltung, wenn am Eingang S eine Spannung von U = 5V angelegt wird. Wird an den Eingang S eine Spannung von 5V gelegt, so beginnt T1 zu leiten. Sein Kollektorpotential wird kleiner. Dadurch wird über RB1 die Basis-EmitterSpannung von T2 kleiner, die Kollektor-Emitter-Spannung von T2 wird größer. Über R1 wird dadurch der Effekt der Eingangsspannung verstärkt, es kommt zu einem Umkippvorgang, an dessen Ende T1 leitet und T2 sperrt. b) Wie verhält sich die Schaltung, wenn der Eingang S anschließend wieder auf U = 0V gelegt wird? Der Zustand der Schaltung ändert sich nicht, wenn S wieder auf 0V gelegt wird, da T1 über RB2 seinen Basisstrom erhält. Da T1 leitet, erhält T2 keinen Basisstrom und sperrt. Der Zustand der Schaltung ist stabil. Seite 9 von 12 b) Was versteht man unter der Personalisierung einer Schaltung ? Unter der Personalisierung versteht man die kundenspezifische Programmierung einer Schaltung. c) Bei welcher Schaltung (PAL, PLA und ROM) lässt sich die UND-Matrix personalisieren, bei welcher die ODER-Matrix ? UND-Matrix personalisierbar PAL X PLA X ROM ODER-Matrix personalisierbar X X Seite 10 von 12 Elektrotechnische Grundlagen, WS 00/01 Aufgabe 5 Musterlösung Übungsblatt 1 PAL- und PLA-Minimerung Eine Schaltung sei durch die nachfolgende Wahrheitstabelle spezifiziert, die für die Schaltfunktionen f1 und f2 gilt (“Funktionsbündel“). PLA j x2 x1 x0 f1 f2 0 0 0 0 0 0 1 0 0 1 1 1 2 0 1 0 1 1 3 0 1 1 0 1 4 1 0 0 1 1 5 1 0 1 1 0 6 1 1 0 1 * 7 1 1 1 0 0 x0 x1 0 1 1 1 1 0 0 1 x1 & c) Realisieren Sie jetzt das Schaltfunktionsbündel als PAL nach Abb. 5-3 und geben Sie dabei die Produktterme Q0 bis Q5 an. 1 0 1 1 1 0 * Für die Produktterme gilt: Q0 = P0 Q1 = P1 Q2 = P2 PAL x2 x1 x0 Q3 = P3 & f1 f1=P0+P1+P2 , f2 Q4 = P1 Q5 = P2 ∨ Q0 Q1 Q2 Abbildung: 5-1KV-Diagramme => ∨ P0 Abbildung: 5-2PLA x2 Für die Produktterme P0 ,...,P3 gilt: P0 = x0 x1 P1 = x0 x2 P2 = x0 x1 f2 f1 P3 0 x2 x0 P2 x0 f2 x1 P1 a) Minimieren Sie das Schaltfunktionsbündel (f1,f2) durch Mehrfachausnutzung von Produkttermen. Füllen Sie dabei die nachfolgenden KV-Diagramme aus und geben Sie die Produktterme P0, ..., P3 an. f1 x2 Q3 P3 = x0 x2 Q4 f2=P1+P2+P3 Q5 b) Zeichnen Sie die Personalisierung des PLA in die Matrix nach Abb. 5-2 ein. Für die UND-Matrix gilt: weißer Punkt = negierte Eingangsvariable angeschlossen; schwarzer Punkt = bejahte Eingangsvariable angeschlossen; kein Punkt = keine Eingangsvariable angeschlossen. Für die ODER-Matrix gilt: schwarzer Punkt = Produktterm angeschlossen; kein Punkt = Produktterm nicht angeschlossen. Seite 11 von 12 Abbildung: 5-3PAL Seite 12 von 12