Kapitel 2.1: Rechnerarithmetik

Werbung

Teil 2: Rechnerorganisation

Inhalt:

• Zahlendarstellungen

• Rechnerarithmetik

• Mikroprogrammierung

• schrittweiser Entwurf eines hypothetischen Prozessors mit

Daten-, Adreß- und Kontrollpfad

• Speicherorganisation

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

1

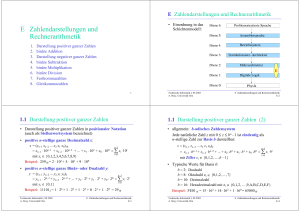

Zahlendarstellungen

Zahlendarstellungen in positionaler Notation :

• n-stellige ganze Dezimalzahl x:

x = (xn-1 xn-2 ... x2 x1 x0)10

= 10n-1 xn-1 + 10n-2 xn-2 + ... + 101 x1 + 100 x0

mit xi ∈ {0,1,2,3,4,5,6,7,8,9}

• n-stellige ganze Binär- oder Dualzahl y:

y = (yn-1 yn-2 ... y2 y1 y0)2

= 2n-1 yn-1 + 2n-2 yn-2 + ... + 22 y2 + 21 y1 + 20 y0

mit yi ∈ {0,1}

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

2

Zahlendarstellungen (Forts.)

Allgemein: b-adisches Zahlensystem

• Jede natürliche Zahl z mit 0 ≤ z ≤ 2n–1 ist eindeutig als

n-stellige Zahl zur Basis b darstellbar:

z = (zn-1 zn-2 ... z2 z1 z0)b

= bn-1 zn-1 + bn-2 zn-2 + ... + b2 z2 + b1 z1 + b0 z0

mit Ziffer zi ∈ {0,1,2, ... ,b–1}

• Typische Werte für Basis b:

b=2: Dualzahl

b=8: Oktalzahl

b=10: Dezimalzahl

b=16: Hexadezimalzahl mit zi ∈ {0,1,2, ... ,9,A,B,C,D,E,F}

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

3

Zahlendarstellungen (Forts.)

Verallgemeinerung für Festkommazahlen :

• Zahl zur Basis b mit k Vor- und m Nachkommastellen :

z = (zk-1 zk-2 ... z1 z0 , z-1 z-2 ... z-m)b

= bk-1 zk-1 + bk-2 zk-2 + ... + b2 z2 + b1 z1 + b0 z0

+ b-1 z-1 + b-2 z-2 + ... + b-m z-m

• Ziffern zk-1 zk-2 ... z1 z0 stellen ganzzahligen Teil,

Ziffern z-1 z-2 ... z-m stellen gebrochenen Teil von z dar

• gesamte Stellenzahl: n = k + m Ziffern

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

4

Zahlendarstellungen (Forts.)

Darstellung positiver und negativer Zahlen in n Stellen:

• höchstwertige Ziffer zn-1 stellt das Vorzeichen dar (Zahl ist

positiv bei zn-1 = 0, negativ bei zn-1= b–1)

• für positive Zahl gilt stets: z = (0 zn-2 zn-3 ... z1 z0)b

• drei Möglichkeiten für negative Zahlen (mit zi = b–1–zi):

A) Vorzeichen und Betrag : –z = (b–1 zn-2 zn-3 ... z1 z0)b

B) (b–1)-Komplement : –z = (b–1 zn-2 zn-3 ... z1 z0)b = bn –1 –z

C) b-Komplement : –z = (b–1 zn-2 zn-3 ... z1 z0)b +1 = bn –z

• bei A und B hat die Zahl 0 zwei Darstellungen

• für Binärzahlen (d.h. für b=2) heißt B das Einerkomplement und

C das Zweierkomplement

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

5

Zahlendarstellungen im Digitalrechner

• ausschließliche Verwendung von Binärzahlen

• Darstellung negativer Zahlen i.a. im Zweierkomplement

• Abbildung aller Zahlen auf Worte der Länge w, ggf. durch

Ergänzung führender Vorzeichenbits

• typische Wortlängen:

w=8

(byte, in Mikroprozessoren der ersten Generation, wie z.B. Intel

8080 oder Z80)

w = 16 (word / half word, in Minicomputern und Mikroprozessoren der

zweiten Generation, wie z.B. PDP-11, Intel 8086, Motorola 68000)

w = 32 (double word / word, in Mikroprozessoren der dritten Generation,

wie z.B. Intel Pentium, Motorola 68040)

w = 64 (quad word / double word, in aktuellen Hochleistungsprozessoren,

wie z.B. PowerPC, Alpha 21264, UltraSPARC)

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

6

Binäre Addition

• Addition zweier positiver n-stelliger Binärzahlen a und b kann

einfach spaltenweise durchgeführt werden:

• für Addition in letzter Spalte wird ein Halbaddierer benötigt,

der aus a0 und b0 Summe s0 und Übertrag (Carry) c0 ermittelt:

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

7

Binäre Addition (Forts.)

• für Addition in Spalten 1 bis n wird ein Volladdierer benötigt,

der Summe si und Übertrag (Carry) ci aus den Eingangssignalen

ai, bi und ci–1 ermittelt:

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

8

Binäre Addition (Forts.)

• paralleles binäres Addierwerk für zwei n-Bit Worte:

• serielles binäres Addierwerk für zwei n-Bit Worte:

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

9

Binäre Subtraktion

• Statt der Entwicklung eines eigenen Subtrahierwerkes ist es

sinnvoller, für die binäre Subtraktion die gleiche Hardware wie

für die Addition einzusetzen ⇒ Idee: a–b = a+(–b)

• einfach bei Verwendung des Zweierkomplements für b:

• korrektes Ergebnis bei Unterdrückung des Überlaufs

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

10

Binäre Subtraktion (Forts.)

• Realisierung eines parallelen binären Addier-/Subtrahierwerkes

(C=0 : Addition a+b, C=1: Subtraktion a–b)

• (wirklicher) Überlauf nur bei cout ≠ cin im FA der Stelle n–1

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

11

Weitere Addierwerke

Problem des parallelen binären n-Bit Addierwerkes, das auch als

„Ripple Carry Adder“ (RCA) bezeichnet wird:

Propagation des Carry Signals bis zur Stelle n–1 ist sehr langsam;

max. Verzögerung: 2n ∆t (mit ∆t Gatterlaufzeit)

alternative Addierwerke:

• „Carry Look Ahead“ Addierer (CLA)

• „Carry Select“ Addierer

• „Carry Save“ Addierer (CSA) für m Summanden

gemeinsam ist die Vermeidung der Propagation des Carry-Signals

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

12

„Carry Look Ahead“ Addierer (CLA)

• Idee: a priori Berechnung der Carry-Signale ci für alle n Stellen

• für i-ten Volladdierer gilt: ci+1 = aibi + (ai+bi)ci := Gi + Pici

– Gi = aibi gibt an, ob in Stelle i Carry-Signal erzeugt wird („Generate“)

– Pi = ai+bi gibt an, ob Stelle i das Carry-Signal propagiert (=1) oder nicht (=0)

• für die ci der ersten Stellen ergibt sich:

c1 = a0b0 + (a0 + b0)c0 := G0 + P0c0

c2 = G1 + P1G0 + P1P0c0

c3 = G2 + P2G1 + P2P1G0 + P2P1P0c0

c4 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0c0

• alle Signale ci lassen sich prinzipiell mit Gatterlaufzeit 2 ∆t

bestimmen, jedoch sind UND-Gatter mit max. i+1 Eingängen

und ODER-Gatter mit max. i Eingängen nötig

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

13

„Carry Look Ahead“ Addierer (Forts.)

• Beispiel:

4-Bit CLA

Addierer

• Kaskadierung möglich durch Ausgangssignale G („Block

Generate“) und P („Block Propagate“):

G = G3 + P3G2 + P3P2G1 + P3P2P1G0 , P = P3P2P1P0

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

14

„Carry Select“ Addierer

• In einem n-Bit „Carry Select“ Addierblock werden die

Summenbits sn-1, sn-2, ... ,s0 sowohl für c0= 0 als auch für c0=1

bestimmt und das Ergebnis über Multiplexer ausgewählt

• Beispiel: 4-Bit „Carry Select“ Addierer

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

15

„Carry Save“ Addierer (CSA)

•

Baustein zur Realisierung

eines mehrstufigen Addiernetzes für die Addition von

m Binärzahlen

•

Idee: Carry-Signale werden

nicht propagiert, sondern erst

bei Addition des nächsten

Summanden berücksichtigt

•

zur Addition von m Zahlen

werden m–2 CSA-Bausteine

benötigt

•

ein RCA oder CLA-Addierer

dient der Addition der noch

verbleibenden Überträge

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

16

Binäre Multiplikation

• Multiplikation zweier 1-Bit Werte entspricht einer logischen

UND-Verknüpfung 0×0=0, 0×1=0, 1×0=0, 1×1=1

• Multiplikation zweier mehrstelliger Zahlen ist zurückführbar auf

wiederholte bedingte Additionen und Schiebeoperationen

(in einfachen Prozessoren wird daher oft auf Multiplizierwerke verzichtet)

• Multiplikation zweier positiver n-stelliger Zahlen a und b ergibt

2n-stelliges Produkt p

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

17

Multiplizierwerke

Implementierungsvariante A

•

serielle Multiplikation durch

Addition und Rechtsschieben

•

Register p = (pH, pL) doppelter

Wortbreite zur Addition

partieller Produkte

•

durch Schieben von b wird nur

Multiplikatorbit b0 benötigt

•

mit zwei n-Bit Registern, einem

2n-Bit Register, einem n-Bit

Addierer und Steuerwerk direkt

in Hardware implementierbar

•

Multiplikation zweier n-Bit

Zahlen benötigt n Takte

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

18

Multiplizierwerke (Forts.)

Implementierungsvariante B

•

Idee: Implementierung des

Multiplikationsschemas in

Hardware („multiplier array“

zur parallelen Multiplikation)

•

max. Zeitverzögerung bei der

Multiplikation zweier 4-Bit

Zahlen: 15 ∆t

(mit Gatterlaufzeit ∆t)

•

max. Zeitverzögerung bei der

Multiplikation zweier n-Bit

Zahlen: 2(2n–1)+1 ∆t

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

19

Multiplizierwerke (Forts.)

Implementierungsvariante C

•

Idee: Addition der n Zeilen zi

aus n×n Bit Multiplikationsschema mit CSA-Bausteinen

•

entweder als CSA-Kette oder

CSA-Baum realisierbar

•

max. Zeitverzögerung bei der

Multiplikation zweier n-Bit

Zahlen (mit RCA am Ende):

(2(n-2) + 4n) ∆t

[Kette]

~ (2 log2 n + 4n) ∆t [Baum]

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

20

Multiplizierwerke (Forts.)

Implementierungsvariante D

•

Idee: Herleitung eines Schaltnetzes aus Wahrheitstabelle

eines n×n Bit Multiplizieres

•

Realisierung als ROM

•

max. Zeitverzögerung bei der

Multiplikation zweier n-Bit

Zahlen: 2∆t

•

Aufwand jedoch extrem hoch:

ROM mit 22n × 2n Bit nötig

•

Alternative: Verwendung von

k×k Bit Multiplizierern im ROM

und Addition der geschobenen

partiellen Produkte

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

21

Binäre Multiplikation negativer Zahlen

• bislang Betrachtung ausschließlich positiver Multiplikatoren

und Multiplikanden

• Was passiert bei negativen im Zweierkomplement kodierten

n-Bit Multiplikatoren und n-Bit Multiplikanden ?

a × –b = a × (2n –b) = a×2n – a×b

– a × b = (2n –a) × b = b×2n – a×b

– a × –b = (2n –a) × (2n –b) = 22n – a×2n – b×2n + a×b

(statt 2n – a×b)

(statt 2n – a×b)

(statt [22n ]+ a×b)

• ohne besondere Maßnahme (Addition von Korrekturtermen)

liefert binärer Multiplizierer falsche Ergebnisse !

• Alternative: Trennung von Vorzeichen und Betrag und separate

Generierung des korrekten Vorzeichens (⇒ hoher Aufwand)

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

22

Multiplizierer nach Booth

•

Idee: Vereinfachung der Multiplikation mit einer 1-Folge im Multiplikator,

z.B.: a × 001110 = a × 010000 – a × 000010

•

Analyse zweier benachbarter Bits bi und bi-1 im Multiplikator:

– Addition von a×2i bei (bibi-1) = 01

– Addition von –a×2i bei (bibi-1) = 10 (im Zweierkomplement, ergänzt)

– keine Addition bei (bibi-1) = 00 oder (bibi-1) = 11

•

Ergänzung von b-1 = 0 erforderlich

•

Beispiele:

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

23

Multiplizierer nach Booth (Forts.)

•

Multiplikation nach Booth funktioniert für beliebige positive und negative

Multiplikanden und Multiplikatoren

•

Algorithmus für serielle Multiplikation nach Booth mit doppelt breitem

Schieberegister p:

•

parallele Multiplikation nach Booth und schnelle Addition der resultierenden

Zeilen des Multiplikationsschemas mittels Wallace-Baum ist in den meisten

modernen Prozessoren implementiert

(jedoch häufig ergänzt mit Registern zwischen manchen Stufen zur

des Durchsatzes, auch als „pipelined multiplier“ bezeichnet)

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

24

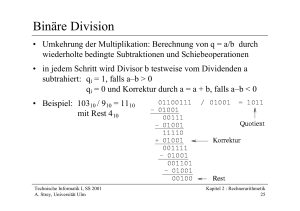

Binäre Division

• Umkehrung der Multiplikation: Berechnung von q = a/b durch

wiederholte bedingte Subtraktionen und Schiebeoperationen

• in jedem Schritt wird Divisor b testweise vom Dividenden a

subtrahiert: qi = 1, falls a–b > 0

qi = 0 und Korrektur durch a = a + b, falls a–b < 0

• Beispiel: 10310 / 910 = 1110

mit Rest 410

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

25

Binäre Division (Forts.)

•

serieller Algorithmus zur Division

zweier n-Bit Zahlen a und b:

•

mit einem n-Bit Register b, einem

2n-Bit Register q, einem n-Bit

Addierer/Subtrahierer direkt in

Hardware implementierbar

•

nach n Schritten befindet sich der

Quotient q in qL, der Rest in qH

•

in aktuellen Prozessorarchitekturen

eingesetzte Divisionsverfahren:

– iterative Approximation (durch

Multiplikation und Addition)

– SRT Algorithmus (simultane

tabellenbasierte Generierung

mehrerer Quotientenbits)

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

26

Gleitkommazahlen

• in vielen technischen und wissenschaftlichen Anwendungen

erforderlich:

– hohe Präzision und Genauigkeit

– große Dynamik

möglich durch Verwendung von Gleitkommazahlen

• allgemeine Gleitkommazahl zur Basis r („radix“) definiert

durch x = a × re mit

Argument oder Mantisse a

Exponent oder Charakteristik e

• eine Gleitkommazahl x ≠ 0 zur Basis r heißt normalisiert, wenn

für die Mantisse a gilt: 1/r ≤ a < 1

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

27

Binäre Gleitkommazahlen

• Verwendung der Basis 2, d.h. eine binäre Gleitkommazahl x ist

definiert durch x = a × 2e

mit m-stelliger Mantisse a

und p-stelligem Exponent e

• eine binäre Gleitkommazahl x ≠ 0 heißt normalisiert, wenn das

höchstwertige Mantissenbit den Wert 1 hat

⇒ zwei Interpretationen: 1.XXXXXXX und [0].1XXXXXX

• häufig Darstellung des Exponenten mit Bias b: x = a × 2e−b

Wahl von b = 2p–1 – 1 bewirkt Transformation des Bereiches für

den Exponenten e von 0 ... 2p – 1 in –(2p–1 –1) ... 2p–1

⇒ einfache Kodierung positiver und negativer Exponenten

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

28

Binäre Gleitkommazahlen (Forts.)

• Mantisse und Exponent können positiv und negativ sein

• viele Variationsmöglichkeiten bei der Definition eines Formates

zur Kodierung binärer Gleitkommazahlen:

1) Wahl der Gesamtwortbreite n

2) Wahl vom m und p = n–m

3) Wahl einer Reihenfolge von a und e

4) Darstellung der Mantisse im Einerkomplement, im Zweierkomplement

oder mittels Vorzeichen und Betrag

5) Darstellung des Exponenten im Einer- oder Zweierkomplement,

mittels Vorzeichen und Betrag oder durch Subtraktion eines Bias

• früher unterschiedliches Gleitkommaformat in jedem Prozessor,

heute überwiegend Verwendung des IEEE 754 Standard

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

29

IEEE 754 Standard

• allgemeine Definition: x = (–1)s × 1.f × 2e–b

• Mantisse aus Vorzeichen s und normalisiertem Betrag a = 1.f

im Bereich 1.00..00 bis 1.11..11

(1 vor dem Komma wird nicht kodiert ⇒ erhöhte Präzision)

• Aufbau einer n-Bit

IEEE Gleitkommazahl:

• p-stelliger Exponent mit Bias b = 2p–1–1, gültiger Exponent e

nur im Bereich emin= 0 < e < emax = 2p–1 = 2b+1

⇒ darstellbarer Zahlenbereich: ± 21–b ... (2–2–m) × 2b

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

30

IEEE 754 Standard (Forts.)

• 3 verschiedene Formate spezifiziert:

single precision

double precision

quad precision

n

32

64

128

m

23

52

112

s

1

1

1

p

8

11

15

emin

0

0

0

emax

255

2047

32767

b

127

1023

16383

| xmin |

2–126 ≈ 10–38

2–1022 ≈ 10–308

2–16382 ≈ 10–4932

| xmax | (2–2–23)×2127 ≈ 1038 (2–2–52)×21023 ≈ 10308 (2–2–112)×216383 ≈ 104932

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

31

IEEE 754 Standard (Forts.)

• e = emin = (00..00)2 und e = emax = (11..11)2 werden zur

Kodierung besonderer Zahlen verwendet:

x = +0 („positive Zero“): e = 0, f = 0, s = 0

x = −0 („negative Zero“): e = 0, f = 0, s = 1

x = +∞ („positive Infinity“): e = emax , f = 0, s = 0

x = −∞ („negative Infinity“): e = emax , f = 0, s = 1

x = NaN („Not a Number“): e = emax , f ≠ 0, s beliebig

x = (–1)s × 0.f × 21−b („Denormalized Number“): e = 0, f ≠ 0

• Denormalisierte Gleitkommazahlen ermöglichen die Darstellung

sehr kleiner Werte im Bereich 21−b−m ... 21−b

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

32

Multiplikation von Gleitkommazahlen

Algorithmus zur Multiplikation zweier IEEE-Gleitkommazahlen

x = (– 1)s × a × 2α−bias und y = (– 1)t × b × 2β–bias :

1) Multipliziere Mantissen: c = a × b

a=1.fa und b=1.fb haben m+1 Stellen ⇒ c hat 2m+2 Stellen !

2) Addiere Exponenten: γ = α + β – bias

3) Berechne Vorzeichen des Produktes: u = s ⊕ t

γ-bias

4) Normalisiere Ergebnis z = (– 1) × c × 2

a) Falls c ≥ 2, schiebe c um 1 nach rechts und inkrementiere γ

b) Schiebe c um 1 nach links

c) Setze c = 1.fc = (c2m+1 c2m c2m–1 ... cm+1), ggf. mit Rundung

5) Behandlung von Sonderfällen:

a) Überlauf, falls γ ≥ 2p – 1 ⇒ z := +∞ oder z := −∞ (bei u = 0 bzw. 1)

b) Unterlauf, falls γ < 1 ⇒ Denormalisierung durchführen

c) Zero, falls c = 0 ⇒ z := 0

u

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

33

Addition/Subtraktion von Gleitkommazahlen

Algorithmus zur Addition/Subtraktion zweier Gleitkommazahlen

x = (– 1)s × a × 2α−bias und y = (– 1)t × b × 2β−bias im IEEE Format:

1) Sortiere x und y derart, daß x die Zahl mit kleinerem Exponenten ist

2) Anpassung der Exponenten: Transformiere x in die Gleitkommazahl

x´ = (– 1)s × a´× 2β−bias durch Rechtsschieben von a um β−α Bitstellen

3) Addiere/Subtrahiere Mantissen:

a) Falls nötig, bilde Zweierkomplement von a´ oder b

b) Berechne c = a´ + b bzw. c = a´ + ( b)

c) Falls c < 0, setze Vorzeichenbit u = 1 und bilde Zweierkomplement

4) Normalisiere Ergebnis z = (– 1) × c × 2β–bias

a) Falls c ≥ 2, schiebe c nach rechts (ggf. Rundung) und inkrementiere β

b) Falls c < 1, schiebe c nach links und dekrementiere β

c) Wiederhole a) bzw. b), bis 1 ≤ c < 2 oder c = 0

5) Behandlung von Sonderfällen (Überlauf ? , Unterlauf ? , c = 0 ? )

u

Technische Informatik I, SS 2001

A. Strey, Universität Ulm

Kapitel 2 : Rechnerarithmetik

34