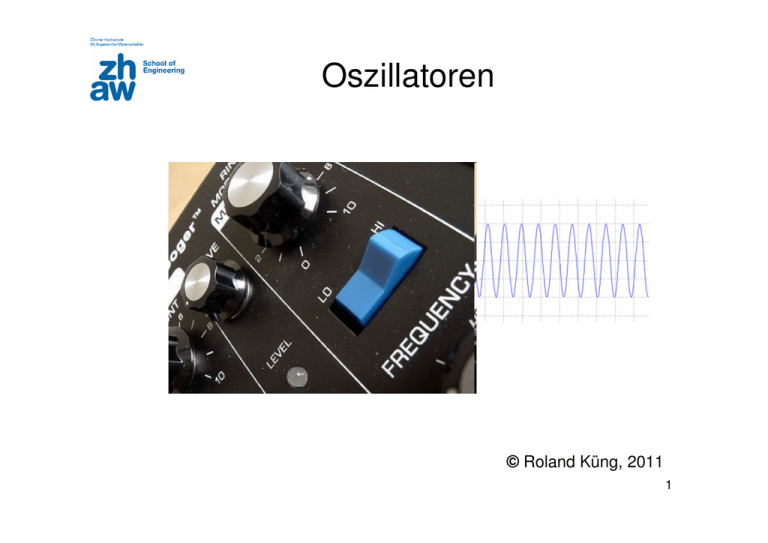

Oszillatoren

Werbung

Oszillatoren © Roland Küng, 2011 1 Methode 1: Mitkopplung • Echte Oszillatoren • Lösung einer DGL Aus Gegenkopplung wird Mitkopplung Instabil 2 Methode 1: Mitkopplung The Players Gain / 1800 Loss / 00 - 900 Bode Feedback Network Gain / 00 Loss / 00 -1800 3 Methode 1: Mitkopplung The Game 1800 4 3 2 1 Phase shift für jedes RC-Glied 00 … 900 00 … 2700 4 Methode 2: Kippschaltung The Players I Schmitt Trigger NI Schmitt Trigger • Bistabile Lösung • Hysterese Labiles System Vd= 0 gilt nicht mehr ! VOL = L0 VOH = L+ 5 Methode 2: Kippschaltung A: Astabiler Multivibrator The Game OpAmp mit Sättigungsspannung ± L Tperiod = 2 ⋅ RC ⋅ ln für L + VTH 1 = L − VTH f0 L = L + = −L − v TH = L + ⋅ R1 R1 + R 2 6 Methode 2: Kippschaltung B: Rechteck/Dreieck The Game C1 R1 R2 R3 OpAmp mit Sättigungsspannung ± L f= für R2 4 ⋅ R1 ⋅ C1 ⋅ R 3 L = L + = −L − VTH = - VTL = L + ⋅ R3 R2 Bsp. Für 1 kHz: C = 100n, R2 = 10k, R3 = 5k, R1 = 5k, L+ = 4 V Dreieck 2 Vpeak 7 Einige Oszillatorschaltungen •Oszillatoren mit Schmitt Trigger •Oszillatoren mit digitalen Gatter im Analogbetrieb •Quarzoszillatoren Takt •Wien Oszillatoren Sinus •Phase Shift Oszillator Sinus Logic Gates 8 Rechteck/Dreieck Integratorzeitkonstante Dreiecksymmetrie Variabler DC-Anteil Dreiecksignal, +U muss nicht mehr gleich –U sein 9 Sägezahn Für jede Flanke eigener Pfad 10 Logikbausteine Schmitt Trigger CMOS, HCMOS, ACMOS TTL 11 Logikbausteine Schmitt Trigger Verbesserung: Unabhängiger von Speisespannung Verbesserung: Künstliche Erhöhung Eingangswiderstand v.a. bei TTL notwendig 12 TINA: Oszillator Simulation: Problem wie merkt Tina dass Schaltung schwingfähig ist? TINA Sim Bsp.: Schmitt Trigger Oszillator für 800 Hz R2 100k Simulationszeitauflösung stimulieren U3 100k Inv. Schmitt Trigger aus Leiste Gatter - nicht Inverter benutzen ! - nicht logische IC‘s benutzen ! R1 1M + C1 1n U1 1 U2 0 VF1 Transientenanalyse: auf "Anfangsw erte verw enden" setzen VG1 Simulationszeit 10 ms VG1: 5 V 10 us Impuls 13 Logikbausteine - Linear • Vor allem CMOS Logik Inverter sind recht ansprechende Analogverstärker • Der Arbeitspunkt liegt in der Mitte der Versorgungsspannung • Er wird mit hochohmigen Widerstand vom Ausgang zum Eingang (R1) eingestellt • Die Verstärkung beträgt zwischen 20 und 1000 je nach Logikfamilie • Die Stromaufnahme ist aber nicht mehr wie bei den Logikanwendungen tief 14 Oszillator mit Invertern Analoge Schaltung! Mindestens 3 Inverter: Mehr als 360 Grad Phasendrehung möglich Labiler Gleichgewichtszustand nach Power on V1 = VCC/2 Abhilfe : Mehr Phasenverschiebung zwischen Eingang und Ausgang durch mehr Tore d.h. Verzögerung Anschwingen als klassischer Oszillator leitet den Kippvorgang ein 15 TINA: Oszillator Simulation: Problem wie merkt Tina dass Schaltung schwingfähig ist? TINA Sim Bsp.: Oszillator mit 3 Invertern für 500 Hz Inverter aus Leiste Gatter - nicht logische IC‘s benutzen ! U4 100k VG1 VF4 + VG1: min. VS1 Volt, 10 us Impuls R3 1M R1 1M C1 1n R4 100k VF3 Simulationszeitauflösung stimulieren >= erw artete Frequenz Transientenanalyse: auf "Anfangsw erte verw enden" setzen 1 1 U1 4069 U2 4069 U3 4069 VF1 VF5 VF2 1 Simulationszeit 5..10 ms 16 TINA: Oszillator Andere Speisespannungen (v.a. für CMOS) TINA Sim Bsp.: 9 Volt Oszillator mit 3 Invertern für 500 Hz Referenzspannungen für Logikbaustein: Jumpers J1 und J2 R2 100k + J1 VS1 9 J2 U4 100k VG1 VF4 + VG1: min. VS1 Volt, 10 us Impuls R3 1M R1 1M C1 1n R4 100k VF3 Simulationszeitauflösung stimulieren >= erw artete Frequenz Transientenanalyse: auf "Anfangsw erte verw enden" setzen 1 1 U1 4069 Erde J2 Vcc J1 U2 4069 Erde J2 Vcc J1 U3 4069 Erde J2 Vcc J1 VF1 VF5 VF2 1 Simulationszeit 5..10 ms 17 VCO Ein Oszillator dessen Frequenz elektrisch veränderbar ist, bezeichnet man als Voltage Controlled Oscillator vin Eigenbau Schaltungsblock in CMOS IC 4046 Abb. 15: • Aufladen von ext. Spannung via D2 mit R2 in der Zeitkonstante • Entladen durch Gatter via D1 mit R1 in der Zeitkonstante 18 Sägezahn Fig (17,18,19) RC Ladeglied (17,18) oder Konstantstromquelle (19) lädt C e-Funktion (17,18) oder lineare Rampe (19) am Gate-Eingang Gate entlädt (17,19) oder lädt (18) C lediglich Applikation: Wobbelspannungen, VCO Sweep, Ablenkspannungen 19 Praktikum Oszillator Stecken und überprüfen der Formel aus AN-118 von Fairchild Vcc = +5 V Messen im (DC mode): vout v2 v1 Design z.B. f = 100 kHz C = 100 pF 20 Quarzoszillatoren Bsp 10 MHz: L = 25 mH C = 0.01 pF R = 65 Ω C0 = 5 pF C0 = C a Cb + Cq C a + Cb Ersatzbild Quarz: Serie- und Parallelschwingkreis 2 Resonanzfrequenzen nahe beieinander Quarze vertragen keine grosse Verlustleistung ! max. 100 µW - 1 mW 21 Quarzoszillatoren fser fpar Betriebsarten: • in Serieresonanz als Kurzschluss bei Frequenz fser • in Parallelresonanz f0 zwischen fser und fpar als L- Ersatz in LC-Oszillatoren • bei fpar des Quarzes praktisch nie benutzt! Aufgabe: Bestimme fser und fpar: L = 25 mH C = 0.01 pF R = 65 Ω C0 = 5 pF Lösung: fser = 10‘065‘842 Hz fpar = 10‘075‘903 Hz 22 Quarzoszillatoren Häufigste Schaltung - Inverter: Phasenshift 1800 LC-Oszillator Gatter arbeitet linear R-C: Phasenshift < 900 und Strombegrenzung inverting L-C: Phasenshift < 1800 Design: klassischer Oszillator mit Verstärker und Mitkopplung Phasendrehung > 180 Grad durch R-C-L-C Netzwerk Quarz „emuliert“ das L 23 Quarzoszillatoren Quarz C0 = C a Cb + Cq C a + Cb Formeln für diesen Oszillator fosc = fser C tot = C0 + CL 1 fser = 2π LC C 1 1+ = C tot C C 2π L tot C tot + C Lastkapazität: Belastung des Quarzes in der Schaltung mit CL CL setzt sich aus C1 und C2 in Serie zusammen CL = C1C 2 C1 + C2 24 Quarzoszillatoren Aufgabe: Wo schwingt ein bei Distrelec bestellter Quarz mit Serieresonanz 10 MHz, wenn man in mit CL = 30 pF belastet? Daten Quarz: fser = 10 MHz C = 0.025 pF R = 65 Ω C0 = 5.5 pF CL = 30 pF Formeln: fosc = fser C tot = C0 + CL 1 fser = 2π LC C 1 1+ = C tot C C 2π L tot C tot + C Lösung: L = 10.132 mH f0 = 10‘003‘520.5 Hz 25 Quarzoszillatoren 26 Quarzoszillatoren Design mit Quarz in Serieresonanz: nur mit TTL empfohlen 2 Gatter haben 3600 Drehung: Rückführung also nur 1 Drahtstück Quarz spielt bei fser diesen frequenzselektiven Draht fosc = fser Viel Empirie drin 27 Quarzoszillatoren Takterzeugung Bis etwa 40 MHz Grundton, darüber Oberton Betrieb Ausgangssignal bis etwa 40 MHz Logikpegel, darüber meist Sinus < 1V Oszillatoren an Mikrokontrollern 28 Praktikum: Beginner Design: 2 MHz Quarz-Oszillator 2 MHz Quarz: RXTAL = 80 Ω C0 = 4 pF Designvorschlag: R1 = 470 Ω (typ.) CL2 = 47 pF (typ.) CL1 = 22 pF (typ.) RF = 1MΩ kompakt aufbauen! 100nF Vcc Block Cap! 29 Praktikum: Advanced Design: Safe working Test Safety Factor: RPOT max SF = RL SF > 3 ist safe, > 5 very safe 2 C0 R = R Resonanz-Lastwiderstand RL: L Xtal 1 + CL CL1CL 2 + Clayout Last Kapazität CL: CL = CL1 + CL2 Beim Design: Messen bis zu welchem Wert von RPOT Oszillator noch anschwingt RPOTmax Test immer mit Power OFF beginnen! Im definitiven Betrieb: 30 RPOT natürlich entfernen Klassische Sinus Oszillatoren A(s)·β(s) nennt man Schleifenverstärkung Schwingbedingung: s= jω 1 - A(s) ⋅ β(s) = 0 Lösung suchen: A(s) • β (s) = 1 IM ( A(s ) ⋅ β (s )) = 0 RE ( A(s ) ⋅ β (s )) = 1 31 Wien Oszillatoren Verstärker mit Av = 1+R2/R1 …also 00 Shift Mitkopplungsnetzwerk muss somit auch 00 Shift haben • Erreichbar mit CR-RC Bandpass • T(s) berechnen • Mittenfrequenz fr berechnen • Dämpfung in Bandmitte bestimmen (Resultat Faktor 3) • Av etwas grösser wählen als Dämpfung (z.B. 3.3) • Ausgang Va benutzen (gefiltert Sinus) 32 Wien Oszillatoren Praktisch: Abgleich R4: ist Av zu knapp: Risiko Abbruch der Schwingung ist Av zu gross: Verzerrungen nehmen zu Bei Av > min steigt Schwingung exponentiell an bis OpAmp in Sättigung geht Da OpAmp dann auch unerwünschte Phasenshift erzeugt ist es besser die Begrenzung mit Dioden selber extern vorzunehmen 33 Wien Oszillatoren Schleifenverstärkung Vs: Normalform: V s = [1+ 1 + R2 R1 R2 ] • Zp = R1 Zp + Zs 3 + pCR + 1 pCR pCR R2 ] ⋅ = [1 + Vs 2 2 2 R1 1+ 3CRp + C R p Phase wird 0 bei: 1 ωo CR = ωo CR 1 ωo = CR Amplitude bei ω0 wird 1 bei: | V s (ωo ) |= 1 1 + R2 = 3 R1 34 Phase Shift Oszillatoren zugleich Filterwirkung gegen Oberwellen ! 6 ωo = 6 ⋅ RC RF/RG = 29 Alternative: RC Hochpässe: 6 mal tiefere Frequenz, gleiche Vst. 1 ωo = 6 ⋅ RC RF/RG = 29 35 Phase Shift Oszillatoren Verbesserung (teurer): OpAmp Spannungsfolger nach jedem RC-Glied: 6 ωo = 6 ⋅ RC RF/RG = 29 Einfache Berechnung: Jedes RC-Glied macht 600 Shift Aufgabe: T(p) RC-Glied ? ω0 = ? Gain = ? Lösung: T( jω) = 1 1 + jωRC ωo = 3 RC RF/RG = 2*2*2 = 8 36 Praktikum TINA Design: Wien-Oszillator für 1 kHz Sinus 2 Vpeak „Starterquelle“ 500 µs Puls verwenden Frequenz Amplitude Phase Oberwellen Frequenz Amplitude Phase Oberwellen ωo = 1 CR + R3 1 + R4 ≥3 R5 R5 = 10 k R1 = R2=R C1 = C2 = C C = 100 n 37 Zusammenfassung 2 Arten von Oszillatoren: Kippschaltungen und Klassisch Kippschaltungen mit Schnitt Trigger realisieren (OpAmp oder Logik) Inverter Logik mit mindestens 3 Invertern bauen (geeignet für höhere Frequenzen) Bei Quarzoszillatoren arbeiten die Logik-Inverter im linearem Betrieb Quarz: Serie- oder nahe Parallelresonanzbetrieb (L-Ersatz) möglich Frequenz nur genau, wenn Lastkapazität = Spezifikation CL im Datenblatt Reservefaktor ermitteln mit Seriewiderstand zum Quarz schützt vor Ausfall Klassische Oszillatoren sind der Wien- und der Phasenschieberoszillator Verstärker Implementation mit Transistoren oder OpAmp 38