Vom Transistor zum Automaten - Prof. Dr. Hellberg EDV Beratung

Werbung

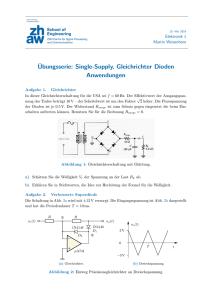

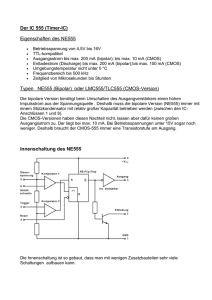

Vom Transistor zum HW-Automaten Technische Grundlagen der Informatik Prof. Dr. Michael Löwe (Grundlage: Tanenbaum/Goodman. Computerarchitektur. 1999.) Inhalt Schalterprinzip eines Transistors Gatter Logische Schaltungen Arithmetisch/Logische Einheit (ALU) Bit-Speicher Register Automaten in Hardware FHDW Vom Transistor zum Automaten 2 Schalterprinzip eines Transistors Kollektor Basis Emitter FHDW Basis-Emitter Kollektor-Emitter Spannung Widerstand 0 +Vcc Vom Transistor zum Automaten 0 3 Das erste Gatter VCC R1 Vout Vin 0 +Vcc Vout +Vcc 0 Vin In FHDW Vom Transistor zum Automaten NOT Out 4 Und-Gatter (fast) VCC R1 V1 V2 Vout V1 0 0 +Vcc +Vcc V2 0 +Vcc 0 +Vcc In1 In2 FHDW NAND Vom Transistor zum Automaten Vout +Vcc +Vcc +Vcc 0 Out 5 Oder-Gatter (fast) V1 R1 V2 Vout VCC V1 0 0 +Vcc +Vcc V2 0 +Vcc 0 +Vcc In1 In2 FHDW Vom Transistor zum Automaten NOR Vout +Vcc 0 0 0 Out 6 Übung Sei 0 Volt als „false“ oder 0 interpretiert und VCC als „true“ oder 1! Realisieren Sie Schaltungen für: • a b, a b, a XOR b • (¬a b) ¬(a c) FHDW Vom Transistor zum Automaten 7 Übung Realisieren Sie eine Schaltung für folgende Tabellen: IN1 IN2 IN1 IN2 OUT1 OUT2 (A+B) (Überlauf) IN3 OUT1 OUT2 (Überlauf) (A+B) (Überlauf) 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 1 0 1 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 FHDW Vom Transistor zum Automaten 8 Multiplexer D0 D1 D2 D3 S1 FHDW S0 Vom Transistor zum Automaten 9 Übung Dekodierer D0 S0 D1 S1 D2 D3 FHDW Vom Transistor zum Automaten 10 Übung ALU (Arithmetisch/Logische Einheit) IN1 IN2 Carry In F0 F1 FHDW ALU OUT Carry Out (1 Bit) Funktionen: • Addieren • Logisches Und • Logisches Oder • Logisches X-Oder Vom Transistor zum Automaten 11 Information speichern S ¬Q SR-Latch Q R FHDW Vom Transistor zum Automaten 12 Getaktetes SR-Latch S ¬Q Takt Q R FHDW Vom Transistor zum Automaten 13 Getaktetes D-Latch D ¬Q Takt Clk Q FHDW Vom Transistor zum Automaten 14 Register D1 D2 D3 D4 D ¬Q D Q D Clk Clk Clk FHDW Q D Clk Q1 Q D Clk Q2 Vom Transistor zum Automaten Q Clk Q3 Q Q4 15 Hardware-Automaten FHDW Vom Transistor zum Automaten 16 Hardware-Automaten Clk Register (n Bit) Input (m Bit) Next State (n Bit) Last State Logische Funktion (m+n Bit k+n Bit) Output (k Bit) Register (k Bit) FHDW Vom Transistor zum Automaten 17