- Stuettler.org

Werbung

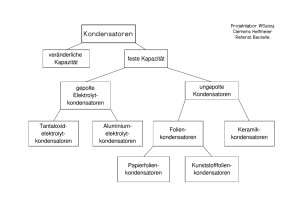

QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ Testung u. Qualitätssicherung QS in der Elektronikfertigung 1. QS in der Elektronikfertigung 1.1 QS beginnt beim Leiterplattendesign 1.2 QS im Einkauf 1.3 QS bei der Lagerung 1.4 QS in der Fertigung 2. Verifizierung der Fertigungsqualität: Fertigungstests 2.1 InCircuit – Testung 2.2 Ersatzmethoden 2.3 Schaltschranktestung 3. Anhang Auswertung der CAD-Daten 1. QS in der Elektronikfertigung Die Qualitätssicherung für elektronische Baugruppen erfordert : - spa Sicheres, Qualität begünstigendes Leiterplattendesign eine seriöses Einkaufsmanagment sachgemäße Lagerung überwachte Fertigung Fertigungstests 1/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ 1.1. QS beginnt beim Leiterplattendesign Qualität im Leiterplattendesign wird begünstigt durch : - Meidung der Bauteilgrenzwerte - Bauteile mit Second Source - Dokumentation, klare und ausführliche Fertigungsunterlagen - Bedachtnahme auf die Umweltproblematik ( Temperatur, Feuchte, Vibrationen ) - Bedachtnahme auf die EMV-Problematik ( Einstrahlung, leitungsgebundene Störungen, Abstrahlung ) - Reparatur- Wartungsfreundliches Design ( gute Zugänglichkeit, Stecker, Im-Feld-Prüfmittel, Modularität ) Qualität im Leiterplattendesign durch testfreundliches Design : - Tespads ca 1mm Durchmesser an einer Leiterbahnstich von 1.5mm Länge - Testpads gleichmäßig auf der Platine verteilt - OEs über Widerstand an Masse/Vcc legen - Abstand der Testpads >= 1.27 mm - Testpads an Netzen die I/Os der Platine kontaktieren in der Nähe der Stecker und Klemmen - ICs mit Funktionsmodell verwenden ansonsten ICs mit Boundary Scan - ICs mit langer Liefergarantie - Entwurf nur mit CAD zur automatischen Generierung der Adapterbestückung und des Testprogrammes - 1,5 mm Abstand von den zu plazierenden Bauteilen - 3,5 mm bauteilfreien Randstreifen - Mikroprozessoren sollen entweder über BoundaryScan verfügen oder es soll im Flash ein Testprogramm während des InCircuit - Tests laufen. Der Takt des Prozessors soll stimulierbar sein. - Batterien erst nach dem InCircuit – Test bestücken 1.2. QS im Einkauf Ein seriöses Einkaufsmanagment verlangt für jedes Bauteil eine detaillierte Spezifikation verfügen. Wichtige wichtige Angaben in Spezifikationen sind : - Spezifikation der Aufgabe mit Blockbild - Spezifikation der Signalpegel - Spezifikation der Versorgungspegel - Spezifikation der Stecker - Spezifikation Gehäuse und Montagebohrungen incl. Zeichnungen - eventuelle Einstellanleitungen - Spezifikation der Umweltbedingungen und Schutzart - Angaben über anzubringende Teilenummer - Spezifikation eventueller Herstellungsvorschriften ( Lackierung, Lack, Bohrerwechsel, In-Circuit-Test,.. ) - Spezifikation der druchzuführenden Warenausgangstests beim Hersteller - Erstellung und Änderungen von Spezifkationen müssen in der Spezifikation mit Datum und Namen vermerkt sein - Änderungen von Spezifikationen sind firmenintern mitzuteilen Technische Angaben und Hersteller - Lieferadressen sollten getrennte elektronische Dokumente sein : Die Wartung von Spezifikationen liegt beim technischem Fachpersonal, Hersteller/Lieferadressen können eventuell zur Änderung durch den Einkauf freigegeben werden. Spezifikationen sollten in Datenbanken erfasst werden ( elektronische Spezifikationen ) . Das garantiert leichte Änderbarkeit, Versionsverwaltung, verhindert eine Papierflut und erlaubt den Zugriff auf immer aktuelle Daten. Ein Verfügbarkeit über das Internet kann für den Service wertvoll sein. Zweckmäßig ist das Ablegen der Daten auch in die Steuerung ( in die Reparatur- und Wartungsdatenbank ) um Sie bei Reparaturen abrufen zu können. spa 2/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ Eine Wareneingangskontrolle ist für spezifizierte Prototypen unerläßlich. Die Wareneinganskontrolle und Versuche zur Dauerbelastung und Zyklenzahl von Waren, Sensoren und Maschinenteilen kann mit IPC's und speziellen Testsystemen oder Steuerungsprogrammieroberflächen ( eventuell zusätzlich Visualisierung und Datenbank ) automatisiert werden. Oft genügt eine stichprobenartige Testung. Der Aufwand für die Wareneingangskontrolle richtet sich nach den eventuellen Schadensausmaßen, der Personengefährdung und der Bewährtheit des Produktes und nach eventuellen Referenzen. Die Verlagerung der Wareneingangstestung hin zum Lieferanten als Warenausgangstestung ist vernünftig, aber unsicherer als die eigene Testung. Stecker Nicht ganz unerheblich ist die Steckerproblematik in der Maschinen-Steuerungstechnik. Achten Sie auf 'vorgehende' Kontakte, die Schutzart, eventuelle Codierungsnotwendigkeit, Platzbedarf, Schirmeignung und die Montagefreundlichkeit. Mil-Ausführungen sind teuer und nicht immer die besten Lösungen. Kunststoffstecker sind nicht korrosionsgefährdet wie die meisten Metallstecker ( auch Alu ist korrosionsgefährdet ! ). 1. 3. QS bei der Lagerung Eine sachgemäße Lagerung erfolgt entsprechend der Herstellererfordernissen und ein softwarebasiertes Ausscheidesystem für abgelaufene Ware. 1.4. QS bei der Verarbeitung Zur überwachten Fertigung gehören Stichproben von chemischen Bädern, von Platinenschliffbildern, BauteilTestung, Mannschaftsschulung, Führung von Statistiken über Ausfälle im Prüffeld / Ausfälle im Feld und über Kundenreklamationen, Zuteilung von Verantwortlichkeiten für die Qualitätssicherung, Einhaltung der einschlägigen Normen, Fertigungstests zur Prüfung der Fertigungsqualität. spa 3/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ 2. Verifizierung der Fertigungsqualität: Fertigungstests Die Fertigungstests dienen nicht direkt der Qualitätssicherung sondern der Evaluierung der Funktion der Qualitätssicherung im Einkauf und der Fertigung. Zu den Fertigungstests gehören : - InCircuit-Tests Funktionstests Echtzeittests Umwelttests (Temperatur-/Klima-/Vibrationstests ) Im InCircuit – Test werden die bestückten Leiterplatten mit Nadeladaptern kontaktiert und zuerst ohne Betriebsspannung auf Leiterbahnunterbrechungen und Kurzschlüsse, Bestückungsfehler und dann unter Betriebsspannung auf Bauteildefekte getestet. Funktionstests werden mit teilfertigen/fertigen Baugruppen gefahren. Spezielle Testprogramme laufen auf den Prozessoren der Baugruppe. Sämtliche I/Os der Baugruppe sind an einem Testgerät ( meist PC mit I/O-Karten ) angeschlossen. Das Funktionstest - Programm testet mit Prüfpatterns an den I/Os der Baugruppe. Im Echtzeittest wird das Arbeitsprogramm in die Baugruppe geladen. Die Baugruppe kann sich noch am Funktionstester oder bereits in der Maschine befinden. Umwelttests d.h. Temperatur/Klima/Vibrationstests werden oft getrennt, besser aber kombiniert durchgeführt. Den eigentlichen Klimatests kann eine Voralterung im Temperaturschrank vorausgehen. Beim eigentlichen Klimatest ist die zu testende Baugruppe im Klimaschrank in Funktion und es werden Testprogramme ( Funktionstests ) gefahren. Kosten der Testung in einem optimal gemanagten Qualitätssicherungssystem Hardware-Test-Kosten 20 10 3 1 InCircuitT. UmweltT. FunktionsT. EchtzeitT. entdeckte Fehler 100% 85% 2% 5% 1% 0 InCircuitT. UmweltT. FunktionsT. EchtzeitT. Die Bedeutung des InCircuit – Tests ist deutlich zu sehen. spa 4/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ 2.1 In Circuit Testung Der Nadeladapter ist am Rand mit einem gegen die Platine dichtenden Gummi versehen. Ein Vakuum zieht die Platine auf den Adapter und die federnden Nadeln werden auf die hierfür im Design vorgesehenen Testpads gedrückt. Um mit einem Adapter auskommen zu können, sollen alle Testpads auf der Lötseite liegen. Jeder Leiterzug ( man spricht jedes Netz ) muss mit einem Testpad versehen sein. Bei Leiterzügen an bedrahteten Bauteilen kann das Testpad entfallen : diese Leiterzüge werden durch Aufsetzen von Kronennadeln auf die Pins des Bauteils auf der Lötseite kontaktiert. Leiterzüge die auf Platinen-I/Os führen sollten nahe den Steckern/Klemmen mit Kontaktierungspads versehen sein, um den ganzen Leiterzug mittesten zu können. Sämtliche Nadeln sind auf eine Relaismatrix verdrahtet. Sie erlaubt die beliebige Verschaltung der Nadeln mit Messverstärkern, Signalgeneratoren und Spannungs-/Stromquellen. Die Verschaltung erfolgt automatisch im InCircuit - Tester mit geeigneten Testprogrammen. 2.1.1. Kontaktierungstest In der ersten Stufe des InCircuit - Tests erfolgt ein Kontaktierungstest. Er prüft den guten Kontakt der Nadeln auf den Testpads. Der Test erfolgt so, dass eine Spannung von 200mV ( unter der Durchlassspannung der Dioden auf der Platine ) auf die Nadeln gelegt wird und Widerstand eines jeden Netzes gegen jedes andere Netz bestimmt wird. Kontakt liegt vor, wenn R< 8Mohm. 2.1.2. Kurzschlußtest Der Test erfolgt so, dass eine Spannung von 200mV ( unter der Durchlassspannung der Dioden auf der Platine ) auf die Nadeln gelegt wird und Widerstand eines jeden Netzes gegen jedes andere Netz bestimmt wird. Ein Kurzschluß zwischen zwei Netzen liegt vor, wenn R< 10Ohm. 2.1.3. Bestückungstest Phase 1 In der ersten Phase erfolgt der Bestückungstest ohne Betriebsspannung. Im Bestückungstest wird das Vorhandensein eines Bauteils, seine richtige Einbauposition ( Verpolung ), und soweit als möglich seine Funktion überprüft. Die Prüfung erfolgt mit Spannungsquellen mit Strombegrenzung oder Stromquellen mit Spannungsbegrenzung. Dabei wird mit der sogenannten Guard – Methode jedes Bauteil selektiv geprüft obwohl es sich in einem Netzwerk von verbundenen Bauteilen befindet. Eine Ausnahme bildet der seltene Fall von zwei parallel geschalteten Widerständen. Dort ist eine selektive Messung nicht möglich aber auch wenig sinnvoll. Ua = 0.2*R/Rx ( Rx = 0.2R/Ua ) Guard Methode zur selektiven Messung von Rx eingebettet in ein Widerstandsnetzwerk bestehend aus 3 Widerständen R1 R2 Rx=? ( zu prüfen ) R 200mV Guard - Punkt R1 R2 Rx Die Guard-Punkte werden vom InCircuit - Tester automatisch durch Probieren ermittelt : Eine als funktionierend bekannte Schaltung wird in den Tester gelegt und der Tester variiert die Guard-Punkte bis er den richtigen Bauteilwert erkennt. Die Messung niederohmiger Widerstände kann, wenn geeignete Pads vorgesehen sind, auch in der 4- und 6- Leitermethode erfolgen. Im der ersten Phase des Bestückungstests werden zuerst die passiven Bauteile geprüft, dann die Transistoren ( pnp oder npn, und die Schaltfunktion ) , die Dioden ( Polung, Funktion ) , und Z-Dioden ( Polung, Z-Spannung ). spa 5/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ Phase 2 Erst in der zweiten Phase des Bestückungstests wird die Betriebsspannung an die Baugruppe angelegt. Diese Vorgehensweise des späten Anlegens der Betriebsspannung erst nach dem Kurzschlusstest und weitestgehenden Bauteiletests garantiert ein möglichst stressfreies Testen der Bauteile. In der zweiten Phase wird nach dem Anlegen der Betriebsspannung die Funktion der OPs geprüft : Sie werden als Komparatoren einmal mit positiver Spannung beaufschlagt und einmal mit negativer. Der Ausgang muß entsprechend ‚schalten’. Phase 3 In der dritten Phase des Bestückungstests werden die Digital – ICs geprüft. Diese Prüfung sollte wenn möglich anhand der sogenannten Funktionsmodelle erfolgen. Funktionsmodelle sind vom Hersteller erstellte Funktionsbeschreibungen im ASCII – Format, die die Funktion des Bauteils incl. Zeitverhalten sehr gut beschreiben. Die Funktionsmodelle können vom InCircuit - Tester abgearbeitet werden. Voraussetzung für die Anwendbarkeit von Funktionsmodellen ist das Vorhandensein solcher, Vorhandensein im Sprachformat des verwendeten InCircuit - Testers, und ein Design dass das Herauslösen des zu prüfenden ICs aus der Schaltung erlaubt. Das Herauslösen von Digital – ICs aus einer Umgebung von Digital – ICs ist durch Aktivierung des Tristate-Zustandes aller berührender ICs möglich. Damit der InCircuit - Tester die ICs hochohmig schalten kann muss der OE ( bzw. OE ) weich über einen Widerstand ( 500 Ohm bis 10k) auf Masse / Vcc gelegt sein. Nur so kann der Tester den OE auf eine beliebiges Potential zwingen und beliebige Bausteine auf Tristate schalten. Dies ist ein wichtiger, im Design zu beachtender Punkt. IC1 IC2 IC3 1k OE Testpad für OE Vcc Funktionsmodelle sind für viele ICs sogar für Prozessoren erhältlich. Bei der Testung von Prozessoren werden sämtliche Befehle und Prozessorfunktionen getestet. Der InCircuit - Tester emuliert dabei mit geeigneten Testpatterns an den Prozessorpins den Programmspeicher und die nötige Peripherie zur Testung der Befehle. Ist kein Funktionsmodell vorhanden, kann ein solches erstellt werden. Die Erstellung ist aber sehr zeitaufwendig und teuer. Ein Kompromiss hinsichtlich der perfekten Testung stellen die folgenden Ersatzmethoden zur Testung mit Funktionsmodellen dar. Die Ersatzmethoden stellen eine preisgünstige Alternative zur Modellerstellung dar. Ersatzmethoden sind : - Boundary Scan / InCircuit - Q-Probe - Flying – Probe ( nur Protoypen ) - reiner Boundary Scan - Test 2.2. Ersatzmethoden 2.2.1. Boundary Scan / InCircuit In BoundaryScan – ICs ( derzeit nur für Digital – ICs genormt ) liegt zwischen den IC-Pins und der internen Logik ein Register, das BoundaryScan – Register BSR. In das BSR können über den seriellen BoundaryScan – Bus Daten geschrieben werden. Das Kontaktieren der 5 Leitungen des BoundaryScan Busses und das Beschreiben des BoundaryScan Registers erfolgt über den InCircuit - Tester. Die Daten des BoundaryScan Registers können dann auf die I/O-Pins gelegt werden. Wenn jedes Netzwerk das einen Pin des ICs kontaktiert mit einer Testnadel kontaktierbar ist, kann das in das BSR- Register geschriebene Testmuster über die Prüfnadel auf den die I/O-Pins kontaktierenden Netzwerken verifiziert werden. Damit ist die Verlötung des ICs einwandfrei geprüft. BoundaryScan – ICs bieten oft auch die Aktivierung von Selbstestroutinen an, sodaß auch die IC- Funktion weitestgehend sicherstellbar ist. Schließlich können die sogenannte IC-ID ( IC-identification ) und Hersteller-ID ausgelesen werden. Damit wiederum ist die richtige Bestückung prüfbar. Die volle Erreichbarkeit eines I/O-Pins mit BS und mit den Nadeln wird als ‚voller Durchgriff’ bezeichnet. Siehe auch : ‚2.2.4.BoundaryScan’ . spa 6/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ 2.2.2. Q-Probe Für den Fall, dass für einen IC weder ein Funktionsmodell verfügbar ist, noch die Herstellung eines solchen als lohnend angesehen wird, und auch keine Boundary Scan Variante des ICs verfügbar ist, kann wenigstens mit der Methode der Q-Probe auf ordentliche Verlötung getestet werden. Die Q-Probe erfolgt im InCircuit - Tester. An den zu prüfenden IC wird eine flächige Prüfsonde herangeführt. Diese wird mit Wechselspannung gespeist. Sämtliche Netze werden vom InCircuit - Tester auf Masse gelegt. Nur jenes nicht, das die Verlötung des zu prüfenden Pins kontaktiert. Ist an jenem Netz eine Spannung messbar, ist die Verlötung in Ordnung. Ist keine Spannung messbar, so ist die Verlötung des Pins fehlerhaft. Die Spannung an dem nicht auf Masse liegenden Netz und Pin entsteht aufgrund der kapazitiven Kopplung der Q-Probe zum IC. 2.2.3. Flying Probe Der Flying-Probe Tester besitzt nur 4-8 Nadeln, die mit Roboterarmen an die Testpads bewegt und aufgesetzt werden. Der Flying-Probe Tester ist nur zur Testung ganz kleiner Serien wirtschaftlich verwendbar. Sein Vorteil besteht darin, dass kein Nadeladapter gebaut werden muß. Allerdings sind die Testmöglichkeiten eingeschränkt gegenüber dem InCircuit - Tester : nur eine geringe Anzahl von Guard-Punkten möglich, kein voller Durchgriff, keine Q-Probe, schließlich ist er sehr langsam ( max 10 Messungen / s ). 2.2.4. Boundary Scan Wenn InCircuit – Testung wegen der hohen Investitionskosten nicht gemacht werden kann, bietet sich im reinen BoundaryScan – Test eine Alternative, die aber qualitativ nicht so hochstehend und nicht so schnell wie die Testung mit dem InCircuit – Tester ist. Für gute BoundaryScan - Testung werden möglichst nur BoundaryScan Digital -ICs auf der Platine verwendet. Analogbauteile mit BoundaryScan sind in Entwicklung. Der BoundaryScan Bus wird seriell von Baustein zu Baustein geführt. Testung auf Kurzschlüsse, Unterbrechungen von Leiterbahnen und IC-Funktionstests sind selektiv möglich. Siehe auch Skriptum ‚JTAG BoundaryScan’. 2.3 Schaltschränke, Schaltschrankverdrahtung und Testung Schaltschränke sind zu verwenden : - wenn Leistungen geschaltet werden müssen zum Schutz der Leistungsschalter - eine besondere Schutzart dies erfordert - empfindliche Geräte untergebracht werden müssen - Eventuell, wenn sehr viele I/O's an einem Ort zusammenkommen sonst ist es meist billiger IP67 - I/O - Module im Freien anzubringen und über einen Feldbus zu bedienen. Schaltschrankheizungen verhindern Kondenswasserbildung. Sonneabschattbleche, Schaltschranklüfter mit Staubfilter, Schaltschrankkühlgeräte, die Montage auf Schwingelementen sind bei ungünstigen Umgebungsbedingungen vorteilhaft. Testen der Schaltschrankverdrahtung : Zum Testen der Schaltschrankverdrahtung dienen vorwiegend PC's mit I/O-Karten an die die Schaltschrankklemmen angeschlossen werden. Wenn keine Schraubklemmen zur Weiterverdrahtung ab dem Schaltschrank sondern Stecker und Kabelbäume verwendet werden, ist die Testung besonders einfach : Sie müssen nur angesteckt werden und der Test kann laufen. Deshalb empfiehlt sich dringend die Verwendung von Kabelbäumen und Steckern. In den Test sollte auch die I/O-Modul-Terminals der Steuerung miteinbezogen werden. Das kann dann besonders einfach erfolgen, wenn die I/O-Module einen Feldbusanschluß haben. Ansonsten muß der Verdrahtungstester über die Steuerung auf die I/O-Module zugreifen. Als Software zur Schaltschranktestung sind verschiedene Produkte erhältlich. Bedingt geeignet sind PCMeßprogramme ( LabView,.. ) oder PC-SPSen. Nur wenn gleichzeitig mit dem Schaltschranktest ein Softwarefunktionstest der Steuerung durchgeführt werden soll , ist als Testsoftware wieder eine Steuerungsprogrammieroberflächen sinnvoll. Sonst ist eine automatische Generierung des VerdrahtungsTestprogrammes aus den Daten des Schaltplanes zweckmäßiger. Der Schaltplan muß dann mit einem ElektroCAD erstellt worden sein. spa 7/8 QS in der Elektronikfertigung V0.0 __________________________________________________________________________________________ 3. Anhang : automatische Auswertung der CAD-Daten CAD-Schaltplan -> CAD-Bauteilliste : 1;C15;n3.3;t5%;g17;p2;xxxxxx;smd;ps13;px113;py37;Kommentar; 2;R33; .. .. 53;Z7; x;x;x;x;x;x;ps3;px153;py87;Testpad; Erläuterung : 1;C15;n3.3;t5%;g17;p2; xxxxxx; smd;ps13;px113;py37;Kommentar BauteilNummer; Bauteilbezeichnung; Wert; Toleranz; Gehäuse;Pins; Firmenidentnummer ; smd-Bauteil;Schaltplanseite;Schaltplan-x-Pos;Schaltplan-y-Pos; Kommentar CAD-Schaltplan -> CAD –Netzliste : Erläuterung : 1;;3/1;12/11;27/3;12/4; NetzNummer;;Bauteilnummer/Bauteilpin;Bauteilnummer/Bauteilpin;.. CAD-Layout -> 1;;3/1;12/11;27/3;12/4; 2;;... Bauteilliste2 : Bauteilliste2 = Bauteilliste mit eingearbeiteter Layoutinformation und eingearbeiteter TestPad-Information : 1;C15;n3.3;t5%;g17;p2;w90;s1;x242;y122;xxxxxx;smd;ps13;px113;py37;Kommentar;z17;z23; .. Erläuterung : 1;C15;n3.3;t5%;g17;p2; w90;s1;x242;y122;xxxxxx; smd;ps13;px113;py37; Kommentar;z17;z23; Nummer; Bauteilbezeichnung; Wert; Toleranz; Gehäuse;Pins; Winkel,Bestü-Seite;x-Pos-Layout;y-Pos-Layout;Firmenidentnummer smd-Bauteil;Schaltplanseite;Schaltplan-x-Pos;Schaltplan-y-Pos Kommentar; Pad-Nummer1; PadNummer2;.. Bauteilliste2 -> Bohrfile für Nadeladapter : 1;x123;y245;d0.2; 2;x113;y54;d0.1; .. Anzahl der Testpads -> Nadelliste : Z1=12.3 Z2=13.7 .. Erläuterung : Die Nadelliste wird vom InCircuit – Tester erzeugt und schafft eine Zuordnung von Nadelbezeichnung und Padbezeichnung Zxx Layout,Nadelliste -> Klebefolie für den Adapterbau : 3.5 12.4 1.12 4.7 Die Bezeichnung Zxx wird durch die Nadelnummer aus der Nadelliste ersetzt. Bauteilliste2 -> File für Bestückungsautomaten : 1; n3.3; g17; w90;s1;x242;y122; … Bauteilliste2,Nadelliste -> Programm für den Tester : C(nF)=2.2;Cmin(nF)=1.8;Cmax(nF)=2.6;TP13.8;TP12.9;delay(0ms); R(kOhm)=47;Rmin(kOhm)=43;Rmax(kOhm)=51;TP5.8;TP12.1;delay(2ms); ... Im wesentlichen wird die Bezeichnung Zxx für die Pads durch die Zuordnung in der Nadelliste ersetzt und bauteilspezifische Testdaten ( Rmin,.. ) hinzugefügt. spa 8/8