Arbeiten mit einzelnen Halbleiterbauelementen

Werbung

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2 Arbeiten mit einzelnen Halbleiter-Bauelementen

2.1 Einfache Transistor-Modelle

2.1.1 Bipolartransistor-Modelle

(a)

(b)

(c)

C

C

IC

IC

ICC

IEE

R

B

C

IC

IB

ICC

F

IE

B

= IDE

IDC

= IDC

IEE

ICC

R

IB

B

IEE

IB

ICC

IEE

F

IDE

IE

E

IE

E

E

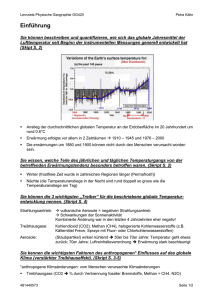

Bild 2.1.1: Ebers-Moll-Modell (ohne Basis-Bahnwiderstände):

(a) Vorwärtsmodell, (b) Rückwärtsmodell und (c) komplettes Modell.

Temperaturspannung: uT kT / q (=26mV für T=300K „Raumtemperatur“)

Boltzmann-Konstante: k=1,381E-23 VAs/K, Elementarladung: q=1,602E-19 As

Absolute Temperatur: T=0K = -273°C, T=273K = 0°C, T=300K = 27°C

(B0)

Diodengleichungen:

I DE

U BE

nU BEu

n F uT

F T

I SE e

1 I SE e

(B1.a)

und

I DC

U BC

nU BCu

n R uT

R T

I SC e

1 I SC e

(B1.b)

Sperrsättigungsströme IES und ICS liegen im Bereich 1fA...1pA,

Emissionskoeffizienten nF, nR liegen im Bereich 1...2, typischerweise in der Nähe von 1.

Großsignal-Modell nach Ebers-Moll (EM1) und vereinfacht nach Gummel-Poon (GP):

IC

IE

I CC I DC = F I DE I DC

I DE I EE = I DE R I DC

U BC

U BE

F uT

F I SE e n

I SE e

U BE

n F uT

- I SC e n R uT

R I SC e

U BC

n R uT

I B I C I E 0 => I B I DE (1 F ) I DC (1 R ) = I CC / ßF I EE / ßR

- SC / Seite 2-1 -

(B2.a)

(B2.b)

(B2.c)

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

x

1 (x=F,R).

1 x

x

F , R : Stromverstärkung in Emitterschaltung. x

(x=F,R).

1 x

F , R : Stromverstärkung in Basisschaltung. x

(B2.a)

(B2.b)

Das Reziprozitätstheorem fordert F I ES R I CS .

In der Schaltungstechnik versuchen wir, alle Größen als Funktion des Kollektorstromes

auszudrücken. Im Normalfall (Vorwärtsbetrieb) ist dann

IC = αF (-IE) = ßF IB.

-IE = IC / αF und IB = IC / ßF .

(B3)

Formal nimmt man alle Ströme das Bauelement positiv, so entsteht oben das negative

Vorzeichen vor IE. In der Praxis fließt ein positiver Emitterstrom meistens aus dem Emitter

heraus.

Early-Effekt. Um einen endlichen Kleinsignal-Ausgangswiderstand des Transistors zu

erhalten, wird eine nach ihrem Erfinder benannte VA Early-Spannung definiert. Typische

Vorwärts-Early-Spannungen liegen im Bereich 50V < VAF < 250Vund typische IS=20fA.

Primitivstes Modell: I C I S e

U BE / uT

U

11 CE

VAF

.

(B4)

Für die Schaltungstechnik wichtige Kleinsignal-Modelle:

Es sei UCE > UCE,sat. Alle Größen werden auf als f(IC) berechnet:

1 d ( I E ) I E

I

F 1

C

rm

dVBE

uT

uT

dI B

g

1

Basis-Emitter-Wid.:

g BE

m <=> rBE rm

rBE dVBE

I

dI C

I

1

Ausgangswiderstand: g CE

C ,sat C

rCE dVCE

VA

VA

V

L

Verstärkung:

AV g m (rCE R L ) R

gmrCE A

uT

Übertragungsleitwert: gm

- SC / Seite 2-2 -

=>

gm

(B6)

=>

rBE

IC

uT

u

T

IC

(B7)

=>

rCE

VA

IC

V

A

uT

(B8)

=> AV ,max

(B9)

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.1.2 Feldeffekt-Transistor-Modelle

2.1.2.1 Eingangs-Charakteristiken des Feldeffekt-Transistors

(a)

(b)

UDS = UGS-VT

UDS = UGS-VT

4

16

ID

mA

ID

mA

2

8

4mA

4

1V

UGS / V

0

-4

-3

-2

-1

0

UGS / V

0

-4

1

-3

-2

Bild 2.1.2.1-1: Eingangskennlinie eines FETs mit (a) I D und (b)

Ein FET liefere folgende Messdaten:

UGS / V:

ID / mA:

-2

1

-1

0

1

I D über UGS.

-1

4

1

16

Diese Daten sind in den Diagrammen in Bild 2.1.2.1-1 (a) und (b) dargestellt.

Die Schwellenspannung VT des FETs lesen wir am leichtesten im Bildteil (b) ab: VT=-3V.

IDSS ist der Strom in UGS=0V, abgelesen aus Bildteil (b): IDSS=ID(UGS=0V) = 32mA = 9mA

Frage: Handelt es sich um einen JFET (Sperrschicht-FET) oder um einen MOSFET?

Antwort: MOSFET, weil UGS=1V bei einem JFET nicht vernünftig möglich ist, sonst wäre

die Gate-Source-Diode leitend.

Übertragungsleitwert ist als Differenzenquotient (Ableitung) definiert: gm =

dI D

.

dU GS

Graphisch aus Bild 2.1.2.1-1 (a): gm(UGS=-1V) 4mA/1V = 4 mA/V

2

2

I D I DSS =

4mA 9mA = 4 mA/V.

Kontrollrechnung: gm(ID,VT,IDSS) =

| VT |

| 3V |

- SC / Seite 2-3 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.1.2.2 Ausgangs-Charakteristiken des Feldeffekt-Transistors

ID

mA

10

VT=-3V

IDSS=9mA

>0

=0

UGS=0V

lin. sat.

>0

5

=0

UGS= -1V

lin. sat.

UGS= -2V

>0

1

-Ua=-20V

=0

0

UDS

6V

Bild 2.1.2.1-2: Ausgangskennlinienfeld eines n-Kanal-FETs mit VT=-3V, IDSS=9mA.

Bild 2.1.2.1-2 zeigt die ID(UDS)-Kennlinien für λ=0 (gestrichelt) und λ>0 (durchgezogen).

Da Ua=20V in Bild 2.1.2.1-2 ist λ=1/Ua=0,05 wenn λ>0.

Die Abschnürgrenze ist bei UDS.sat=UGS-VT. Dies ist eine Parabel. Auf ihrer linken Seite ist

der sogenannte „lineare“ Bereich, in dem der FET ähnlich einem Widerstand arbeitet. Rechts

der Parabel ist der FET gesättigt. (Achtung: beim Bipolartransistor ist Sättigung genau anders

herum definiert.)

In Bild 2.1.2.1-2 ist die Grenze zwischen linearem Bereich und Sättigung gekennzeichnet

durch einem kurzen vertikalen Strich.

dI D

.

dU DS

Graphisch aus Bild 2.1.2.1-2: gDS(UGS=-1V,UDS=6V) 5,2mA/26V = 0,2mA/V = (5K)-1.

Der Ausgangsleitwert ist als Differenzenquotient (Ableitung) definiert: gDS =

Kontrollrechnung: gDS(ID,λ) λ ID = 0,05V-1 5,2 mA = 0,26 mA/V = (3,8K)-1.

2.1.2.3 Einfachste Modell-Gleichungen für MOSFET und JFET

Großsignal-Modell nach Shockley:

I D 2 ß ((U GS VT ) 0.5U DS )U DS (1 U DS ) für U DS U DS ,sat U GS VT

(F1.a)

I D ß (U GS VT ) 2 (1 U DS )

für U DS U DS ,sat U GS VT

(F1.b)

IS ID ,

für

IG 0

U GS VT 0

- SC / Seite 2-4 -

(F1.c)

Prof. Dr. M. Schubert

Substrat2 Si qN a

VT

'

COx

Skript Schaltungstechnik

(=Bulk-)

Hochschule Regensburg

USB=US(ource)-UB(ulk)

Vorspannung:

2F U SB 2F

,

(F2)

Sättigungsspannung:

VDS ,sat VGS VT

Sättigungsstrom:

I D ,sat ß (VGS VT ) (1 VDS )

(F4)

2

ß(VGS VT )

=>

2

(F5)

Kleinsignal-Modell: Es sei VDS > VDS,sat. Man bezieht alle Größen auf den Drain-Strom ID:

Übertragungsleitwert in der Sättigung: g m

dI D

1

2 (VGS VT )(1 VDS )

rm dVGS

=> g m 2 (1 VDS ) I D für 0 folgt g m

ZG

dI D

1

Ausgangswiderstand: g DS

I D ,sat I D

rDS dVDS

Gate-Widerstand:

Verstärkung:

=>

=>

0

2 I D

ZG

1

rDS

I D

L

AV gm (rDS RL ) R

g m rDS AV ,max => AV ,max

(F6)

(F7)

(F8)

2

ID

(F9)

Besonderheiten für FETs mit negativer Schwellenspannung: VT<0 (betrifft besonders JFETs)

Wir bezeichnen mit IDSS den Strom bei VGS=0. Dann ist IDSS= ß*(0-VT)2,

daher:

I DSS VT2

folglich:

gm

In Sättigung ist:

ID

VGS VT 1

I DSS

2

VT

<=>

I DSS I D

=

=

I DSS

VT2

(F10)

g m 2 I D

(F11)

VT

ID

(F12)

Hinweis:

Obiges Modell ist im Schaltkreis-Simulations-Programm Spice der UC Berkeley

implementiert. In der internationalen Literatur findet man oft ein ß, das wir hier ß' nennen

wollen, welches definiert ist zu ß'=2ß. Damit ergibt sich

I D ß'((VGS VT ) 0.5VDS )VDS (1 VDS )

für VDS VDS ,sat VGS VT

(F1'.a)

I D 0,5 ß'(VGS VT ) 2 (1 VDS )

für VDS VDS ,sat VGS VT

(F1'.b)

g m 2 I D (F4'),

I DSS 0,5 VT2 (F8').

- SC / Seite 2-5 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.1.3 Die Grundschaltungen von Bipolar- und Feldeffekt-Transistoren

(a) Emitter - Schaltung

(b) Basis - Schaltung

uout

uin

uin

(d) Source - Schaltung

uout

uin

(e) Gate - Schaltung

uout

uin

(c) Kollektor - Schaltung

uin

uout

(f) Drain - Schaltung

uout

uin

uout

Bild 2.1.3: Die drei Grundschaltungen für bipolare und Feldeffekt- Transistoren.

Jeder in einer Schaltung verwendete Transistor lässt sich in eine von drei Grundschaltungsarten einordnen: Emitter-, Basis oder Drain-Schaltung für bipolare Transistoren und Source,

Gate- oder Drain-Schaltung für Feldeffekt-Transistoren. Die Schaltung wird nach der

Elektrode benannt, die den steuernden Eingangskreis und dem gesteuerten Ausgangskreis

gemeinsam ist.

Die Kollektor-Schaltung wird oft auch Emitter-Folger genannt.

Die Drain-Schaltung wird oft auch Source-Folger genannt.

2.1.4 Dynamische und statische Groß- und Kleinsignal-Modelle

(b)

(a)

C

B

B

(c)

C

CBC

G

G

Q

rm

E

(d)

D

gm uBE

CBE

E

rCE

CCE

M

S

CGD

gm uGS

CGS

S

D

D

rDS

CDS

Bild 2.1.4: (a) BJT mit (b) dyn. Kleinsignal-ESB, (c) NMOSFET mit (d) dyn. Kleinsig.-ESB.

Die statischen Kleinsignal-Zugriffsimpedanzen von FETs und Bipolartransistoren lassen sich

gemäß dem Bild auf der folgenden Seite zusammenfassen.

Das Bild auf der übernächsten Seite stellt die Analysearten vor: Großsignal und Kleinsignal,

jweils dynamisch und statisch.

In den statischen Modellen wird Frequenz f=0 angenommen, so dass Kapazitäten zu

Unterbrechungen und Induktivitäten zu Kurzschlüssen werden.

Kleinsignal-Ersatzschaltbilder (ESBs) sind um den Arbeitspunkt (engl.: operating point)

linearisiert. Dann gilt lineare Superposition, bei der Groß- und Kleinsignalsignal-Größen

getrennt betrachtet und addiert werden können. Das Kleinsignal-ESB zeigt nur letztere.

- SC / Seite 2-6 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Kleinsignal-Impedanzen des Transistors :

rm + RD / AV,max

rDS + RS * AV,max

RS

RD

VDo

VSo

VG

8

Es ist :

1/gm = rm = rBE / ß

und AV,max = gm rDS bzw. AV,max = gm rCE

Alle angegeben Impedanzen sind Kleinsignal-Impedanzen gegen Masse.

rm + R B / ß

_ Z <

rCE <

C _ ß rCE

RE

RC

VCo

VEo

RB

VBo

rm + RE

ZC = rCE *

rm + RE / ß

rBE + ß RE

RE << rm

->

rm<RE<ßrm

RE >> ß rm

->

- SC / Seite 2-7 -

ZC = rCE

ZC = RE * Av,max

-> ZC = ß rCE

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.2 Transistoren als Schalter

2.2.1 Eigenschaften eines Schalters

(a) off

(c)

IC, ID bipolar:

sat.

mA

lin.

Is=0

Ron

UGS-Vth

Us

FET: lin. sat.

(d) Ron

(b) on

Is

Ron

Us

0

1

UCE, UDS

5

Bild 2.2.1: (a) Offener Schalter: Is=0, (b) geschlossener Schalter: Us klein,

(c) Ausgangsstrom / Ausgangsspannung für bipolare und Feldeffekt-Transistoren.

Schaltleistung eines Schalters: Maximale übertragbare Leistung: Ps = Us,max(off) * Is,max(on)

Verlustleistung des Schalters (erwärmt ihn): Pv,off = Us,off * Is,off ~ Us,off * 0 = 0

Pv,on = Us,on * Is,on = Rs,on * (Is,on)2

Idealer Zweipunktschalter: Us,on=0, Is,off=0 => Schalter erwärmt sich nicht: Pv,on=Pv,off=0 =>

100% Leistungsübertragung von der Quelle an den Verbraucher.

Elektr. gute Lösung: mechanisches Relais. Nachteile: langsam, bewegte Teile inkl. Verschleiß

2.2.2 Bipolartransistor als Schalter

Gon = 1/Ron = GCE(UCE=0) = ΔICE/ΔUCE @ UCE=0V

Vorteile als Schalter

+ hoher Strom auf kleiner aktiver Fläche

Nachteile als Schalter

- keine leistungslose Steuerung (Basisstrom)

Vorteile als Leistungs-Schalter

+ physikalisch relativ klein für große Ströme

+ Ron klein

Nachteile als Leistungs-Schalter

- neigt zum Durchbrennen in „Hot Spots“

Vorteile als Schalter in der Mikroelektronik

+ Guter Leistungstreiber (z.B. Taktpuffer)

Nachteile als Schalter in der Mikroelektronik

- physikalisch rel. groß in der Mikrotechnik

- Schalter leckt (wegen Basisstrom): IC IE

- Schaltverzögerung bei übersättigter Basis

- arbeitet nicht gut bidirektional

- SC / Seite 2-8 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.2.3 FET als Schalter

2.2.3.1 Generelle Eigenschaften (auch für Leistungsschalter)

Gon = 1/Ron = GDS(UDS=0) = ΔIDS/ΔUDS @ UDS=0V

Vorteile als Schalter

Nachteile als Schalter

- Leistungselektronik: phys. groß für große ID

+ Mikrotechnik ~1/10 der Größe eines Bip.

+ arbeiten sehr symmetrisch bidirektional

+ Schalter leckt nicht (kein IG,DC)

+ leistungslose Steuerung

+ keine Schaltverzögerungen wg. Übersättig.

+ gute Stromverteilung unter dem Gate =>

+ keine Neigung zu Hot-Spots => zuverlässig

Zitat aus Artikel “Power MOSFETs in Switching Applications”, Electronics & Technology Cosmos International, Febraury 2014 (Issue 1):

“Power MOSFETs have replaced bipolar transistors in many applications in the power

switching domain because they provide much higher switching speeds, low drive

requirements, high input impedance, and improved safe operating area. In addition, the drive

circuits are usually simpler than those using bipolar transistors.”

2.2.3.2 NMOS-Schalter in programmierbarer Logik

G

(a)

(c)

D

S

UDS

US

(b)

UG=5V, VT=0,75V

gDS

US

0

1

2

3

4

VDD

Bild 2.2.3.1: (a) MOSFET als Schalter, (b) GDS(Uout), (c) Anwendung: programmierb. Logik.

Bild 2.2.6(a) zeigt einen NMOSFET als Schalter mit UDS0 (sonst müssten S und D

vertauscht werden). Bildteil (b) zeigt die Leitfähigkeit des Schalters GDS(Uout)=ΔIDS/ΔUDS bei

UDS~0V. Eine typische Anwendung solcher Schalter, die Leitungen in einer programmierbaren Logik verknüpfen können, zeigt Bildteil (c). Gemäß Gl. (F1.a) ist

I D 2 ß ((U GS VT ) U DS / 2)U DS (1 U DS )

- SC / Seite 2-9 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Für sehr kleine UDS kann man Summenterme wie ½UDS oder λ·UDS (typ.: λ<<1/V)

vernachlässigen, eine Multiplikation mit UDS dagegen nicht. Daher folgt

DS 0

U

I D 2 ß (U GS VT )U DS .

Somit ist für der On-Leitwert eine mit UGS-VT steuerbare Größe:

Gon GDS

dI D

2 ß (U GS VT ) 2 ß ((U G VT ) U S )

dU DS

für UG ≥ US+VT.

Der Schalter soll leiten bei UG=VDD. Bei größer werdendem US nimmt der On-Leitwert ab,

denn er ist proportional (UG-VT)-US. Daher kann er US nicht auf Spannungen höher als

US≥UG-VT treiben, weil UGS = ≥ VT mit UGS = UG - US sein muss.

2.2.3.3 Transmission-Gate: komplementärer (=ergänzender) MOS-Schalter

(a)

(c)

(e)

UGn=5V, VTn=0,75V

UGp=0, VTp=-0,75V

G

(b)

GDSn

Gon

GDSp

(d)

Uout

0

1

2

3

4

VDD

Bild 2.2.3.2: (a) Transmission-Gate (TG), (b) kapazitiv ausgewogenes TG, (c) Symbol für

TG, (d) Schaltersymbol für TG, (e) Leitwert Gon des TG für UDS~0V.

Bildteil (a) oben zeigt zwei komplementäre FETs. Deren Leitwerte mit ßn=ßp so eingestellt

sind, dass ihre Summe Gon gemäß Bildteil (e) über einen weiten Spannungsbereich konstant

ist. Bildteil (c) zeigt das Symbol für ein Transmission-Gate (TG) und Bildteil (d) einen

Schalter, der als TG realisiert sein kann.

Bildteil(b) zeigt ein kapazitiv ausgewogenes TG. Da ßn=ßp verlangt, dass die Gate-Fläche

und somit die Kapazität des PMOSFETs ca. 2,7 mal größer ist, als die des NMOSFETs, wird

in Bildteil (a) der PMOSFET während der Taktflanken von entsprechend mehr Ladung

einstreuen (bekannt als „clock feed through“). Damit die durch den PMOSFET eingestreute

Ladung vom NMOSFET kompensiert wird, muss der NMOSFET eine gleich große GateFläche haben. Damit die Symmetrie der Leitwerte gemäß Bildteil (e) erhalten bleibt,

verwendet man zwei kurzgeschlossene NMOSFETs so, dass die gesamte Kapazität der drei

N-FETs genauso groß ist wie die des P-FETs.

- SC / Seite 2-10 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.2.4 Gemischt bipolare und CMOS (BiCMOS) Technologien

2.2.4.1 Vergleich der Vor- und Nachteile verschiedener Logik-Technologien

(a) TTL

VCC

(b) ECL

(c) C-Bipolar

(d) C-JFET

(e) CMOS

VCC

out

Ip

Bild 2.2.4.1-1: (a) TTL, (b) ECL, (c,d) Komplementäres Bipolar/JFET nicht mögl., (d)

CMOS

ECL: hält Transistoren sättigungsfrei unter Strom => sehr schnell + hoher Stromverbrauch.

MOSFETs nur in Si möglich, alle andere Technologien (GaAs, InPh,...) können nur JFETs.

Bild 2.2.4.1-2:

(a) NAND-Gatter Symbol

(b) NAND-Gatter realisiert

mit idealen Schaltern.

(c) Die Schalter in (b)

wurden durch MOSFETs ersetzt, wobei NKanal

MOSFETs

prinzipiell gegen VSS

und P-Kanal MOSFETs

prinzipiell gegen VDD

schalten müssen.

(a)

a

(c)

&

y

VDD

b

M1

b

M2

(b)

a

y

b

y

a

M3

b

M4

a

b

VSS

- SC / Seite 2-11 -

VSS

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.2.4.2 Gemischt bipolare und CMOS (BiCMOS) Technologien

(a)

(c)

(d)

a

a

y

&

b

VDD

M1

b

M2

u

VDD

Q1

R1

a

(b)

u

M1

b

y

M2

Q1

y

a

M3

b

M4

R1

a

y

v

M3

Q2

b

R2

v

M4

VSS

VSS

Q2

R2

Bild 2.2.4.2: BiCMOS Gatter (aus [1]): (a) Realisiertes NAND-Gatter, (b) „full swing totempole unit“, (c) CMOS-Realisierung, (d) BiCMOS-Realisierung, mit npn-Transistoren.

Bild 2.2.4.2 zeigt eine Möglichkeit ein CMOS-Gatter in BiCMOS-Technologie zu realisieren.

Die guten Eigenschaften der CMOS und der bipolaren Technologie werden kombiniert:

CMOS-Vorteil: Preiswert (kleine Flächenverbrauch, relativ einfache Technologie).

CMOS-Vorteil: Kein Stromverbrauch im stationären Zustand bei y='0' oder y='1'.

Bipolar-Vorteil: Starke Treibereigenschaften -> schnell

Weitere positive Eigenschaften des BiCMOS-Gatters

Ausgangsspannung mit „full swing“, also von VSS ... VDD möglich

Beliebig viele Eingänge möglich

Eingangsspannung mit „full swing“, also von VSS ... VDD möglich

Es wird kein pnp-Transistor benötigt (würde zusätzliche, sehr tiefe n-Wanne benötigen)

Nachteile des BiCMOS-Gatters:

Es werden pipolare Transistoren benötigt

Es werden Widerstände benötigt

Wegen der nicht zu vernachlässigenden Nachteile wird man nur solche Gatter nur dort

verwenden, wo große Lasten mit steiler Flanke treiben werden muss (z.B. als Takt-Puffer).

Aufgaben der Widerstände R1, R2:

Schnelligkeit: Entladung der Basen von Q1 und Q2, wenn diese die Q’s übersättigt sind,

„Full swing“ am Ausgang: R1, R2 ermöglichen maximale Aufladung der kap. Last gegen

VDD über M1, M2, R1 u. Restentladung einer kapazitiven Last gegen VSS über M3, M4, R2.

- SC / Seite 2-12 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.3 CMOS-Technologie: Eigenschaften und technische Bedeutung

Die CMOS-Technologie ist heutzutage die alles dominierende Technologie in der

Digitaltechnik. Diese Tatsache beruht auf der Kombination zweier Eigenschaften des

MOSFETs:

1. Leistungslose Steuerung

2. Gate im gesamten Spannungsbereich 0V...VDD isoliert

3. Verfügbarkeit komplementärer Transistoren

Damit lässt sich erreichen, dass ein logisches CMOS-Gatter Leistung ausschließlich für

Schaltvorgänge benötigt. Die Schaltungsgröße ist daher wärmetechnisch begrenzt auf die

kühlbare Anzahl an Schaltvorgängen pro Sekunde und Chip. (Die in einer Kapazität

gespeicherte Energie ist EC= ½CU2, der Leistungsbedarf bei f Umladungen pro Sekunde

P=f·EC=½fCU2. Die Leistungsaufnahme einer CMOS-Technologie ist also proportional der

Taktfrequenz f, der Gate-Kapazitäten CG und dem Quadrat der Versorgungsspannung VDD.)

Alle anderen Technologien benötigen einen Ruhestrom proportional zur Anzahl der Gatter.

Ihre Schaltungsgröße ist daher wärmetechnisch begrenzt auf die kühlbare Anzahl an Gattern

pro Chip.

Betrachtet man die drei Inverter in den drei verschiedene Technologien in Bild 2.3.1-1, dann

kann erst einmal nur der CMOS-Inverter einen Ausgangs-Low-Pegel von 0V erreichen.

(a)

(c)

(b)

RC

M2

RB

Mp

Uout

Uout

Uin

VDD

VDD

VCC

Q

Uin

Uin

Mn

M1

0V

0V

0V

IC

ID1

IDn

A

A

A

100

100

100

50

50

50

0

0

0,3

0

1

Uout

Uout

3

0

0

1

Uout

3

0

1

Bild 2.3.1-1: Inverter in drei Technologien (a) bipolar, (b) NMOS, (c) CMOS.

- SC / Seite 2-13 -

Uout

3

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Beispiel zu Bild 2.3.1-1(a): Der bipolare Inverter in Bildteil (a) habe einen Ausgangs-LowPegel von 0,3V bei VCC=3V und RC=27KΩ?

Dann ist der Kollektorstrom IC bei Ausgangs-High-Pegel (Uin=0,3V) μA und bei AusgangsLow-Pegel IC = (3V-0,3V)/27KΩ = 100μA.

Beispiel zu Bildteil (b): Der NMOS-Inverter in Bildteil (b) besteht aus zwei n-KanalMOSFETs, nämlich dem selbstsperrenden M1 (z.B. mit der Schwellenspannung VT1=1V) und

mit dem selbstleitenden M2 (z.B. mit VT2=-1V und IDSS=100μA).

Nimmt man für beide λ=0 an, dann ist der Drainstrom ID bei Ausgangs-High-Pegel 0μA bei

Ausgangs-Low-Pegel ist (willkürlich angenommen) ID2 = IDSS = 100μA Wegen UGS2=0V.

Der selbstleitende n-Kanal-MOSFET M2 sättigt bei UDS2,sat = UGS2 - VT2 = 0V–(-1V) = 1V.

Dies entspricht einer Ausgangsspannung von Uout,sat2 = VDD - UDS2,sat = 3V - 1V = 2V. Für

kleinere Uout arbeitet M2 als Stromquelle.

Beispiel zu Bildteil(c): Ein CMOS-Gatter führt nur während des Schaltvorganges einen

statischen Strom, wie es in (c) für einen maximalen Ausgangsstrom von 100μA skizziert ist.

Folgerungen: Bipolar und NMOS ziehen nur bei Ausgangs-Low-Pegel einen statischen

Strom, CMOS in keinem der Pegel.

Andere logische Gatter, z.B. NOR, in diesen Technologien erhält man, indem man dem

Biopolartransistor in Bildteil (a) oder dem FET M1 in Bildteil (b) gleichartige Transistoren

parallel schaltet. Bei CMOS werden weitere komplementäre Transistorpaare eingefügt. Der

Stromverbrauch ändert sich durch solche Modifikationen nicht gegenüber dem oben

berechneten Stromverbrauch eines Inverters.

In einer großen Digitalschaltung kann man davon ausgehen, dass ca. 50% aller

Gatterausgänge eine logische '0' und der Rest eine logische '1' treiben. Daher ist die Größe

einer digitalen CMOS-Schaltung wärmetechnisch begrenzt durch Schaltvorgänge pro

Sekunde und Chip. In allen anderen Technologien ist sie begrenzt durch Gatter pro Chip.

(a)

(b)

SRAM cell

D

WA

D

WD

RD

WA

RA

D

D

RA

WD

RD

Bild 2.3.1-2: "Static Random Access Memory" (SRAM) Zelle (a) Gatterebene mit den

Leitungen "Write Data" (WD), "Write Address" (WA), "Read Address" (RA) und "Read

Data" (RD), (b) Standardrealisierung in CMOS als 6T(ransistor)-Zelle.

- SC / Seite 2-14 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Bild 2.3.1-2 zeigt einen Vorschlag für eine SRAM-Zelle (gestrichelt umrandet), die aus zwei

gleichen Invertern mit einer der oben diskutierten Technologien aufgebaut ist. Tab. 1-1 zeigt

den Stromverbrauch als Funktion der Technologie und des logischen Zustands.

Tabelle 2.3.1-1: Stromverbrauch einer statischen SRAM-Zelle.

Technologie:

D='1'

D='0'

bipolar

100 nA

100 nA

NMOS

100 nA

100 nA

CMOS

0 μA

0 μA

Ein 128MB SRAM enthält 128·106 x 8 Bits ≈ 1048576 Bits. Tabelle 2.3.1-2 zeigt den

Stromverbrauch eines solchen 128MB SRAMs für die verschiedenen Technologien. Benötigt

jedes Bit 100nA Strom, dann ergibt sich ein Gesamtstromverbrauch von über 100A für die

bipolare und die NMOS-Technologie. Um diesen Strom in das Chip hereinzubringen dürfte

dessen Durchgangswiderstand nur 3V/100A=30mΩ betragen, was erhebliche Ansprüche an

die Leiterbahnen und Stecker stellen würde.

Tabelle 2.3.1-2: Stromverbrauch eines 128KB SRAMs.

Technologie:

Stromverbrauch:

bipolar

102,4 A

NMOS

102,4 A

CMOS

0A

Es sei angemerkt, dass dynamische RAM (DRAM) Zellen ihren Zustand nicht dauerhaft

halten können, sondern einen internen "Refresh" - Mechanismus benötigen, der die

Information von Zeit zu Zeit ausliest und wieder zurückschreibt. Die veraltete Bauweise

gemäß Bild 2.3.1-3(a) nutzt die Gate-Kapazität eines MOSFETs, um Ladung zu speichern

und kann ihre Information zerstörungsfrei auslesen. Sie verbraucht jedoch mehr Chip-Fläche,

als eine Kapazität, die man mit Hilfe eines geätzten Grabens in die Tiefe bauen kann. Eine

moderne DRAM-Zelle besteht im wesentlichen aus einer Kapazität, die so klein ist im

Vergleich zur Kapazität der Schreib-/Leseleitungen, dass man ihre Information gerade noch

auslesen kann.

(a)

Bild 2.3.1-3:

Dynamische RAM (DRAM) WD

Zellen:

(a) veraltete Version,

WA

(b) neue Version.

(b)

RA

M

RD

Data

Address

Isens

- SC / Seite 2-15 -

C

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.4 Berechnung der 3 Grundschaltungen des Bipolartransistors

2.4.1 Emitter-Schaltung mit Bipolartransistor

(a)

(b)

ICa

URc

2

UB

Q1

UB

RC

UC

2

(c)

VCC

VCC

1

ICa

Bild 2.4.1-1:

Q2

UBias

2

UC

Q1

ICa

UC

Q1

UB

1

0V

VCC

1

0V

0V

(a) Verstärkerstufe mit Bipolar-Transistor und idealer Stromquelle,

(b) Verstärkerstufe mit Bipolar-Transistor und Kollektor-Widerstand RC,

(c) Verstärkerstufe mit Bipolar-Transistor und aktiver Last Q2.

Gegeben: ICa=100μA, RC=25KΩ, Early-Spannung von Q1 und Q2: 2·VA1 = 3·VA2 = 200V,

uT=25mV. Gefragt sind nachfolgend Formel und Wert, wenn nichts anderes gefordert wird.

In allen drei Fällen in Bild 2.3.1(a-c) gilt Gm=ΔIC1/ΔUB [im Beispiel also 4mS].

Der Kollektor-Emitter-Widerstand rCE1 ist damit in Bild 2.3.1(a-c) rCE1=VA1/ICa [=1MΩ].

2.4.1.1 Emitter-Schaltung mit Lastwiderstand -> ∞ (Stromquelle):

Z2 = rCE1||∞ = rCE1 = 1/gCE1 [ 1MΩ]

Allgemein: -AV(gm,gCE) = gmZ2 = gm/gCE

[= 4mS/1μS = 4000]

Speziell bipolar:

-AV(VA1,uT) = gmZ2 = (IC/uT)/(IC/VA1) = VA1/uT [= 100V/25mV = 4000]

Typisch bipolar: Die Verstärkung ist (in erster Näherung) von IC . unabhängig!

2.4.1.2 Emitter-Schaltung mit endlichem Lastwiderstand und rCE -> ∞:

Z2 = rCE1 || RC -> RC

[=

Allgemein:

-AV(gm,RC) = gm Z2 = gm RC

25KΩ]

[= 4mS 25KΩ = 100]

- SC / Seite 2-16 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Verstärkung von der Basis zum Kollektor, speziell bipolar:

-AV,BC = gm RC = (IC/uT) (UR/IC) = URc/uT

[= 2,5V/25mV = 100]

Typisch bipolar: Die Verstärkung ist (in erster Näherung) von IC . unabhängig!

2.4.1.3 Emitter-Schaltung mit Lastwiderstand und rCE endlich:

Z2 = rCE1 || RC = RC rCE / (RC + rCE)

[ = RC·0,9756 = 24,39KΩ ]

Z2 = RC·F mit

F = 1/(1+gCE·RC) = 1/(1+(IC/VA1)·(URc/IC)) = 1/(1+URc/VA1)

[=0,9756 ]

Wichtig: Auch F ist keine Funktion von IC! Folglich:

-AV,BC = gm Z2 = (gm RC)·F = (URc/uT)·1/(1+URc/VA1)

[ = (2,5V/25mV)/(1+2,5V/100V) = 97,56]

Typisch bipolar: Die Verstärkung ist (in erster Näherung) von IC . unabhängig!

2.4.1.4 Emitter-Schaltung mit aktiver Last (typisch für integrierte Schaltungen)

gCE1 = ICa/VA1 = 100μA/100V = 1μS

[=1/1MΩ]

gCE2 = ICa/VA2 = 100μA·1,5/100V = 1,5μS [=1/666,7KΩ]

Z2 = 1/(gCE1+gCE2)= 1/(1μS + 1,5μS) = 400KΩ

Mit der effektiven Early-Spannung VA,eff = VA1||VA2 = 1/[(1/VA1)+(1/VA2)] [= 40V]:

Z2 = 1/(gCE1+gCE2) = 1/[(IC/VA1)+(IC/VA2)] = (VA1||VA2)/IC = VA,eff/IC

Wie groß ist die Spannungsverstärkung in Bild 2.3.1(c) als f(gm,Z2) und als Wert?

-AV,BC = gm·Z2 = 4mS 400KΩ = 1600

-AV,BC = gm·Z2 = (IC/uT) (VA,eff/IC) = VA,eff/uT [ = 40V/25mV=1600]

Typisch bipolar: Die Verstärkung ist (in erster Näherung) von IC . unabhängig!

- SC / Seite 2-17 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.4.2 Basis-Schaltung mit Bipolartransistor

Es gelten alle Verstärkergleichungen wie bei der

Emitterschaltung oben. Abweichungen:

VCC

URc

(1) Eingangsimpedanz ist rm (=1/gm) statt rBE=ß·rm.

(2) Verst. Vom Emitter zum Kollektor: AV,EC=-AV,BC > 0,.

ICa

RC

2

UB

Zin =>

Grund für (2): Die Spannungsdifferenz UBE=UB-UE steuert den

Kollektorstrom.

E-Schaltung: Änderung von UB um ΔUB: ΔUBE = ΔUB .

B-Schaltung: Änderung von UE um ΔUE: ΔUBE = -ΔUE .

UC

Q1

UE

2.4.3 Kollektor-Schaltung mit Bipolartransistor (Emitter-Folger)

(a)

(b)

(c)

VCC

UB

VCC

UB

Q

UBE

rm

UB

UE

RE

0V

UE

Zin=

ß(rm+RE)

RE

0V

UB

0V

Q1

UBE

Uout

UBias

Q2

0V

Bild 2.4.3: (a) Kollektor-Schaltung, (b) Kleinsignal-ESB, (c) mit Q2 als aktiver Last.

- SC / Seite 2-18 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.4.4 Variante der Emitter-Schaltung: mit Emitterwiderstand

Bild 2.4.4: Emitterwiderstand stabilisiert den

Temperaturgang auf Kosten der Verstärkung:

VCC

IC

RC

UC

UB

RC

R

r

AV

R

C

rm RE

RE

E

Q

m

UBE

UE

RE

IE

0V

AV

R U B

U C I C RC

R

( U E ) RC

I E C

E

U B

U B

U B

RE U B rm RE

RC

RC

U B RE rm RE

2.4.5 Variante der Emitter-Schaltung: Induktivität als Last

VCC

(a)

VCC

(b)

LC

RC

IL

UC

UB

D

IL

LC

UC

UB

Q

VCC

(c)

UC

UB

Q

Q

UC

UC

UC

VCC

UCa= VCC

UCa= VCC

UCa

0

UCE,sat

t

0

UCE,sat

t

0

t

Bild 2.4.5: E-Schaltung (a) mit RC, (b) mit LC, (c) mit LC u. Freilaufdiode zum Schutz von Q.

- SC / Seite 2-19 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.5 Berechnung der 3 Grundschaltungen des FETs

2.5.1 Source-Schaltung mit Feldeffekt-Transistor

(a)

(b)

IDa

UG

URD

UD

2

0V

Bild 2.5.1:

1

IDa

RD

2

UG

M1

1

(c)

VDD

VDD

VDD

UBias

2

UD

M1

UG

IDa

M2

1

0V

UD

M1

0V

(a) Verstärkerstufe mit MOSFET und idealer Stromquelle,

(b) Verstärkerstufe mit MOSFET und Drain-Widerstand RD,

(c) Verstärkerstufe mit MOSFET und aktiver Last M2.

Gegeben: IDa=100μA, RD=25KΩ, ß=400μA/V2; Daten für M1: λ1=0,01/V, VT1=0,7V, ß1=ß;

Daten für M2: λ2=0,015/V, VT2=-0,7V, ß2=ß. (Verwenden Sie das Modell g m 2 I Da .)

Zeigen Sie, dass für den Übertragungsleitwert der Stufe in Bild 1.1(a-c) gilt: Gm ≈ 400μS.

(2P)

Gm = gm1 = g m 2 I D 2 4 10 4 AV 2 10 4 A 2 4 10 8 A 2 / V 2 = 400μS

Zeigen Sie, dass für den Drain-Source-Widerstand rDS1 in Bild 1.1(a-c) rDS1=1MΩ gilt.

(2P)

rDS1 = 1/gDS1 1/(λ1IDa) = 1/{(10-2/V)·(10-4A)} = 1/1μS = 1MΩ

2.5.1.1 Source-Schaltung mit Lastwiderstand -> ∞ (Stromquelle):

Wie groß ist die Impedanz Z2 des Ausgangsknotens in Bild 1.1(a) als f(rDS) und Wert?

(2P)

Z2 = rDS1 = 1MΩ

Wie groß ist die Spannungs-Verstärkung der Stufe in Bild 1.1(a) als f(gm,rDS) und als Wert?

(Hinweis: Wenn sie hier ein Problem haben, machen Sie zuerst Aufgabe 1.5)

(2P)

-AV = gmZ2 = gm/gDS = 400μS/1μS = 400

Wie groß ist die Spannungs-Verstärkung der Transistorstufe in Bild 1.1(a) als f(ß,λ1,IDa)?

- SC / Seite 2-20 -

(1P)

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

-AV = gm/gDS = 2 I Da /(λ1IDa) = 2 /(λ1 I Da ) [=0.04/(0.012)=400]

Mit welchem Exponenten geht IDa in diese Formel ein? ......-0,5.............

(1P)

2.5.1.2 Source-Schaltung mit endlichem Lastwiderstand und rDS -> ∞:

Wie groß ist die Ausgangsimpedanz Z2 in Bild 1.1(b) für rDS -> ∞ als f(RD) und Wert?

(2P)

Z2 = rDS1 || RD -> RD = 25KΩ

Wie groß ist die Spannungs-Verstärkung in Bild 1.1(b) für rDS -> ∞ als f(gm,RD) und Wert?

(2P)

-AV = gm Z2 = gm RD = 0,4mS 25KΩ = 10

Wie groß ist die Spannungs-Verstärkung der Schaltung in Bild 1.1(b) für rDS -> ∞ als

f(URDa,ß,IDa)? (Hinweis: URD≈URDa=IDaRD.)

-AV = gm RD = 2 I Da ·(URD/IDa) = 2URDa

I Da

[=2·2,5V

(2P)

400 A / V 2

=10]

100 A

Mit welchem Exponenten geht IDa in diese Formel ein? ......-0,5.............

(1P)

2.5.1.3 Source-Schaltung mit Lastwiderstand und rDS endlich:

Wie groß ist die Ausgangsimpedanz Z2 in Bild 1.1(b) für endliche rDS als f(rDS,RD)?

Z2 = rDS1 || RD = RD rDS / (RD + rDS)

[ = RD·0,9756 = 24,39KΩ ]

Stellen Sie die Ausgangsimpedanz Z2 in Bild 1.1(b) als Z2=RD·F dar und geben Sie die

Formel für den Faktor als F = f(RD,gDS) an. (Nur Formel)

Z2 = RD·F

mit

(1P)

(1P)

F = rDS / (RD + rDS) = 1/(1+gDS·RD)

Geben Sie die Formel für den Faktor F an als Funktion von URD und λ1 (mit URD≈IDaRD).

(1P)

F = 1/(1+gDS·RD) = 1/ (1+{(λ1ID)·(URD/ID)} = 1/(1+λ1URDa)

[ = 0,9756 ]

Wie groß ist die Spannungs-Verstärkung in Bild 1.1(b) für endliche rDS als f(ß,URD, λ1,IDa)?

(Formel und Wert, je 1P)

- SC / Seite 2-21 -

(2P)

Prof. Dr. M. Schubert

Skript Schaltungstechnik

-AV = gmZ2 = gmRDF = 2 I Da

U RDa

2U RDa

/(1+ λ1URDa) =

I Da

1 1U RDa

-AV =

2 2,5V

1 0,01V 1 2,5V

400 A / V 2

100 A

Hochschule Regensburg

I Da

= 4,878V-1 2V = 9,756

Mit welchem Exponenten geht IDa in diese Formel ein? ......-0,5.............

(1P)

2.5.1.4 Source-Schaltung mit aktiver Last (typisch für integrierte Schaltungen)

Wie groß sind gDS1 und gDS2 in Bild 1.1(c) als f(λi,IDa) und Wert?

gDS1 = λ1 IDa = 0,01V-1 100μA = 1μS

(2P)

[=1/1MΩ]

gDS2 = λ2 IDa = 0,015V-1 100μA = 1,5μS [=1/666,7KΩ]

Wie groß ist die Ausgangsimpedanz Z2 in Bild 1.1(c) als f(gDS1,gDS2) und als Wert?

(2P)

Z2 = 1/(gDS1+gDS2)= 1/(1μS + 1,5μS) = 400KΩ

Zeigen Sie, dass die Ausgangsimpedanz in Bild 1.1(c) als Z2=1/((λ1+λ2)ID) darstellbar ist.

(1P)

Z2 = 1/(gDS1+gDS2)= 1/[(λ1ID)+(λ2ID)] = 1/(λ1+λ2)ID

Wie groß ist die Spannungsverstärkung in Bild 1.1(c) als f(gm,Z2) und als Wert?

(2P)

-AV = gm·Z2 = 0,4mS 400KΩ = 160

Wie groß ist die Spannungsverstärkung in Bild 1.1(c) als f(ß,λ1+λ2,IDa)?

-AV = gm·Z2

2 I Da

2

=

=

1 2

(1 2 ) I Da

I Da

(1P)

2V

400 A / V 2

[ =

= 160]

0,01 0,015

100 A

Mit welchem Exponenten geht IDa in diese Formel ein? ......-0,5.............

- SC / Seite 2-22 -

(1P)

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.5.2 Gate-Schaltung mit Feldeffekt-Transistor

(a)

(b)

IDa

UG

URD

UD

2

RD

2

M1

IDa

UD

M1

UG

1

(c)

VDD

VDD

1

IDa+iD

Zin

VDD

M3

M2

R

2

IDa

UD

M1

UG

1

IDa+iD Zin

IDa+iD Z

in

Bild 2.5.2: MOSFET als Verstärker in Gate-Schaltung

Gegeben: IDa=100μA, RD=25KΩ, ß=400μA/V2; Daten für M1: λ1=0,01/V, VT1=0,7V, ß1=ß;

Daten für M2: λ2=0,015/V, VT2=-0,7V, ß2=ß. (Wir verwenden das Modell g m 2 I Da .)

Bild 2.5.2 zeigen MOSFETs als Verstärker in Gate-Schaltung. Man beachte die Ähnlichkeit

zu Bild 2.5.1 mit MOSFETs in Source-Schaltung. Die Schaltungstechnik um die DrainElektrode ist für die Bilder 2.5.2 und 2.5.1 identisch und somit sind auch die Ausgangsimpedanzen Z2 identisch. Da auch die Übertragungsleitwerte gleich sind, liefern die Bilder

2.5.1 und 2.5.2 gleiche betragsmäßige Verstärkung. Allerdings liefert die Gate-Schaltung

positive und die Source-Schaltung negative Verstärkung. Zum Verständnis der betragsmäßig

gleich großen Verstärkungen wie auch der Vorzeichenumkehr mache man sich klar, dass die

Source-Schaltung im Prinzip mit uGS gesteuert wird und die Gate-Schaltung mit uSG=-uGS.

Erhebliche Unterschiede zwischen Gate- und Source-Schaltung ergeben sich für die resistiven

Kleinsignal-Eingangsimpedanzen. Für die Source-Schaltung hatten wir resistive KleinsignalEingangsimpedanzen von Zin , also leistungslose Steuerung. Die Gate-Schaltung

steuern wir mit der Source-Elektrode und erhalten mit rm1=1/gm1 und AV,max1=gm1·rDS1

für Bild 2.5.2(a) Zin = rm1 + /AV,max1 = , für Bild 2.5.2(b) Zin = rm1 + RD/AV,max1, für

Bild 2.5.2(c) Zin = rm1 + rDS2/AV,max1.

2.5.3 Drain-Schaltung mit Feldeffekt-Transistor (Source-Folger)

VDD

u1

G

gnd

D

S

u2

RS

Bild 2.5.3: FET

in S-Schaltung

Mit der gleichen Argumentation wie für den Bipolartransistor

ergibt sich für den FET als Source-Folger die Verstärkung

RS

AV Gm Z 2 g m ( RS || rm )

,

rm RS

die man als Kleinsignal-Spannungsteiler ansehen kann bestehend

aus RS und dem Ausgangswiderstand des FETs, also rm=1/gm.

- SC / Seite 2-23 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6 Strom- und Spannungsquellen

Ip1

UCC

Ip3

Q7

Ip4

Q1

Uinn

Q2

Uinp

UCC

U2

Q5

Q3

U3

Q6

Ip2

UEE

Uout

Up2

Cm

R1

Q4

Up1

Q8

UEE

Ip5

UEE

Bild 2.6: Verstärker ohne Biasing Circuit.

Bild2.6 zeigt einen Verstärker, den wir im Kapitel über „Verstärker für differentielle Signale“

genauer betrachten werden. Hier sei nur auf die Stromquellen Ip1 ... Ip5 und Spannungsquellen

Up1=UBE7 und Up2=|UBE8| hingewiesen, welche in der Schaltung zur Vorspannungserzeugung

(engl. biasing circuit) realisiert werden müssen. Oft ist die Vorspannungserzeugung

komplexer, als der Verstärker selbst.

2.6.1 Stromquellen

2.6.1.1 Widerstand als Stromquelle

Rp1

Rp für Ip

Rp für Ip

Rp3

Rp4

Q1

Uinn

Q2

U2

Q5

UEE

Q4

Q7

Uinp

UCC

Q3

UCC

U3

Cm

R1

Rp2

Up1

Uout

Up2

Q6

UEE

Q8

Rp5

Bild 2.6.1.1: Stromquellen Ip1...Ip5 mit Widerständen Rp1...Rp5 realisiert.

- SC / Seite 2-24 -

UEE

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Der Strom durch einen Widerstand ergibt sich nach Ohm zu I = U / R. In Bild 2.6.1.1

wurden die Stromquellen Ip1...Ip5 in Bild 2.6 mit Hilfe der Widerstände Rp1...Rp5 realisiert.

Stromquellen mit Widerständen zu realisieren ergibt schlechte Verstärkereigenschaften und

ist nur bei diskreter Bauweise billiger, als Stromquellen mit Transistoren zu realisieren.

2.6.1.2 Induktivität als Stromquelle

Bild 2.6.1.2: Die Induktivität „wehrt“ sich

gegen eine Stromänderung: ΔIL=UL/L. Je

größer die Induktivität, um so kleiner ΔIL.

L

IL

UL

Die Induktivität erwärmt sich nicht durch Stromfluss, wie es bei einem Transistor oder

Widerstand zur Abwärtsregelung der Fall wäre. (Aufwärtsregelung auf U2>U1 so unmöglich.)

Impedanz der Induktivität für sinusförmige Ströme: ZL=jωL.

Die Änderungsgeschwindigkeit von IL ist dIL/dt=UL/L.

Die in der Induktivität gespeicherte Energie berechnet ist EL=½LI2.

2.6.1.3 Transistor als Stromquelle

(a)

IR

(b)

UR

(d)

IC

(c)

UCE

ID

UDS

IC, ID

0

-VA, -1/

UCE, UDS

Bild 2.6.1.3: (a) Widerstand ersetzt durch (b) Bipolar- und (c) Feldeffekt-Transistor,

(d) Transistor-Kennlinie

Der Kleinsignalwiderstand eines Bipolartransistors berechnet sich zu rCE=(UCE+VA)/IC. Um

diesen Kleinsignalwiderstand durch einen gleich großen Widerstand R=rCE bei bleichem

Strom IR=IC zu ersetzen, benötigen wir über dem Widerstand die Spannung UR=UCE+VA.

Der Kleinsignalwiderstand eines Feldeffekt-Transistors berechnet sich zu rDS=(UDS+1/)/ID.

Um diesen Kleinsignalwiderstand durch einen gleich großen Widerstand R=rDS bei bleichem

Strom IR=ID zu ersetzen, benötigen wir über dem Widerstand die Spannung UR=UDS+1/.

- SC / Seite 2-25 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Transistoren mit VA=150V oder λ=1/150V können also in einer 3,3V-Technologie Stromquellen realisieren, für die wir sonst zusätzlichen Hilfsspannungen von 150V bereitstellen

müssten. Das wäre nicht nur technisch aufwendig, sondern würde auch zusätzlichen Aufwand

zum Personenschutz beim Umgang mit hohen Spannungen nach sich ziehen.

2.6.1.4 Selbstleitender FET als Stromquelle

(a)

Ip

(b)

(c)

ID

ID

UDS

UDS

ID

(d)

UDS,sat

0

-1/

-VT

UDS

Bild 2.6.1.4: (a) Stromquelle, ersetzt durch (b) JFET- oder (c) MOSFET, (d) FET-Kennlinie.

Es ist eine verbreitete Technik Stromquellen durch selbstleitende FETs gemäß obigem Bild

zu realisieren.

Die Schwellenspannung eines selbstleitenden n-Kanal-FETs ist VT<0.

Sättigungsspannung: UDS,sat = UGS –VT, hier also UDS,sat = 0–VT = -VT = |VT|.

Wir betrachten den Fall des FETs für die oben dargestellte Situation UGS=0:

(1) Für UDS<0V handelt es sich in Bildteil (b) um eine in Vorwärtsrichtung betriebene Diode.

(2) Für 0 ≤ UDS < UDS,sat=|VT| gilt I D 2 ß (| VT | 0.5U DS )U DS (1 U DS )

(3) Für UDS > UDS,sat=|VT| gilt I D ßVT2 (1 U DS )

Um den selbstleitenden N-FET bei UGS=0 als Stromquelle zu betreiben muss UDS > -VT=|VT|

sein, da der FET sonst nicht in Sättigung arbeitet. (Erinnerung: UDSsat=UGS-VT=0-VT=-VT.)

Was passiert, wenn man in Bildteil (c) einen selbstsperrenden FET (i.e. VT>0) verwendet?

- SC / Seite 2-26 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.1.5 Einfache Stromspiegel mit MOSFETs (Quellen und Senken)

VDD

Iin

Io,1

Io,2

Io,3

Io,N

Iin

Io,1

Io,2

Io,3

VSS

Io,4

Io,5

VSS

Bild 2.6.1.5: (a) Stromsenken Io,x=Iin , (b) Stromsenken Io,1=Io,2=Iin, Stromquellen

Io,3=Io,4=Io,5=Iin.

2.6.1.6 Einfache Stromspiegel mit Biopolartransistoren

Iin = IC,0+(N+1)IB = IC,0+(N+1)IC,x/ß = IC,x(1+(N+1)/ß)

(a)

Iin

Io,1

Io,2

=>

Io,3

IC,x = Iin / (1 + (N+1)/ß)

Io,N

Q0

VEE

(b)

VCC

Iin

Io,1

Io,2

Io,3

Io,4

Io,5

Q0

VEE

Bild 2.6.1.6: (a) Stromsenken Io,x, (b) Stromsenken Io,1=Io,2, Stromquellen Io,3=Io,4=Io,5.

- SC / Seite 2-27 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.1.7 Verringerung des Basisstromfehlers beim bipolaren Stromspiegel

Bild 2.6.1.7:

Verringerung des

Basisstrom-Fehlers

durch Einfügen des

Puffer-Transostors

QB.

Iin

Io,1

Io,2

Io,3

Io,N

VCC

QB

Q0

VEE

Iin = IC,0+[(N+1)IB] / ß = IC,0+[(N+1) IC,x/ß ] / ß = IC,0+(N+1)IC,x/ß2 = IC,x(1+(N+1)/ß2)

IC,x = Iin / (1 + (N+1)/ß2),

Der Fehlerterm ist von (N+1)/ß um den Faktor ß auf (N+1)/ß2 geschrumpft.

2.6.1.8 Stromquellen mit Source- / Emitter-Widerständen

Bildteil (a): Der FET mit Source-Widerstand hat eine Ausgangsimpedanz von

Z out rDS1

g m1

U U GS 1

R2 und einen Ausgangsstrom von I out B

g DS1

R2

Bildteil (b): Der Bipolartransistor (engl. biploar junction transistor, BJT) mit EmitterWiderstand hat eine Ausgangsimpedanz von

Z out rCE1

rm1 R2

U U BE1

und einen Ausgangsstrom von I out B

rm1 R2 / ß1

R2

Bildteil (c) zeigt eine Realisierung der Schaltung (b) im Operationsverstärker TL08x. Es ist

Iout=(UB–UBE)/R10. mit UBE≈0,7V.

(a)

Zout

Iout

Bild 2.6.1.8:

(a) FET mit SourceWiderstand

(b) BJT mit EmitterWiderstand

UB

M1

(c) Realisierung im

TL08x.

(b)

Zout

UB

R2

VSS

(c)

Iout

Q1

Iout

- SC / Seite 2-28 -

UB

Q10

D2

R2

VEE

IB

VEE

R10

TL08x

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.1.9 Kaskadierter Stromspiegel mit MOSFETs und Bipolartransistoren

Der kaskadierte Stromspiegel mit FETs in Bildteil (a) unten hat eine Ausgangsimpedanz von

Z out rDS1

g m1

rDS 2 und einen Ausgangsstrom von I out I in

g DS1

Der kaskadierte Sptromspiegel mit BJTs in Bildteil (b) unten hat eine Ausgangsimpedanz von

Z out rCE1

rm1 rCE 2

und einen Ausgangsstrom von I out I in 2 I B

rm1 rCE 2 / ß1

Die Ausgangsimpedanz ist wesentlich höher als bei den nicht kaskadierten Spiegeln, aber die

minimale Ausgangsspannung liegt höher über VSS.

(a)

Bild 2.1.1.9:

(a) Kaskadierter Stromspiegel mit FETs

(b) Kaskadierter Stromspiegel mit BJTs

Zin

Iin

(b)

Zout

UB1

M4

Iout

Zin

M1

Q4

M2

Q3

UB1

UB2

M3

Zout

Iin

Iout

Q1

UB2

Q2

VSS

VEE

2.6.1.10 Wilson Stromspiegel mit MOSFETS und Bipolartransistoren

Wilson-Spiegel haben die höchsten Zout, sind aber schlechter über der Frequenzachse.

(a)

Bild 2.1.1.10:

(c) Wilson-Stromspiegel

mit FETs

(d) Wilson-Stromspiegel

mit BJTs

Zin

(b)

Zout

Iin

Iout

Zin

Zout

Iin

M1

Q1

Ufb

M3

Iout

Ufb

M2

VSS

- SC / Seite 2-29 -

Q3

Q2

VEE

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.1.11 Stromspiegel mit Schwellenstrom

(a)

(b)

IT

Zin

Iin

Zout

Iout

Iout

t

I ou

I ou

M3

M4

M1

M2

VSS

0

0

IT

t,T

Iin

Bild 2.6.1.11: (a) Schaltkung, (b) Kennlinie.

Ohne die in Bildteil (a) blau eingezeichneten Transistoren M3, M4 ergibt sich ein einfacher

Stromspiegel mit der in Bildteil (b) dargestellten Kennlinie. Durch einfügen der blau

gezeichneten Schaltung mit den Transistoren M3, M4 in Bildteil (a) bekommen wir die blau

gezeichnete Kennlinie in Bildteil (b), welche Ausgangsstrom Iout nur für Iin≥IT liefert.

2.6.1.12 Stromspiegel mit Iout ≠ Iin: Mehrfache Verwendung einer Transistor-Basiszelle

Der Drainstrom eines FETS verhält sich theoretisch gemäß W/L, wobei W die Breite und L

die Länge des Kanals unter dem Gate ist. Genaue Einstellungen sind so aber nicht möglich, da

sich Randeffekte an den Rändern des Kanals und die Stromverteilung um die Kontakte nicht

einfach mit W/L skalieren lassen. Daher erstellt man eine Einheitszelle eine Transistors und

verwendet diese mehrfach.

Ist das Spiegelverhältnis eine rationale Zahl gemäß Iout / Iin = M / N mit den ganzen Zahlen

M/N, dann benötigt man M+N Transistoren, wenn sich M/N nicht weiter kürzen lässt. Man

legt dann M Transistoren für Iout und N für Iin parallel, wie im Bild für Iout/Iin=M/N=5/4

gezeigt.

Reelle Zahlen müssen gerundet und dann auf ein an der zu erreichenden Genauigkeit

orientiertes Maß gekürzt werden: Beispiel: π = 3,141592... ≈ 3,14 = 314/100 = 157/50. In

diesem Fall bräuchte man also 207 Transistoren.

Bei der Fertigung dieser Transistorhaufen ist darauf zu achten, dass aus vielen

Transistorzellen zusammengesetzten Transistoren gut vermischt umd um ein gemeinsames

geometrisches Zentrum symmetrisch verteilt werden. Dann treffen Veränderungen im Kristall

oder Temperaturänderungen, die von einer bestimmten Seite kommen, Ein- und Ausgang des

Stromspiegels gleichermaßen, so dass das Matching weitgehend erhalten bleibt.

- SC / Seite 2-30 -

Prof. Dr. M. Schubert

(a)

Skript Schaltungstechnik

Hochschule Regensburg

Iin

M12

M11

M13

Iout = (5/4) Iin

M14

M21

M22

M23

M24

M25

VSS

(b)

M23

M12

M24

M11

M22

M21

M14

M13

M25

Bild 2.6.1.12: (a) Stromspiegel mit Spiegelverhältnis 1:1,25, (b) geometrische Verteilung

2.6.1.13 Ausnutzen der unendlichen Impedanz einer idealen Stromquelle

(a)

(b)

(c)

VDD

IDa

UD

2

UG

1

M1

0V

IDa

IDa

0V

UD

2

UG

1

M1

0V

UD

2

UG

1

M1

0V

Bild 2.6.1.10: Stromquelle mit positivem Pol an (a) VDD, (b) Masse und (c) unbekannt.

Der Innenwiderstand einer idealen Stromquelle ist unendlich. Die Schaltungen in Bildteil

(a) und (b) verhalten sich identisch. Es ist also egal, wo der zweite Anschluss einer idealen

Stromquelle liegt, da ihr Innenwiderstand unendlich ist. Daher zeichnet man sie auch häufig

ohne Anschluss des zweiten Pols wie in Bildteil (c).

- SC / Seite 2-31 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.2 Treibende Spannungsquellen

2.6.2.1 Batterie als treibende Spannungsquelle

Eine Batterie kann im einfachsten Falle als Spannungsquelle oder große Kapazität mit

Innenwiderstand modelliert werden. Gute Batteriemodelle - speziell von Lithium-basierten

Batterien - sind allerdings eine komplizierte Angelegenheit.

2.6.2.2 Widerstand, Diode, Zenerdiode als treibende Spannungsquellen

2.6.2.3 Geschaltete Kapazitäten als treibende Spannungsquelle

(a)

(b)

1

(c)

2

R

U1

C

U2

C2

U1

C

U2

C2

U1

U2

C2

Bild 2.6.2.2: (a) C lädt an U1, (b) C lädt um auf U2, C2, (c) äquivalenter Widerstand u.

Quelle.

Q1 = CU1.

Die Kapazität C enthält in Bildteil (a) die Ladung

Die Kapazität C enthält in Bildteil (b) die Ladung

Q2 = CU2.

Die Kapazität C transportiert mit jedem Schaltzyklus je nach Polung die Ladung

Q = C(U1-U2).

.

Die Kapazität C transportiert bei f Schaltzyklen pro Sekunde den mittleren Strom

Im = fs·Q = = fsC(U1-U2).

Die geschaltete Kapazität entspricht somit einer Spannungsquelle UB mit Innenwiderstand

Requiv=1/fC.

- SC / Seite 2-32 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.2.4 Bipolartransistor mit 2 Widerständen als treibende Spannungsquelle

2.6.2.5 Geschachtelte Bipolartransistoren als treibende Spannungsquelle

Der Ausschnitt aus dem TL081 von Texas Instruments

zeigt auf der linken Seite oben und unten je einen

Transistor als Stromquelle (A) und –senke (B), welche

die treibende Spannungsquelle (C) aus zwei

verschachtelten Transistoren unter Strom halten. Sinn der

Spannungsquelle ist es die Vorspannung für die

Endstufentransistoren (D) zu erzeugen, die gegen zu viel

Vorspannung (z.B. durch Fertigungstoleranzen) und

Überstrom (z.B. durch Kurzschluss am Ausgang) mit je

einem 64-Widerstand vor dem Emitter geschützt sind.

A

D

C

B

Ausschnitt aus dem TL081

- SC / Seite 2-33 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.3 DC/DC-Wandler

Bild 2.6.3-1:

DC/DC-Wandler-Prinzipien:

(a) Aufwärts-W. (Boost-Conv.)

(b) Abwärts-W. (Buck- Conv.)

(c) Spannungsumkehrer

(b)

2,68

2,79

3,05

3,16

3,27

3,42

3,76

3,95

3,77

3,99

4,47

4,88

(c)

High-Current-LED, white

UF,min / V UF,typ / V UF,max / V

6

5

forward voltage

LEDStrom/A

0,2

0,35

0,7

1

(a)

Bild 2.6.3-2: Vorwärtsspannungen einer

weißen Hochstrom-LED für automotive

Anwendungen aus [4].

4

UF,min / V

3

UF,typ / V

UF,max / V

2

1

0

0,2

0,35

0,7

1

current

DC/DC-Wandler mit Induktivitäten berechnet man für die Annahme eines im Mittel

konstanten Laststromes. Hierfür sind Licht emittierende Dioden (LEDs) ein gutes Beispiel, da

ihre Helligkeit stromgesteuert ist.

Bild 2.6.3-3 zeigt typische LED-Schaltungen.

Der Widerstand als Stromquelle in Bildteil (a) ist

extrem anfällig für schwankende Versorgungsspannungen. Die Stromquelle in Bildteil (b) ist hochohmiger aber genauso ineffizient.

und

UF=3V.

Die

Beispiel:

VCC=12V

Leistungsaufnahme der Stromquelle ist bei

gleichen Diodenstrom ((VCC-UF)/UF)2 (hier neun

mal) höher als die der Leuchtdiode.

(a)

(b)

VCC

VCC

R

R

UF

UF

Bild 2.6.3-3: Typische LED-Schaltungen

- SC / Seite 2-34 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.3.1 Tiefsetzsteller bzw. Abwärtswandler (engl.: Buck , Step-Down Converter)

2.6.3.1.1 Mit Längsregler und Wärmeverlusten: PV = Pin - Pout

(a)

(b)

Udo

Ui

(c)

Udo

Uo

Ui

(d)

Udo

Uo

Ui

Uo

Q2

Q1

Q1

Us

Ui

Uo

Udo

Udo

Ui

Uo

Ui

Uo

Q2

Q1

Q1

Q1

Us

(f)

Q2

Q2

Q1

Us

(e)

Udo

Us

Us

Us

Bild 2.6.3.1.1: Bipolare Leistungsschalter eines Reglers für konstante Ausgangsspannung Uo.

Übung 1: Benennen sie die 6 Leistungsschalter in den oben dargestellten Bildteilen (a)-(f).

(a) ..........................

(b) ..........................

(c) ..........................

(d) ..........................

(e) ..........................

(f) ..........................

Übung 2: Wie groß in Volt ist Udo mindestens für UCE,sat=0,3V, UBE=0,7V, Uis=Ui-Us≥0,3V?

(a) ..........................

(b) ..........................

(c) ..........................

(d) ..........................

(e) ..........................

(f) ..........................

Lösungen zu Übung 1:

(a)

(c)

(e)

npn Bipolartransitor

npn Darlington-Transistor

npn Pseudodarlington-Transistor

(b)

(d)

(f)

pnp Bipolartransitor

pnp Darlington-Transistor

pnp Pseudodarlington-Transistor

Lösungen zu Übung 2:

(a) Udo,min = Uis + UBE1 ≥ 0,3V + 0,7V = 1V

(b) Udo,min = UCE,sat1 = 0,3V

(c) Udo,min = Uis + UBE1 + UBE2=,3+,7+,7 =1,7V (d) Udo,min = UBE2 + UCE,sat1 ≥ 0,7V+0,3V = 1V

(e) Udo,min = Uis + UBE1 = 0,3V + 0,7V = 1V

(f) Udo,min = UCE,sat1 + UBE2 =,3V+0,7V = 1V

- SC / Seite 2-35 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.3.1.2 Mit ausgeglichener Leistungsbilanz: Pin = Pout

(a)

(b)

UL,a

IL

U

Sa 1

I1

L

U1

Sb

U2

I1

R IR U 1

C

UL,b

IL

U1

Sa

Sb

L

C

(c)

U2

R

IL,max

Ib

Ia

Ia

Ib

IL

(f)

'1'

Rsense

U1

'0'

Tb

Ta

(d)

IL,min

t

0

IR

Usense

(e)

IL

U1

IL,max

IL

I1

t

0

Rsense

Usense

IL,min

0

Bild 2.6.3.1.2 DC/DC-Konverter: Der Schalter Sa ist im periodischen Wechsel jeweils (a) für

die Zeitspanne Ta ideal leitend und (b) für die Zeitspanne Tb eine Unterbrechung. Sb

arbeitet exakt gegensinnig zu Sa. Es sei Ux=konstant (x=1,2) und Duty-Cycle:=

D=Ta/(Ta+Tb).

Wandlertypen, die Energie in einer Induktivität zwischenspeichern und mit einem anderen

Verhältnis von Spannung und Strom wieder abgeben haben einen theoretischen

Wirkungsgrad von 100%. In der Praxis werden 90% gut erreicht, 94...96% sind schwierig.

Das Bild oben zeigt einen DC/DC-Abwärtswandler.

(a) In Bildteil (a) wird die Induktivität L geladen. Es ist zu beachten, dass die Ladezeit

begrenzt werden muss, weil der Strom sonst – rein theoretisch für konstante U1, U2 –

ins unendliche wächst.

(b) In Bildteil (b) entlädt Induktivität L ihre Energie an den Sekundärkreis.

(c) In Bildteil (c) wird ebenfalls die Induktivität L geladen, und

(d) in Bildteil (d) über die LEDs entladen.

(e) Bildteil (e) illustriert den Strom durch die Induktivität L. er muss stetig sein.

(f) Bildteil (f) zeigt den Strom durch die Spannungsquelle U1. Er weist Stromsprünge

auf, welche ihn für viele Anwendungen ausschließen. Eine Autobatterie z.B. darf mit

derart hohen Frequenzanteilen dieser Energie nicht konfrontiert werden.

Der DC-Strom durch die Induktivität L kann sehr hoch werden. Alle von diesem Strom

durchflossenen Leiterbahnen müssen darauf ausgelegt sein. Der mittlere Strom beträgt

IL,mitt =

½ (IL,max+ IL,min)

Die Spannung UL,b entlädt L während des Intervalls Tb:

UL,b = UL(Ta<tTb) =

0 – U2 = –U2

- SC / Seite 2-36 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Die Induktivität L gibt an den Sekundärkreis die mittlere Leistung P2,mitt ab:

P2,mitt =

U2 IL,mitt

Die Energie in der Induktivität L wird mit der Spannung UL,a geladen:

UL,a = UL(0<tTa) =

U1 – U 2

Die Spannungsquelle U1 liefert dabei den mittleren Strom

I1,mitt =

IL,mitt D

Dabei gibt die Quelle U1 die mittlere Leistung P1,mitt ab:

P1,mitt =

U1 I1,mitt = U1 IL,mitt D

Das Verhältnis U2/U1 als Funktion des Duty-Cycles:

dI

Ia L

dt

dI

, Ib L

dt

= (U1–U2)/L

0 t Ta

= (-U2)/L

Ta t Tb

Wenn der Strom im eingeschwungenen Zustand periodisch schwankt, dann gilt Ta Ia +Tb Ib =0.

Folglich ist 0=Ta I +Tb I =Ta(U1-U2)/L+Tb(-U2)/L=0 => 0=Ta(U1-U2)-TbU2 =>

a

b

TaU1–(Ta+Tb)U2 Ta =>

U2 = U1 Ta/(Ta+Tb) = U1D

Die Wirkleistung PL,mitt=P1,mitt-P2,mitt, welche die Induktivität L erwärmt ist somit 0, da Blindleistung nicht in Wärme umgesetzt sondern gespeichert und wieder abgegeben wird:

PL,mitt = U1DIL,mitt – U2IL,mitt = U2IL,mitt – U2IL,mitt = 0.

Schalter Sb wird in der Praxis häufig durch eine Diode ersetzt, welche die mittlere Leistung

UDIL,mitt verbraucht. Bei kleinen Spannungen U2 kann das einen erheblichen Anteil der

Gesamtleistung ausmachen. Daher sind hier Schottky-Dioden (Metall-n- statt pn-Übergang)

zu empfehlen. Sie sind sehr schnell und haben nur ca. 0,4V Durchlassspannung.

Bildteil (a):

L lädt Energie.

Bildteil(b): L

entlädt Energie.

(a)

U1

S

U1

D

UL

L

(b)

IL

U2

U1

S

C

R IR U 1

- SC / Seite 2-37 -

D

UL

L

IL

C

U2

R

IR

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.3.2 Hochsetzsteller bzw. Aufwärtswandler (engl.: Step-Up , Boost Converter)

(a)

Bild 2.6.3.2:

Aufwärtswandler:

(a) IL laden

(b) IL abgeben + U1

puffern auf C

(c) Stromverlauf

für konstanten

Lastrom und (c)

konstante

Spannungen

U1, U2.

L

(b)

U2

IL

UL

U2

IR

C

U1

IL

C

IR

IL

IL

T1

0

T2

t

T

Spannungskonversion:

Stromänderung beim Aufladen von L im Intervall T1:

ΔIL1 = T1 IL1 = T1 (U1–0V) / L .

Stromänderung beim Entladen von L im Intervall T2:

ΔIL2 = T2 IL 2 = T2 (U1–U2) / L

Im eingeschwungenen Zustand ergibt sich ΔIL1+ΔIL2 =0 => U2 = U1 T/T2 mit T=T1+T2.

Als f(D) mit D=T1/T: Die Spannungserhöhung U2/U1 hängt im eingeschwungenen Zustand

bei konstantem, mittlerem Laststrom IR nur vom Tastverhältnis (Duty-Cycle) D=T1/(T1+T2)

ab. In diesem Falle ist wegen T2/T=(T-T1)/T=(1-D) die Ausgangsspannung U2=U1/(1-D).

Leistungsbilanz:

Die ideale Induktivität (Kupferwiderstand des Drahtes = 0Ω) erwärmt sich nicht, so dass die

von U1 eingespeiste Leistung gleich der an U2 abgegebenen Leistung sein muss:

Der von U1 abgegebene, mittlere Strom ist Im1 = I0+½IL.

Der von U2 aufgenommene, mittlere Strom ist Im2 = (I0+½IL)T2/T.

Die von U1 abgegebene, mittlere Leistung ist Pm1 = U1Im1 = U1 (I0+½IL)

Die von U2 aufgenommene, mittlere Leistung ist Pm2 = U2Im2 = U1 T/T2 (I0+½IL)T2/T = Pm1.

Anmerkungen:

Der Aufwärtswandler setzt voraus, dass U2>U1, sonst wird IL stetig größer und kann zur

Zerstörung von Bauelementen führen. (Darf die Last eine einzelne LED sein bei U1=12V?)

Für Low-Power-Anwendungen (z.B. "handheld Devices" wie Walkman, Handy), in denen

die Leistungsaufnahme der Diode mit Udiode=0,7V zu hoch ist, werden MOSFETs als

Schalter eingesetzt (, deren ON/OFF-Timing dann allerdings stimmen muss).

Die von der Quelle zu verkraftenden Stromänderungen sind im Vergleich zum

Abwärtswandler moderat. => Emission verkraftbarer Störungen in die (Auto-)Batterie!

- SC / Seite 2-38 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.6.3.3 Kombinierte Aufwärts-/Abwärts-Wandler

Bild 2.6.3.3: Kombinierter

Aufwärts-/Abwärts-Wandler

nach [3].

U1

Rsense

Beim kombinierten Aufwärts-/Abwärts-Wandler verhindert der Aufwärtswandler eine

Belastung der Quelle U1 mit extremen Stromsprüngen. Der Abwärtswandler passt den

Ausgangsstrom an die Last an [3].

2.6.3.4 Wandler mit Vorzeichenumkehr

(a)

Sa

Sb

U1

I1

IL

UL

U1

gnd

(b)

U2

U1

I1

U2

IR

C

Sa

U1

0V

Sb

U2

IL

UL

C

gnd

0V

U2

IR

(c)

Bild 2.6.3.4:

(a) Aufladen von L,

(b) Entladen von L,

(c) Strom IL=I(L),

(d) Strom I1=I(U1).

IL

IL,max

Ib

Ia

Ia

Ib

IL

IL,min

t

0

(d)

Ta

Tb

IL

I1

t

0

IL,max

IL,min

UL,a = UL(0<tTa) = U1

UL,b = UL(Ta<tTb) = U2

dIL,a/dt = UL,a / L = U1 / L

dIL,b/dt = UL,b / L = U2 / L

IL,a = Ta dIL,a/dt = Ta U1/L

IL,b = Tb dIL,b/dt = Tb U2/L

IL,a+IL,b=0 => IL,a=-IL,b => U1Ta=-U2Tb => U2 = -U1Ta/Tb

2.6.3.5 Transformator

Bild 2.6.3.5: Ein Alleskönner (Aufwärts- und

Abwärts-Regelung, Vorzeichenumkehr und

galvanische Trennung) ist der Transformator.

Nachteilig ist sein schwerer Eisenkern.

- SC / Seite 2-39 -

Rsense

0

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.7 Verstärkerstufen mit einzelnem Bipolar-Transistor

(a)

(b)

RC

URc

Q

UB

Q

UC

UB

UE

Q

UE

UBE

CE

0V

RE

0V

Bild 2.7-1:

URc

RC

UC

UBE

UBE

VCC

URc

RC

UC

UB

(c)

VCC

VCC

RE

0V

(a) Verstärkerstufe mit Bipolartransistor und RC=20KΩ, (b) zusätzlicher

Widerstand RE=10KΩ, (c) zusätzliche Kapazität CE.

Die Verstärkung der Stufe in Bild 2.7-1 (a) berechnet sich zu

AV = -gmZ2 = -gm(rCE||RC) -gmRC = -URc/uT [z.B. -2,4V/26mV=-92,3]

Da sie thermisch nicht stabil ist, bauen wir den Emitter-Widerstand RE gemäß Bildteil (b) ein.

RE wird mit 10KΩ so bestimmt, dass UE=VCC/5, was zur Folge hat, dass die Verstärkung auf

-AV = RC / (rm+RE), wobei rm=1/gm=uT/IC [z.B. -20KΩ/10KΩ = -2]

reduziert wird. Um für Wechselspannungen die Verstärkung der Stufe in Bildteil (a) mit der

Stabilität der Stufe in Bildteil (b) zu bekommen, kann RE mit der Kapazität CE für

Wechselspannungen kurzgeschlossen werden. Die rein resistive Impedanz des Emitterknotens

ohne die Kapazität CE berechnet sich zu

ZE = RE||(1/gm) = RE/(1+gmRE).

(Diese Formel der Reduktion einer Knotenimpedanz durch Anschluss eines Emitters oder

einer Source sollte man im Kopf haben!) Die Polfrequenz dieser Stufe liegt dann bei

p = 1/ZECE = (1+gmRE)/RECE

fp = (1+gmRE)/2RECE

Da die Verstärkung nicht unter die DC-Verstärkung von AV,DC=-RC/RE sinken kann, muss der

Frequenzgang eine Nullstelle in

fz = fp AV,DC/AV,AC = fp (-RC/RE)/(-gmRC) = fp/gmRE.

- SC / Seite 2-40 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

aufweisen, weil wir es hier um eine Steigung von 20dB/dec zu tun haben. Bild 2.7-2 stellt

dies im Bodediagramm dar für die Situation AV,DC=-2 (=6dB) und AV,AC=-200 (=46dB).

(a)

(b)

40

VCC

20

lH(s)l

dB 0

URc

RC

UC

0,1

1

10 100 1K

f/fz

0,1

1

10 100 1K

f/fz

-20

UB

Q

-40

UE

UBE

CE

RE

(c)

(H(s))

-90°

0V

-135°

-180°

Bild 2.7-2:

(a) Verstärkerstufe mit AV,DC=-2 (=6dB) und AV,AC=-200 (=46dB),

(b) Amplitudengang, (c) Phasengang.

Komplette Verstärkerstufe mit Bipolartransistor in Emitterschaltung

VCC

Bild 2.7-3:

Verstärkerstufe mit

Bipolar-Transistor.

UR2

IR2

einzelnem

Beispiel:

VCC=5V, ICa=100A, UEa=1V,

UCa=3V, UBE=0,65V, B=ß=200,

RE=10K, RC=20K.

Ck1

R2

RC

Ck2

IB

Rgen

UB

UC

Q

Ugen UR1

IR1

RL

UE

UBE

CE

RE

R1

0V

Bild 2.7-3 zeigt ein typisch Beispiel für eine diskrete Verstärkerstufe, wie sie bis ca. 1980

üblich war. Die Arbeitspunkteinstellung erfolgt mit Hilfe von R1, R2 so, dass IR2≈10IB. Die

DC-Arbeitspunkte werden mit den Koppelkapazitäten Ck1 und Ck2 entkoppelt. Daraus folgt

neben der relativ geringen Verstärkung dieser diskreten Stufe als weiterer Nachteil, dass der

Verstärker nicht DC-fähig ist.

- SC / Seite 2-41 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.8 Verstärkerstufen mit einzelnem Feldeffekt-Transistor

2.8.1 Diskreter Verstärker mit JFET in Source-Schaltung

Bild 2.8.1.1 zeigt einen JFET in Source-Schaltung. Die Koppelkapazitäten Ck1, Ck2 und die

Source-Kapazität CS seien so groß, dass für die interessierenden Frequenzen ihre

Blindwiderstände vernachlässigt werden können, also XCk1=XCk2=XCS0 ist.

UDD

3

RD

1

Ck1

5

Ck2

2

UD

ID

4

iout

U2

6

U1

CS

RG

RL

RS

0

Bild 2.8.1.1: Verstärkerschaltung mit JFET in Source-Schaltung

2.8.1.1 Einstellung des Arbeitspunktes an Gate und Source

Das Eingangssignal U1 wird über die Kapazität Ck1 gleichspannungsmäßig vom Eingang des

FETs entkoppelt. Da der JFET eine Eingangsspannung UGS0V benötigt, legt man den

Arbeitspunkt des Gates mittels RG auf den kleinstmöglichen Wert der Schaltung, nämlich

U Ga 0V .

(2.8-1)

Der Index „a“ steht für „im Arbeitspunkt“. Dieser wird nun mittels RS eingestellt: Der DrainStrom im Arbeitspunkt, IDa, muss über den Source-Widerstand RS abfließen und erzeugt die

Source-Spannung

U Sa RS I Da

(2.8-2)

und somit eine Gate-Source-Spannung im Arbeitspunkt von

U GSa U Ga U Sa U Sa RS I Da .

(2.8-3)

- SC / Seite 2-42 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Die Extremwerte RS=0 und RS-> führen zu den Strömen IDa=IDSS und IDa=0. Um die

Kleinsignalverstärkung der Stufe nicht durch RS zu beeinträchtigen, wird RS kleinsignalmäßig

mit der Source-Kapazität CS kurzgeschlossenen, also XCS=0 im interessierenden

Frequenzbereich.

Die Wahl des Gate-Widerstands RG ist ein Kompromiss. Wegen des hohen Eingangswiderstands des FETs ist der Eingangswiderstand der Schaltung

Zin RG

(2.8-4)

für Frequenzen, bei denen die Gate-Source-Kapazität CGS noch keine Rolle spielt. Da der

hohe Eingangswiderstand einer der charakteristischen Vorzüge dieser Schaltung ist, empfiehlt

sich ein sehr hoher Wert für RG. Ein anderer Vorteil des FETs ist jedoch sein geringes

Rauschen, doch in dieser Hinsicht gilt die Regel hohe Widerstände vor hochohmigen

Eingängen zu vermeiden. Die beste Lösung wäre also RG ganz aus der Schaltung zu

entfernen. Dann jedoch würde UGa treiben (floaten) und der Leckstrom durch die Gate-Diode

die Spannung am Gate langsam aber sicher nach oben schieben. Um die Voraussetzung

UGa=0V sicherzustellen, muss RG bezüglich dieser Leckströme einen Kurzschluss darstellen.

Ein typischer Wert ist RG=1M.

Betrachten wir die Verstärkerstufe in Bild 2.8.1.1, dann gibt es hinsichtlich des

Lastwiderstandes zwei extreme Einstellungen. RL-> und RL=0.

1. Für RL-> steuern wir die Last mit Spannung, z.B. den Eingang eines OPs. Die

Spannungsverstärkung |AV| ist bei dieser Belastung maximal. Die Stromverstärkung wird

wegen i2=0 zu |Ai|=0 und somit ist die Leistungsverstärkung ebenfalls Ap=AVAi=0. In

diesem Fall ist eine Einstellung des Arbeitspunktes UDa gemäß Gl. (2.8-10) sinnvoll.

2. Für RL=0 steuern wir die Last mit Strom, während UDa konstant gehalten wird. Dann ist Ai

maximal, AV=0 und somit auch in diesem Extremfall Ap=AiAV=0.

- SC / Seite 2-43 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.8.1.2 Berechnung des Drain-Stroms IDa für RL=0

UDD

3

URD

RD

Bild 2.8.1.2:

Der

Extremfall

RL=0 kann mit einer

Spannungsquelle als

Last

dargestellt

werden.

UD

1

Ck1

ID

4

iout

S

2

U2

6

U1

CS

RG

RS

0

Bild 2.8.1.2 zeigt den Extremfall RL=0. Er kann mit einer Spannungsquelle als Last

dargestellt werden. In der Realität ist RL niemals wirklich 0, aber beispielsweise die BEDiode eines Bipolartransistors erzwingt eine Spannung von ca. 0,7V. Eine niederohmige Last

arbeitet stromgesteuert.

Am Drain-Widerstand RD liegt eine konstante Spannung. Daher erfährt RD eine Kleinsignalspannung und einen Kleinsignalstrom von Null. In der Tat ist RD in dieser Situation meistens

überflüssig. Wegen uRD=0 ist auch iRD=0. Daher ist

iout = iD = gmu1.

Da der Drain-Strom des FETs zwischen den Extrema ID,min=0 und ID,max=IDSS schwanken

kann, erreicht man die maximale Amplitude î2,max=0,5IDSS, wenn der Arbeitspunkt auf

IDa=0,5(ID,max+ID,min)=0,5IDSS eingestellt ist. Dies setzt allerdings voraus, dass die Last, z.B.

die Basis eines Bipolartransistors, einen so großen Strom verkraften kann.

- SC / Seite 2-44 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

2.8.1.3 Berechnung des Drain-Stroms IDa für RL->

Einstellung des Arbeitspunktes am Drain

Eine solche Schaltung ist gedacht für eine Drain-Spannung von

U D U D , sat U G VT ,

(2.8-5)

wobei VT die Schwellspannung (threshold voltage) ist und nicht mit der Temperaturspannung

uT=kT/q verwechselt werden darf. Bekannter als Gl. (2.8-5) ist die Formel UDS,sat UGS - VT,

welche aus obiger Gleichung folgt, wenn man auf beiden Seiten US abzieht. Wegen UGa=0

und XCk1=0 ist

U G uG u1 ,

(2.8-6)

wobei kleine Buchstaben für Kleinsignalgrößen stehen, also u=U und i=I. Die Sättigungsspannung des FETs schwankt also mit u1 um VT und erreicht einen Maximalwert von

U D , sat VT u1 |VT |

u2

.

| AV |

(2.8-7)

Darin ist AV=u2/u1 die Kleinsignal - Spannungsverstärkung und ûx ist die maximale

Amplitude von ux. Man beachte, dass UD,sat gemäß Gl. (2.8-7) keine Funktion von US und

somit auch keine Funktion RS ist, was die Einstellung des Arbeitspunktes sehr erleichtert.

ID

u2,max

u2,max

u1

u1

u2

UDa,mid

0

0

-VT

UDa,min

UDa,max

UD

UD,min =

UD,max

max(UD,sat)

= UDD

Bild 2.8.1.3: Kennlinienfeld für Verstärkerschaltung mit JFET in Source-Schaltung

- SC / Seite 2-45 -

Prof. Dr. M. Schubert

Skript Schaltungstechnik

Hochschule Regensburg

Um den FET mit Sicherheit in der Sättigung zu halten, darf die Drain-Spannung den Bereich

UD UD,min nicht verlassen, wobei

U D ,min max{U D , sat } |VT |

u2

,

| AV |

(2.8-8.a)

U D ,max U DD .

(2.8-8.b)

Soll die Ausgangsspannung eine gewisse Mindestamplitude û2 ermöglichen, dann muss dies

bei der Wahl des Arbeitspunktes berücksichtigt werden:

1

(2.8-9.a)

U Da ,min U D ,min u2 |VT | u2 1

,

| AV |

U Da ,max U D ,max u2 U DD u2 .

(2.8-9.b)

Die maximale mögliche Ausgangsamplitude erhält man, wenn man den Arbeitspunkt genau in

die Mitte des erlaubten Bereiches der Drain-Spannung platziert:

U Da , mid

u

1

1

(U D ,max U D ,min ) U DD |VT | 2 .

| AV |

2

2

(2.8-10)