6 Integrierte digitale Logikbausteine

Werbung

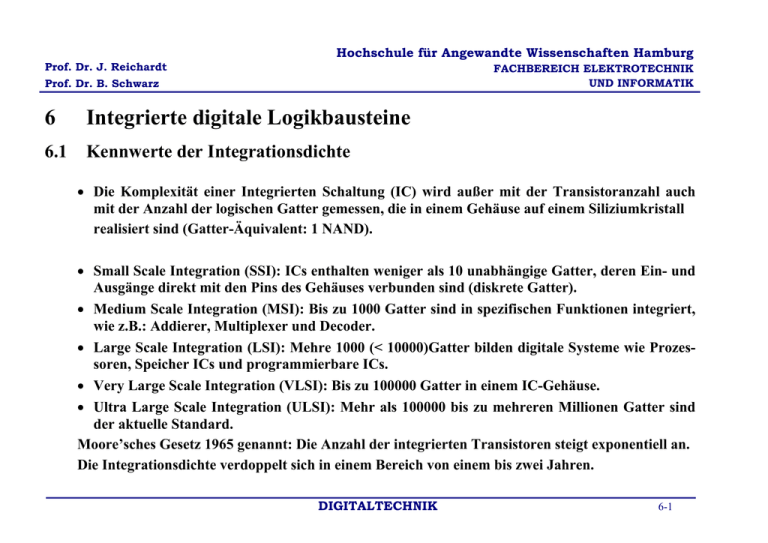

Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 6 Integrierte digitale Logikbausteine 6.1 Kennwerte der Integrationsdichte • Die Komplexität einer Integrierten Schaltung (IC) wird außer mit der Transistoranzahl auch mit der Anzahl der logischen Gatter gemessen, die in einem Gehäuse auf einem Siliziumkristall realisiert sind (Gatter-Äquivalent: 1 NAND). • Small Scale Integration (SSI): ICs enthalten weniger als 10 unabhängige Gatter, deren Ein- und Ausgänge direkt mit den Pins des Gehäuses verbunden sind (diskrete Gatter). • Medium Scale Integration (MSI): Bis zu 1000 Gatter sind in spezifischen Funktionen integriert, wie z.B.: Addierer, Multiplexer und Decoder. • Large Scale Integration (LSI): Mehre 1000 (< 10000)Gatter bilden digitale Systeme wie Prozessoren, Speicher ICs und programmierbare ICs. • Very Large Scale Integration (VLSI): Bis zu 100000 Gatter in einem IC-Gehäuse. • Ultra Large Scale Integration (ULSI): Mehr als 100000 bis zu mehreren Millionen Gatter sind der aktuelle Standard. Moore’sches Gesetz 1965 genannt: Die Anzahl der integrierten Transistoren steigt exponentiell an. Die Integrationsdichte verdoppelt sich in einem Bereich von einem bis zwei Jahren. DIGITALTECHNIK 6-1 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 1000 2X growth in 1.96 years! Transistors (MT) 100 10 486 1 386 286 0.1 0.01 P6 Pentium® proc 8086 8080 8008 4004 8085 0.001 1970 1980 1990 Year 2000 2010 • Die Anzahl der Transistoren in Prozessoren verdoppelt sich alle 2 Jahre [11]. DIGITALTECHNIK 6-2 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz Die size (mm) 100 P6 486 Pentium ® proc 10 386 8080 8008 4004 8086 8085 286 ~7% growth per year ~2X growth in 10 years 1 1970 1980 1990 Year 2000 2010 • Die Chipfläche wächst mit 14% nach dem Moore’schen Gesetz [11, Intel]. DIGITALTECHNIK 6-3 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • 10000 Frequency (Mhz) 1000 2X every 2 years P6 100 Pentium ® proc 486 10 8085 1 0.1 1970 8086 286 386 8080 8008 4004 1980 1990 Year 2000 2010 • Die µP-Taktfrequenz wird alle 2 Jahre verdoppelt [11, Intel]. DIGITALTECHNIK 6-4 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 6.2 Digitale Schaltkreisfamilien • Die Schaltungstechnologie wird den Entwicklungsstufen der Schaltkreisfamilien zugeordnet: ¾ RTL Resistor Transitor Logic ¾ DTL Diode Transistor Logic ¾ TTL Transistor Transistor Logic ¾ ECL Emitter-Coupled Logic ¾ MOS Metal-Oxide Semeiconductor ¾ CMOS Complementary Metal-Oxide Semiconductors • Die Charakteristika der Schaltkreisfamilien werden für die Basisgatter NAND, NOR bzw. Inverter angegeben: ¾ Fan Out: Anzahl der Gatter, die an einem Gatterausgang angeschlossen werden dürfen, ohne dass dessen Betriebsverhalten gestört wird. ¾ Propagation Delay: Mittlere Verzögerungszeit einer Ausgangssignal-Pegeländerung als Folge eines Eingangssignal-Pegelwechsels. ¾ Noise Margin: Maximaler Störpegel, der einem Gattereingangssignal überlagert werden darf, ohne sich der Ausgangpegel ändert (Störspannungsabstand). ¾ Power Dissipation: Mittlere Leistungsaufnahme in mW. DIGITALTECHNIK 6-5 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 6.3 Metal Oxide Semiconductor (MOS) 1 • Die Grundfunktion liefert der Feldeffekt-Transistor (FET). Dieser FET ist ein unipolarer Transistor, da nur eine Ladungsträgerart am Stromleitungsmechanismus beteiligt ist. • Schematischer Aufbau der Halbleiterbereiche eines p-Kanal (a) und eines n-Kanal (b) MOSTransistors [5]. Der Source-Anschluss wird mit dem Substrat verbunden. Der GateSteueranschluss ist vom Silizium durch ein Metalloxyd isoliert aufgebracht. _________________ 1 Die Grafiken in diesem und den folgenden Abschnitten sind der Quelle www.prenhall.com/mano entnommen, vgl. [5]. DIGITALTECHNIK 6-6 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • p-Kanal MOS Transistor: ¾ Unter dem Gate bildet sich ein Kanal mit Löcherleitung, der Drain und Source verbindet, wenn zwischen Gate und dem Source-Anschluss eine negative Spannung angelegt wird: UGS < UTH < 0. ¾ Das über UGS < 0 erzeugte Feld zieht die im n-dotierten Substrat vorhandenen Löcher an, sodass die Leitfähigkeit zwischen den p-dotierten Drain- und Source-Bereichen erhöht wird. Es fließt ein Strom vom Source zum Drain-Anschluss. • n-Kanal MOS Transistor: ¾ Unter dem Gate bildet sich ein Kanal mit Elektronenleitung, der Drain und Source verbindet, wenn zwischen Gate und dem Source-Anschluss eine positive Spannung angelegt wird: UGS > UTH > 0. ¾ Das über UGS > 0 erzeugte Feld zieht die im p-dotierten Substrat vorhandenen Elektronen an, sodass die Leitfähigkeit zwischen den n-dotierten Drain- und Source-Bereichen erhöht wird. Es fließt ein Strom vom Drain- zum Source-Anschluss. DIGITALTECHNIK 6-7 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • Die Symbole auf der jeweils linken Seite bei (a) und (b) zeigen, dass der leitende Kanal bei den so genannten Anreicherungstypen ohne angelegte Steuerspannung UGS unterbrochen ist. ¾ Der Pfeil gibt die Verschiebung der Elektronen im Substrat an, wenn |UGS| > 0 wird. • Ein vereinfachtes, häufig verwendetes Symbol ist auf der jeweils rechten Seite dargestellt. ¾ Der Pfeil zeigt die technische Stromrichtung für den Fall an, dass der Kanal mit |UGS | > |UTH | leitfähig wird. DIGITALTECHNIK 6-8 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 6.4 Complementary MOS (CMOS) • CMOS-Schaltungen bestehen aus beiden Typen der MOS Transistoren, die miteinander verbunden die gewünschten logischen Funktionen bilden. • Die Inverter-, NAND- und NOR-Funktionen ergeben sich durch wechselseitig ein- bzw. ausgeschaltete MOS Transistorpfade. • Beim einfachsten CMOS Element dem Inverter ist der Source-Anschluss des p-Kanal Transistors T1 mit der Versorgungsspannung UDD und der andere SourceAnschluss (T2) ist mit Masse verbunden. • Funktionstabelle: UA UGS1 GND 0 UDD UDD CMOS Inverter [5] UGS2 T1 T2 UY -UDD 0 • Während des Pegelwechsels an A fließt ein Querstrom durch T1 und T2, der den entscheidenden Verlustleistungsbeitrag des Inverters verursacht. DIGITALTECHNIK 6-9 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • Ein CMOS NAND-Gatter mit zwei Eingängen besteht aus zwei parallelen p-Kanal Transistoren und zwei dazu in Reihe geschalteten n-Kanal Transistoren. • Funktionstabelle: UA UB T1 T2 T3 T4 UY • Sind beide Eingänge (A, B) auf High, so leiten die n-Kanal Typen und die p-Kanal Typen sperren. Der Ausgang Y ist dann auf Low. • Wenn nur ein Eingang auf Low ist, sperrt der zugehörige n-Kanal Typ und der zugehörige pKanal Type ist leitend. Der Ausgang Y ist damit auf High. DIGITALTECHNIK 6-10 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • CMOS NOR-Gatter mit zwei Eingängen besteht aus zwei parallelen n-Kanal Transistoren, deren Source-Anschluss an Masse liegt, und zwei dazu in Reihe geschalteten p-Kanal Transistoren. • Funktionstabelle: UA UB T1 T2 T3 T4 UY • Sind alle Eingänge auf Low, so sind beide pKanal Typen leitend und die n-Kanal Typen sperren. Der Ausgang Y liegt dann an UDD . • Ist einer der Eingänge auf High, so sperrt der zugehörige p-Kanal Typ und der zugehörige nKanal Typ leitet. Der Ausgang Y liegt somit an Masse. DIGITALTECHNIK 6-11 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • MOS Transistoren lassen sich als elektronische Schalter auffassen, die entweder geschlossen oder geöffnet sind. • Ausgehend von dieser Sicht besteht der CMOS Inverter (a) aus einem oberen Öffner (p-Kanal) und einem unteren Schließer (n-Kanal). • Liegt am Eingang Uin ein Low Pegel, so schließt der obere Schalter und der untere öffnet. Am Ausgang liegt das Komplement des Eingangs: Uout = UDD . • Häufig wird in technischen Dokumentationen ein vereinfachtes Transistorsymbol (b) zur Verdeutlichung des logischen Verhaltens der Schalter bevorzugt. • Der Gate-Anschluss des p-Kanal Transistors ist darin mit einem Invertierungskreis dargestellt. CMOS Inverter in Schalterdarstellung [5] DIGITALTECHNIK 6-12 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz 6.5 CMOS Kennwerte • Die Leistungsaufnahme der CMOS Logik ist bei statischen Pegeln sehr gering, da die jeweils leitenden Transistoren einen geringen Innenwiderstand haben und die sperrenden nahezu keinen Strom führen: Pstat = 0.01mW. Die Gateanschlüsse zeigen rein kapazitives Verhalten, sodass die Eingänge statisch stromlos (~1µA) sind. • Im dynamischen Betrieb, d.h. bei Pegelwechseln mit z.B. 1µs Periodendauer (1MHz Taktfrequenz) steigt die Leistungsaufnahme auf Pdyn= 1mW und bei 10 MHz auf Pdyn = 5mW. Ursächlich sind die dynamischen Querströme durch die Transistoren, die ihren Leitfähigkeitszustand in endlicher Zeit ändern. • Der Fan-Out der Gatterausgänge spezifiziert die maximal zulässige Anzahl von Gattereingängen, die an einen Ausgang angeschlossen werden dürfen. • Der Fan-Out ergibt sich aus dem Quotienten des max. verfügbaren Ausgangsstromes und der Stromaufnahme eines einzelnen Gatters. DIGITALTECHNIK 6-13 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • Da die CMOS Gatter-Eingänge keinen statischen Strom aufnehmen, ist nur die dynamische Belastung relevant: Fan-Out ~ 30 bei 1MHz. • Die Signalpegeländerungen erfahren vom Eingang eines CMOS Gatters zu dessen Ausgang eine zeitliche Verzögerung, die Propagation Dealy genannt wird. Ursächlich sind die Ladungsträgertransportvorgänge beim Aufbau und Leeren eines Kanals, die das kapazitive Verhalten bestimmen. Aufgrund des symmetrischen Aufbaus von CMOS Gattern sind die Zeiten tpLH und tpHL gleich. • Gemessen wird zwischen den 50 % Pegeln der Versorgungsspannung. • CMOS Inverter der Reihe 74AHC04: tpLH = tpHL = 5ns bei 15 pF Lastkapazität. DIGITALTECHNIK 6-14 Hochschule für Angewandte Wissenschaften Hamburg Prof. Dr. J. Reichardt FACHBEREICH ELEKTROTECHNIK UND INFORMATIK Prof. Dr. B. Schwarz • Der maximale, verfügbare Störabstand (Noise Margin) ergibt sich aus zwei Wertepaaren: High-Ausgang: ∆H = UOH - UIH ; Low-Ausgang: ∆L = UIL - UOL • Störspannungen, die sich einem Ausgangspegel überlagern, dürfen die Signalhübe ∆H bzw. ∆L nicht überschreiten, da die Eingangsstufe eines CMOS Gatters ansonsten keine korrekte Low- oder der HighErkennung durchführt. • CMOS NAND der Reihe 74AHC00: ∆H = UOH - UIH = 4,6V–3,5V = 1,1V ∆L = UIL - UOL = 1,5V-0,3V = 1,2V DIGITALTECHNIK 6-15