LVA 354.028 Integrierte Schaltungstechnik

Werbung

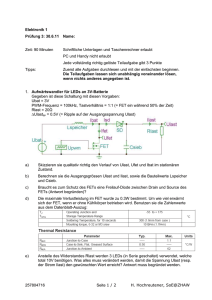

Ausarbeitung der gesammelten Fragen der LVA 354.028 Integrierte Schaltungstechnik Diese Ausarbeitung wurde gemeinsam von Martin Fein und Christian Schwingenschlögl im Laufe der Prüfungsvorbereitung erstellt und ist nach bestem Wissen und Gewissen ausgearbeitet worden! 2 Unterschied zwischen integrierten und diskreten Bauteilen (Seite 1): Diskrete Bauteile Integrierte Bauteile kleinere Toleranzen der Wiederstandswerte Große Toleranz der Widerstandwerte absolute Genauigkeiten sehr gut Widerstandsbereich: mΩ - GΩ Widerstandsbereich: Ω - kΩ Kapazitätsbereich: pF – mF Kapazitätsbereich: fF – pF Induktionsbereich: nH – H Induktionsbereich: nH große Werte Kleine Werte Kombination von verschiedenen Silizium dominiert (SiGe) bei NMOS, PMOS Semikonducter-Materialien möglich (+NPN) Selection of key device possible Ungenauigkeiten (mismatch) bleiben mit (z.B.: low-noise u high-noise HEMT) Laser oder Sicherungen abgleichen high-electron-mobility-transistor “Transistor mit hoher Elektronenbeweglichkeit“ Hoher Preis pro Transistorfunktion Kleiner Preis pro Transistorfunktion Begrenzte Geschwindigkeit Hohe Geschwindigkeiten (high speed) am Chip möglich Warum gibt es Design Regeln? (DRC – Design Rule Checking) (Seite 2) DRC: (Seite 70) ist ein Layout- u Verifikationstool. Chiphersteller gibt dem Schaltungsdesigner bestimmte Spezifikationen/Entwurfsregeln für einen Chip vor (z.B.: Mindestabstände-, Mindestbreiten-, Überlappungen-, Innenlagen der einzelnen Layer, …) nach dem Entwurf müssen die Einhaltung dieser Regeln überprüft werden automatisch mittels DRC; falls etwas nicht passen sollte gibt es Re-Design. Was ist Analog IC Design? Analog IC Design (Entwurf) ist die erfolgreiche Implementierung analoger Schaltungen und Systeme unter Verwendung von IC Technologien. o Geometrie ist sehr wichtig! Electrical Design Physical Design Test Design o Für gewöhnlich gemischte Architekturen (analog/digital) o Analog 20% u digital 80% der Chipfläche o Jedoch benötigt analoges 80% der Entwurfszeit (im Circuit Level) !! Zusammenfassung: o IC kombiniert Funktion und Applikation mittels IC Technologien für eine erfolgreiche Lösung o 3 Hauptschritte in der Entwicklung: Electrical Design: Topologie, W/L (Width u Length), DC Schaltkreise Physical Design (Layout) Test Design (Test) o Komplexe Probleme können durch Knowhow und flexible Designer vereinfacht und verstanden werden u somit implementiert werden o IC wird mehr von alt bewährten Technologien getrieben als von ganz neuen o IC Entwurf hat seine „Reife“ erlangt (ist ausgereifte Technologie) o Wenn das Problem ökonomisch digital gelöst werden kann, verwende NICHT analoge Schaltungen! 3 Wie wird der Chip im Wafer realisiert? (Seite 25 ff) Oxidgrowth (Oxidation) Diffusion Ion Implementation Deposition (Schichtabscheidung) Etching Epitaxy Photolithography Auf dem Silizium Wafer wird eine Schicht Silizium Oxid ‚aufgewachsen‘. VT: unterliegende Material wird vor Verschmutzung geschützt, Isolation zw. 2 Schichten; Maskieren; Gateoxid erstellen; für dünne Schichten: dry oxidationtechniques für dicke Schichten: wet oxidationtechniques Hier werden Fehlatome von der Obefläche des Siliziums in das Innere (Bulk) befördert; von hoher zu niedriger Konzentration! Bei hohen Temperaturen (800 - 1200 °C) Bei diesem Schritt werden Fehl Ionen eingepflanzt; dies passiert mit hoher Geschwindigkeit; VT: gut kontrollierbar u wiederholbar; Konzentrationsspitze knapp unter der Oberfläche; bei niedrigen Temperaturen (im Verhältniss zu Diffusion); geht durch die Oberfläche;Ausglühen ist notwendig um die Fehlionen zu ‚aktivieren‘ u die Kristallstrukturschäden zu reparieren (500 – 800 °C); bei noch höheren Temperaturen Difusion Verschiedene Materialschichten werden am Silizium Wafer abgeschieden: SiliziunNitrat, Silizium Oxid, Aluminium, Polysilicon Verschiedene Arten: Chemical Vapor Deposition (CVD): chemische Reaktion das ein Gas als dünnen Film auf der Oberfläche transformiert Low Preassure CVD Plasma Assisted CVD: keine thermische Energie wird verwendet Sputter Deposition Anwendung am ganzen Layer Selektives beseitigen von Layermaterial: Mask, Film, Underlying Layer Etzrate in bestimmte Richtungen (film etch rate / mask etch rate Zur Herstellung von Dotierungsschichten die mit üblichen Verfahren (Diffusion Ion Implementation) nicht realisiert werden können; Epitaxyschichten sind viel reiner Um das Layout mittels einer Maske auf den Chip zu bringen; Photoresist Material, Mask, Oxid (Wo Maske rauf kommt) Positiv- u negative photolitograpy 4 CMOS Aufbau: (Seite 36) Complementary Metal Oxyd Semiconducor) PMOS u NMOS auf einem Substrat Auch in p-well Technologie realisierbar! (n-substrate p-well) Well tie & Subtrate tie = Bulk Anschlüsse des PMOS u NMOS Backgate = Bulk Backgate Effekt: Mit der Spannung VSB kann die Schwellspannung Vth verändert werden: VSB↑ Vth↑ Herstellung eines PNP Transistors (Seite 52,53): Es gibt 2 Arten: 5 Aufbau MOS Transistor: (Seite 39) (NMOS u PMOS siehe 1.Bild CMOS Aufbau) + parasitäre Effekte: Ist eigentlich ein NMOS auf n-Substrat. NMOS: Source u Drain n+ dotiert PMOS: Source u Drain p+ dotiert CMOS (Complementary Metal….) bedeutet sowohl PMOS als auch NMOS auf einem Substrat 6 BJT NPN u PNP Aufbau: NPN mit buried Layer: PNP siehe Frage: Herstellung eines PNP Transistors Unterschiede zwischen MOS und BJT: (Seite 59) MOS BJT Spannungsgesteuert Stromgesteuert Negativer Temperaturkoeffizient Positiver Temperaturkoeffizient Majoritätsladungsträger Bauteil Minoritätsladungsträger Bauteil ID ~ VGS2 IC ~ exp(VBE) Gut geeignet für IC Schlecht geeignet für IC Probleme mit CMOS: o Längere Transistoren führen zu höheren Strömen o Schalten von hohen Spannungen mit Standard CMOS ist nicht möglich BJTs werden für Leistungstransistoren bevorzugt! Gibt es Bipolartransistoren in reiner CMOS Technologie? (Seite 41) Ja, natürlich… 7 Performance (Stromverstärkung u Übertragungsfrequenz) können nicht mit dem vertical NPN Transistor in SBC (Standard Buried Collector) Technologie (Buried Layer: siehe Bild NPN Aufbau) mithalten. ESD Schutz (Seite 43): Um das Gate Oxid vor hohen externen Spannungen zu schützen wird ‚Electrostatic-Discharge Protection‘ (ESD) verwendet. Hervorgerufen kann dies werden durch: o Induktivitäten: wenn die Oberfläche von einem nahen el. Feld polarisiert wird o Capazitiv: wenn die Kapazität des Gehäuse, das auf fixem Potential liegt, steigt o Reibungselektrizität: wenn zwei Materialien die getrennt werden Ladung als Folge von Reibung austauschen (z.B.: der Mensch kann eine wesentliche Ladung aufweisen) Vergleich zwischen MOSFET und BJT: Analog IC: BJT sind besser Digital IC: CMOS sind besser Analog/digital IC: BiCMOS o Verstärkung und Bandbreite vom BJT sind viel größer als die des MOS Verstärkers o Steilheit: gm,BJT ≈ 10 * gm,MOS o Temperaturverhalten: MOS: T↑ µ↓ gm↓ BJT: T↑ IC↑ gm↑ o Geschwindigkeit: bei BJTs werden Kapazitäten schneller geladen und entladen o Rauschen: In Transistorschaltungen zur Signalverarbeitung wie Vorverstärker ist das Rauschen eine wesentliche Störgröße. Es spielt dabei vor allem das thermische Rauschen, das Schrotrauschen sowie das 1/f-Rauschen eine Rolle. Bei dem MOSFeldeffekttransistor ist das 1/f-Rauschen bereits unter ca. 1 MHz besonders groß. Das unterschiedliche Rauschverhalten bestimmt ebenfalls die möglichen Einsatzbereiche der Transistortypen, beispielsweise in Niederfrequenzverstärkern oder in speziellen rauscharmen Hochfrequenzumsetzern. o Matching: baugleiche Transistoren müssen möglichst gleiche Bauteilparameter aufweisen. BJT: IS, β, VA, Emitter area MOSFET: VT, K‘, λ, Width & Length 8 CMOS BiCMOS Vorteile/Nachteile: BiCMOS = CMOS + NPN BJT (vertical) (meistens) Allgemein BiCMOS: Kombination von MOSFET und BJT. Eingang und logische Verknüpfung in CMOS Technik (Vorteile von CMOS); Ausgangsstufe als BJT realisiert Vorteil BiCMOS: hohe Stromtreiberfähigkeit und geringe Abhängigkeit von der kap. Last; mit BiCMOS werden Logikschaltungen mit leistungselektronischen Schaltungen auf einem Chip vereint. Zum Schalten und Regeln hoher Ströme Nachteile: BiCMOS können beispielsweise nicht gut in Microprozessoren eingesetzt werden. Herstellung ist teuer! BiCMOS bei analog/digitalen Schaltungen CMOS bei rein digitalen Schaltungen Vorteile CMOS: nahezu keine Stromaufnahme ohne Zustandsänderung (zB.: BIOS),sehr niedrige Kosten, extrem niedriger und unkritischer Leistungsbedarf, nahezu unendlich große Eingangswiderstände, gute Rauscheigenschaften Nachteil CMOS: Ausgänge sind empfindlich gegen Belastung (speziell kap. Belastung), bei hohen Frequenzen >5MHz hohe Verluste Matching/Mismatching (Seite 75-77) Mismatch tritt auf wenn gleiche Bauteile Abweichungen in deren Parametern haben. Matching siehe Frage ‚ Vergleich zwischen MOSFET und BJT‘ o MOS: 2 spezielle Modellparameter: ΔVth (=Schwellspannungs Mismatch) und ΔID/ID (=Drainstrom Mismatch) σ ΔVth … Standardabweichung von ΔVth σ ΔVth = ist ein const technologieabhängiger Faktor. In den meisten Fällen reicht dieser Faktor aus, um das gesamte Mismatchverhalten zu beschreiben. σ ΔID/ID … Standardabweichung von ΔID/ID σ ΔID/ID = o hängt stark von (VGS- VTH) ab. Wenn (VGS- VTH) ↑ BJT: 2 spezielle Modellparameter: ΔIC/IC, ΔIB/IB und deren Standardabweichungen σ ΔIC/IC = ↓ We u Le… width u length of emitter σ ΔIB/IB = o o Methoden gegen Mismatch: (Seite 74) Einheitliche Bauteilgeometrien des selben Materials sollten verwendet werden. Für kleine Geometrien ist das Matching Verhältnis 2:1; Matching Elemente sollten möglichst nahe beisammen sein, selbe Orientierung aufweisen, Dummy Elemente sollten am Rand von Matching Elementen hinzugefügt werden (zwischen 2 verschiedenen). Teile die die höchsten Anforderungen haben sollten im Zentrum des Chips (die) platziert werden, thermal sensitive Elemente sollten soweit wie möglich von energieverbrauchenden Bauteilen entfernt sein. Temperatur macht beim BJT Probleme, BJT haben einen pos. Temperaturkoeffizienten 9 Integrierte Kapazitäten und Widerstände: Standard MOS Kapazität: o D=S=B o Arbeitet zwischen Accumulation (Vorwärtsbetrieb) und Inversion (Rückwärtsbetrieb), aber const hohe Kapazität nur bei Accumulation und starker Inversion! o Nichtlinear u nichtmonoton o Supply blocking capacitaors on Chip Inversion Mode MOS Kapazität: D = S; B = VDD keine Accumulation Region!! Poly-Poly Kapazität: Best möglicher Kakazität für analoge IC, niedrige parasitäre Effekte, Spannungsunabhängig Ploysilicon Widerstand: o 30 – 100 /square (unshielded) o 100 – 500 square(shielded) o Abs Genauigkeit ±30% o Rel Genauigkeit 2% o Temp Koeffizient 500 – 1000 ppm/°C o Spannungskoeffizient 100 ppm/V 10 Stomspiegel: (Seite 82ff) Stromspiegel sind sehr wichtig für analoge u digitale ICs! Mirror Ratio (Spiegelverhältnis) = I0/IREF Welche Arten: o Standard Stromspiegel: MOS bzw. BJT Bauart realisierbar! MOS: Für idente Werte von VDS ist I0 = IREF Jedoch ist dies in der Realität wegen Mismatch nicht gegeben! Ausgangswiderstand: ROUT = ro2 … Ausgangswiderstand des Transistors M2 BJT: Da Basisströme vorhanden sind, und die Stromverstärkung endlich ist ( ≈ 100) resultiert ein Errorfaktor beim Ausgangsstrom: (für ≈ 100 Fehler = 2%) Ausgangswiderstand: ROUT = ro2 … Ausgangswiderstand des Transistors Q2 Um die Leistung zu erhöhen, kann die Mirrorratio verändert werden: MOS: es werden W/L der beiden NMOS verändert: BJT: die Emitterflächen werden in ein Verhältnis zueinander gesetzt: Im Idealfall (Verstärkung ): I0/IREF = M 11 Sonst: o Multable Current Sources: Wird benötigt, wenn mehrere verschiedene Stromquellen verwendet werden. Problem: für BJT würde der Fehler bei endlichem unakzeptabel groß werden! Buffered Current Mirror o Buffered Current Mirror: Erweiterung um einen BJT Q3: es wird dadurch der Basisstrom IB1 und IB2 reduziert Errorterm wird kleiner!! o Widlar Current Source (BJT): Erweitert den Standard-Stromspiegel um einen Widerstand im Emitterzweig 2. Dies schafft einen zusätzlichen Freiheitsgrad für die Mirror Ratio. Durch R wird der Ausgangsstrom IO festgelegt. 12 Ausgangswiderstand: ROUT = K*ro2 … Faktor K * Ausgangswiderstand des Transistors Q2 ROUT ist bei der Widlar Source um das 1 bis 10 fache Größer als beim StandardStromspiegel!! Widlar Source ist auch mit MOS realisierbar! (Seite 96 ff) Erweitert den Standard-Stromspiegel um einen Widerstand im Sourcezweig 2 ROUT = ro2(1+gm2*R) o Wilson Source: (Seite 98ff) Die Wilson Source ist ein Stromspiegel mit sehr hohem Ausgangswiderstand! Wird benötigt für hohes CMRR bei OPAMPs. MOS: Ausgangswiderstand: ROUT = µf2*ro3 Als BJT: Ausgangswiderstand: ROUT = Dieser Ausgangswiderstand ist im Verhältnis zum Standard-Stromspiegel um den Faktor erhöht!! 13 Um jedoch bessere Ergebnisse bei Präzisionsschaltungen zu erlangen wird ein weiterer Transistor hinzugefügt: o Cascode Current Sources (MOS u BJT): Hier werden 2 Standard-Stromspiegel kaskadiert: MOS: Ausgangswiderstand: ROUT = µf4*ro2 BJT: Ausgangswiderstand: ROUT = Die Cascode Source und die Wilson Source sind die besten Stromspiegel, da sie hohe Werte von VCS und hohe Ausgangswiderstände gewährleisten! Referenzstromquelle: (Seite 108) Alle bisher besprochenen Stromspiegel benötigen eine Referenzstromquelle: Einfachste Möglichkeit ist: Widerstand R vorschalten (a) oder 2 MOSFETs in Serie (b): 14 Bandgap Referenzquelle (BGR): (Seite 115) o Ziel ist es, die Referenzspannungsquelle unabhängig von der Temperatur zu machen Prinzip: Kombination von VBE und VT: VBE↓ mit T↑ Generation einer Spannung VT die diesen Abfall von VBE kompensiert o Praktische Realisierung eines BGR: (a) Ohne OPAMP: Feedbackloop mit Q4 wird verwendet, um den Arbeitspunkt festzulegen; VOUT ist von der Versorgungsquelle abhängig. (b) Mit OPAMP: I1 und I1 verhalten sich wie R1 und R2; OPAMP ist ideal kein Offset!) o Kompabilität mit CMOS Technologie: Die meisten CMOS Prozesse sind N-well Prozesse! Daher ergeben sich nur PNP Transistoren!! Mit Collector = Substrate (= Ground) o Problem mit BGR: In der Realität hat der OPAMP eine Offsetspannung VOS Fehler in VOUT VOS (ist auch temperaturabhängig) wird mit einem Faktor (1+R2/R1) verstärkt! LÖSUNG: Es gibt 3 Möglichkeiten: (1) Einbinden großer Bauelemente um Offset zu minimieren (2) Collectorstrom von Q1 und Q2 kann mit einem Faktor m ins Verhältnis gebracht werden (3) ein zusätzlicher PNP Transistor wird in jeden Zweig hinzugefügt um ΔVBE zu verdoppeln. ( jedoch nicht realisierbar in StandardCMOS Q2 u Q4 sind nicht geerdet in Emitterfolger konvertieren!!) 15 PTAT (Proportional To Absolute Temperature): (Seite 119 u 125) Prinzip: wenn 2 BJT mit unterschiedlichen Kollektorströmen arbeiten, dann ergibt sich eine Differenz ΔVBE ihrer Basis-Emitter-Spannungen, die ebenso von der absoluten Temperatur abhängig ist! (PTAT) ΔVBE = VBE1 - VBE2 = VT*ln(n) daraus ergibt sich ein pos. Temperaturkoeffizient (TC): In BGR Schaltungen sind die Bias Ströme der Transistoren ebenfalls proportional zur absoluten Temperatur. Dadurch ist es möglich eine Strombasierende PTAT Bandgap Quelle zu generieren. Was ist ein einfacher OTA (Operational Transconductance Amplifier) (Seite 147) o Ein OTA ist ein OPAMP der die Differenzspannung an den beiden Eingängen in einen proportionalen Ausgangsstrom umwandelt. T1 und T2 sind matching Transistoren (gleiches W/L); keine Vorspannungs-Schaltungen für Lasten nötig; T3 und T4 sind ebenso matching Transistors; IB bestimmt alle Stromstärken; Alle wells sind mit den Sources verbunden (ebenso Bulk = Source) VBS = 0 , d.h.: kein Body-Effekt! Somit wird Matching verbessert; o Gain-Bandwidth (GBW): Es existieren 2 Pole: ein dominanter (fd) und ein nicht-dominanter (fnd) (Knoten (5) und (4) im vorherigen Bild) und Dadurch ergibt sich die Spannungsverstärkung zu AV = gm1 * ROUT !! Phasenrand ist im Frequenzgangdiagramm die Differenz zu -180° Phasenlage (PM ist pos. für arg. > -180° 16 Phasenrand (Phase Margin): PM = 90° - arctan(GBW/fnd) Es ist ersichtlich, dass sowohl die Bandbreite (GBW), die Spannungsverstärkung (AV) und der Phasenrand (PM) von der Steilheit (gm1) abhängen o Funktionsweise einfacher OTA: IOUT = UIN * gm Eine Ausgangsspannung kann durch eine externe Last generiert werden. Funktion ohne Widerstände sondern nur mit Transistoren realisiert! o Funktionsweise Miller OTA (2-Stufen Miller OTA): Der Miller OTA ist eine Erweiterung des Standard-OTAs. (siehe nächste Grafik) Die Erweiterung betrifft einen zusätzlichen invertierenden Verstärker und somit wird der Miller OTA ziemlich schnell. Die Pole und Nullstellen des Miller OTAs heben sich soweit auf, jedoch gibt es ein Problem bei sprunghaften Eingangssignalen Dominate Pol ändert kurzfristig seine Frequenz höheres Überschwingen Allgemeines (Seite 164): Die Pole f1 und f4 liegen nahe beisammen negativer Phasenrand (PM)! Durch die zusätzliche Kapazität CC wird der Phasenrand wieder positiv. Die GBW hängt beim Miller OTA nur mehr vom CC ab und NICHT vom CL siehe nächste Formel. und Phasenrand (Phase Margin): PM = 90° - arctan(GBW/fnd) o Spannungs-Verstärkung des Miller OTA: 1. Stufe: Niederfrequenzverstärkung: Av10 = gm1/(gOUT2+gOUT4) 2. Stufe: Niederfrequenzverstärkung: Av20 = gm6/G’L mit G’L = 1/RL + gOUT5 + gOUT6 Av0 = Av10 * Av2 BW = GBW/AV VT/NT Miller OTA und einfacher OTA: Miller OTA Einfacher OTA VORTEILE Maximale Leistungsvertärkung Keine zusätzliche Kompensationskapazität Maximales Signalschwingen Niedrigerer Leistungsverbrauch Besserers PSRR (Power Suppl Rejection Ratio = Netzstörunterdrückungsverhältnis) NACHTEILE Benötigt zusätzliche Kapazität für Kleineres Signalschwingen Frequenzkompensation Größerer Leistungsverbrauch 17 o o Eigenschaften Miller OTA: Slew Rate: maximale Anstiegsrate. Bei niedrigen Frequenzen wird Ausgangsspannung von der Versorgungsspannung begrenzt; bei hohen Frequenzen limitiert die SR die Ausgangsspannung Settling Time: (Zeit bis Error < 0,1%) entweder durch SR oder τd (durch BW gegeben) begrenzt Input Impedanz: RIN ZIN ist kapazitiv und fällt mit f Ausgangswiderstand: für kleine Frequenzen ZOUT ~ 550k ; für hohe Frequenzen ZOUT ~ 5k; Temperaturverhalten: nur der Faktor Kn‘ ist temp.abhängig T-mit Rauchverhalten: jeder MOS besitzt thermisches und 1/f Rauschen: Niedrige u mittlere Frequenzen: 1/f Rauschen ist dominant! Für hohe Frequenzen: 1/f Rauschen spielt keine so große Rolle und die Kapazitäten müssen betrachtet werden Miller-Effekt: Als Millereffekt wird die Vergrößerung der Eingangskapazität eines invertierenden Verstärkers bezeichnet, die aufgrund der effektiven Verstärkung der Kapazität zwischen Ein- und Ausgang dieses Verstärkers auftritt. Dieser Effekt ist meist störend, kann aber auch zum Erzeugen größerer effektiver Kapazitätswerte vorteilhaft genutzt werden. Miller OTA CMRR (Common Mode Rejection Ratio) (Seite 201): o = Gleichtaktunterdrückung gibt an, wie wenig sich die Ausgangsspannung ändert, wenn sich die beiden Eingangsspannungen eines elektrischen Differenzverstärkers um den gleichen Betrag (=„Gleichtakt“) ändern. Im Idealfall sollte sich dann die Ausgangsspannung des Differenzverstärkers nicht ändern, weil sie nur von der Differenz der beiden Eingangsspannungen abhängt. CMRR und der Offset hängen vom Matching der Transistoren ab. CMRR = Add/Adc Add … Verstärkung für einen reinen Differenzverstärker = gm1 * RL Adc … Verstärkung für einen reinen Gleichtaktverstärker Eingänge auf gleiches Potential! CMRR kann verbessert werden durch: hohe Eingangs Transkonduktanz (Steilheit) gm1 und hohen Ausgangswiderstand (RB) der Stromquelle. Zusammenhang mit dem Offset: VOS * CMRR = IB * RB 18 o o Offset und CMRR bei Bipolar Differenz Verstärkern im Gegensatz zu MOS: Der Offset ist bei Bipolar Differenzverstärkern um eine Größenordnung (Faktor 10) KLEINER als bei MOS Differenzverstärkern! Offset u CMRR: VOS * CMRR = 2gm * RB *(k*T)/q CMRR ist für typische Werte um einen Faktor 10 GRÖßER als beim MOS! Kann man die Eingangsströme (bias current) von bipolaren Differenzverstärkern kompensieren? (Seite 207 - 209): Die Differenz der beiden Eingangsströme Ibias ist Ibos. Der Offset Ibos ist ca. 5 – 10 % von Ibias . Kann zwar nicht auf 0, aber auf 1/10tel bis 1/20tel. (5 – 10%) reduziert werden. 2 verschiedene Schaltungen im Skriptum: 19 o PSRR (Power Supply Rejection Ratio): (Seite 210) = Netzstörunterdrückungsverhältnis Digitale Schaltungen in Mixed-Signal Chips verursachen Spannungsspitzen an VDD und VSS; mittels einer hohen PSRR kann nur das Einkoppeln dieser Spannungsspitzen in analogen Schaltkreisen vermindert werden. PSRRDD = Av/ADD = vDD/vIN PSRRSS = Av/ASS = vSS/vIN (vDD und vSS sind die jeweiligen Spannungsspitzen) 20 Symmetrischer CMOS OTA (SOTA): (Seite 215) Die Transistoren T5 und T6 sind um den Faktor B weiter als T3 und T4. Dieser Faktor B bedingt einen größeren Leitwert (Steilheit) G B * gm1 als beim einfachen OTA. Verstärkung: Av = B * gm1 * ROUT Aber gleichzeitig wird ROUT um den Faktor B kleiner Die GBW eines SOTAs ist um den Faktor B größer als die eines einfachen OTAs. Der totale Stromverbrauch ist um den Faktor (B + 1) größer als beim einfachen OTA. Wegen des Phasenrands kann der Faktor B nicht besonders groß gemacht werden. PM↑ für: Cn5↓ bzw Cn6↓; B↓; (W/L)7↑ Die Slew Rate (SR) des SOTAs ist um das B fache größer als die des einfachen OTAs o Symmetrical BiCMOS OTA: Die NMOS (eher PMOS?)Transistoren werden durch NPN Transistoren ersetzt Die PMOS Transistoren als Eingang auf Grund des hohen Eingangswiderstandes und des hohen SR/GBW Verhältnisses; Vorteil: größerer Output swing u Knoten 4 u 5 haben kleinere Impedanz Nachteil: Rauscheigenschaft ist schlecht, da Av1 kleiner wird o Komplementäre SOTA: normaler SOTA, jedoch ist die Schaltung auf den Kopf gestellt und die Eingangstransistoren 21 werden durch PMOS Transistoren ersetzt. o Kaskaden SOTA: (Cascoded SOTA) (Seite 220) Transistoren M7 – M10 erhöhen die open Loop Verstärkung (VORTEIL). Sie werden von den Transistoren M15 – M18 mittels der Stromquelle IB und M14 beeinflusst; Nur der Ausgangsknoten hat hohe Impedanz; Av0 = gm1 * ROUT GBW ~ GBW von SOTA jedoch wird die Steilheit um gmb1 erhöht o Folded Cascode CMOS SOTA: (Gefalteter Kaskaden CMOS OTA) (Seite 223): Der Output Swing wird durch das Falten erhöht (VORTEIL) M7 – M9 sind kaskadierte Stromspiegel Der Strom von M3 ist doppelt so groß als jener von M1 Verstärkung: die einzig hohe Impedanz ist wieder der Ausgangsknoten Av0 = gm1 * ROUT wobei ROUT sehr groß werden kann! (VORTEIL) Slew Rate: SR = o Folded Cascode BiCMOS SOTA: (Gefalteter Kaskaden BiCMOS OTA) (Seite 226): In Vergleich zum Folded Cascode CMOS SOTA werden die Transistoren M5 u M6 durch NPN Transistoren ersetzt. Dadurch werden die Knoten 8 u 9 niederohmig. Dadurch kann ein hoher Phasenrand (PM) realisiert werden. 22 Komparatoren: (Seite 243) Komparatoren sind die grundlegenden Bauelement für ADCs. Allgemein: Am Ausgang des Komparators steht ein Signal zur Verfügung, das anzeigt, welche der Eingangsspannungen höher ist. Wenn die Spannung am positiven, nicht-invertierenden Eingang höher ist als die Spannung am negativen, invertierenden Eingang, so nähert sich die Ausgangsspannung der positiven Versorgungsspannung. Bei umgekehrten Verhältnissen geht die Ausgangsspannung gegen die negative Versorgungsspannung. Reale Komparatoren: o Endliche Empfindlichkeit o Offset o Endliche Geschwindigkeit 2 Typen von Komparatoren: o Kontinuierlicher Betrieb (OPAMP): hohe Verstärkung notwendig o Sample Betrieb (S&H, Verstärker A, Latch): kleine Verstärkung von A ist ausreichend (ist schneller!) Empfindlichkeit: das ist die kleinste Eingangsspannung / der kleinste Eingangsstrom, der nötig ist, um einen konsistenten Ausgang zu bekommen. Input Offset Spannung VOS: Spannung die am Eingang anliegen muss, damit der Ausgang Null liefert. Verstärker Antwortzeit tr: benötigte minimale Verarbeitungszeit um einen richtigen logischen Ausgang zu erlangen Hysterese: sollte größer als das Rauschlevel sein. o Offset Compensation: die benötigte Empfindlichkeit beträgt ~ 1mV. CMOS haben jedoch einen Offset in der Größenordnung von 10 mV!! Auto zero techniques sind notwendig allgemein: in der 1. Phase wird VOS vom S&H Glied gelesen; im der 2. Phase wird die Eingangsspannung durchgeschaltet und mit dem Betrag des S&H Glieds (VOS) summiert; dann wird die Summe am invertierenden Eingang des Verstärkers angelegt VOS kürzt sich raus; Implementierung erfolgt mittels Kapazität am Eingang (siehe Bild unten) 23 o Latch (Aufbau): (Seite 254) o Latch steuert eine weitere Verstärkung hinzu, es generiert einen logischen Ausgang, es gewährleistet stabilen Ausgang der synchron zum Takt ist; TODO Funktionsweise Seite 249 ff !!! Sample & Hold Glied: (Seite 271) Anwendung in: ADCs, Switched Capacitor (SC) Filters, Komparatoren Schaltet, um das Sampeln durchführen zu können. Hohe Eingangsimpedanz Vorteile von MOSFET gegenüber BJT: o eingeschaltet aber kein Stromfluss o S/D Spannungen sind nicht mit der Gate Spannung verknüpft o Leitet in beide Richtungen MOSFET Schalter Fehler: o Endliche Aufnahme (acquisition) Zeit o Endliche Bandbreite in Samplemode o DC Offset in Samplemode (VOS1) o Endliche Aperturzeit (t) o Abfall in Hold Mode 24 … im linearen Bereich Widerstand ergibt sich ja aus den Parametern RON = des MOSFET Wenn der Schalter ON ist, lädt sich der Kanal mit einer bestimmten Ladung. Nach dem Ausschalten muss sich die Ladung abbauen ca. 50% gehen zum Ausgangsknoten (der genaue Wert ist sehr von bestimmten Parametern abhängig), falls die Taktrate zu klein ist, wird die gesamte Ladung vom Eingang absorbiert; Clock feed-through: Beim Ausschalten des Schalters wird eine zusätzliche Kapazität (abhängig von Bauteil Parametern des MOS) auf den Ausgang wirksam. Bei kleiner Clockrate ist diese jedoch sehr klein. Um Ladungsinjektion zu verhindern, wird ein weiterer MOSFET als Schalter hinzugefügt (Dummy Switch), jedoch mit entgegengesetztem Clock und W2 = W1/2 ! o kT/C Rauschen: (Seite 275) äquivalente Schaltung mit Rauschquelle: Mittelwert von vn² = 4*k*T*RON*f Mittelwert von vOT² = k*T/CH vOT(rms) = 25 Unabhängig vom Eingang liegt am Ausgang immer diese Rausschspannung vOT(rms) an. Switch Capacitor (SC): (Seite 278) … sind elektronische Filter, die in ihrem Schaltungsaufbau statt ohmschen Widerständen geschaltete Kondensatoren besitzen. Prinzip: Widerstand kann als geschaltet Kapazitäten realisiert werden! o Vorteile: Kondensatoren sind in CMOS leichter zu realisieren als Widerstände Wert der Kapazität ist temperaturunabhängig Kapazität verbunden mit dem Ausgang eines OPAMP wirkt sich nicht auf dessen Widerstand aus und folglich auch nicht auf die open loop Verstärkung o Nachteile: Clock feed-through ist ein Thema Die 2 Taktraten dürfen sich nicht überlappen Bandbreite des Signals muss kleiner als die Taktfrequenz sein Der äquivalente Widerstand ergibt sich zu: Requ = T/C mit T = Periodendauer Wird beispielsweise bei S&H Glied verwendet Oszillatoren Verwendung: als Taktgenerator in Microprozessoren; zur Trägersignalgenerierung bei Mobiltelefonen; Realisierung ist in CMOS noch immer eine Herausforderung, oft in Phase locked Loop Systemen realisiert Arten von Oszillatoren: Ringoszillator, LC Oszillator, VCO, … Systeme mit negativer Rückführung oszillieren möglicherweise; „Ein Oszillator ist ein schlecht designter Rückkopplungs-Verstärker….“ „In der Hochfrequenzwelt sind Verstärker Oszillatoren, und eigentliche Oszillatoren sind keine…“ VOUT/Vin(s) = H(s)/(1 + H(s)) 26 Oszillation für s = j0, H(j0)=-1 closed loop Verstärkung = für 0 Verstärker verstärkt seine eigene Rauschkomponente bei 0 Barkhausen Kriterium (nicht notwendig, aber hinreichend): | H(j0)| ≥ 1 Arg(H(j0)) 180° o Ringoszillator: Single Common source schwingt nicht, da das Barkhausenkriterium nicht erfüllt ist 90° (1Pol) + 180° (CS-stage) = 270° ≠ 180° 2-Pol-Feedback-System schwingt nicht weil : zwar Phasenlage = 180° ABER pos. Rückkopplung (siehe Grafik) und falls der Winkel stimmt (mit zusätzlicher Signal Inversion) passt |H(j0)| (loop-gain) nicht! LÖSUNG ist eine dritte Stufe, um Phase shift zu erhöhen jede Stufe muss eine Phaseshift von 60° aufweisen damit in Summe ein Winkel von 180° realisiert werden kann 0… -3dB Bandbreite OSC… Frequenz, bei der der Oszillator schwingt arctan(OSC / 0) = 60° OSC = *0 27 o Ringoszillator mit CMOS Inverters: Vorteile: kein Widerstand notwendig, Rail to Rail Swing ist möglich -) Singleended ring Oscillator: ungerade Zahl an Inverter sind notwendig -) Differential Ringoszillator: eine gerade Zahl an Stages ist möglich falls eine Stage nicht invertiert Optimal sind 3 – 5 Stages bezüglich Geschwindigkeit, Energieverbrauch, Rauschunempfindlichkeit o LC Oszillator (Seite 302): Oszillator mit Spule und Kapazität o Voltage Controlled Oscillator (VCO) (Seite 303) : VCO handelt es sich um einen elektrischen Schwingungserzeuger, dessen Frequenz durch die Größe einer anliegenden Spannung (Steuer- oder Regelspannung) verändert werden kann. KVCO ≥ entspricht der Verstärkung Für Versorgungsspannung↓ KVCO↑ Oszillator wird empfindlicher (für geg. 2-1) gegenüber Rauschen bezüglich der Steuerspannung Im Folgenden werden Kombinationen aus VCOs und Ringoszillator bzw VCOs und LC Oszillator verwendet VCO + Ringoszillator: fOSC kann um 4 Größenordnungen variiert werden; bei großen Veränderungen von ISS bleibt ein relativ konstanter Output swing; VCO + LC Oszillator: fOSC = Kapazität (Varactor) realisiert ; L ist const und C wird als spannungsabhängige 28 Dioden in CMOS realisieren (Seite 308) : (a) Anode ist unvermeidlich geerdet (b) Beide Anschlüsse können verwendet werden Integrierte Induktivitäten: (Seite 309 ff) Range für on-chip Induktivitäten: 5 – 25 GHz 5 – 1 nH Mögliche Realisierungen: o Bond wire Inductors: 2 – 5 nH o Planar Spiral inductors: 1 – 8 nH o Multi level spiral inductor (3D): gut für hohe Induktivität pro Fläche o Solenuid Inductors (3D): magn Fluss in einem kleinen Bereich, potentiell am besten mit ferromagn. Kern