D.1 Versuchsreihe 1: Messtechnik

Werbung

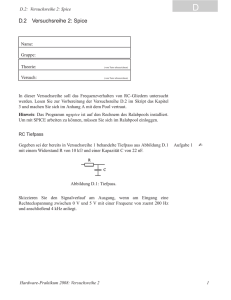

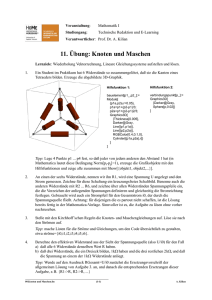

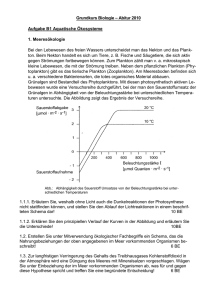

D D.1: Versuchsreihe 1: Messtechnik D.1 Versuchsreihe 1: Messtechnik Name: Gruppe: Theorie: (vom Tutor abzuzeichnen) Versuch: (vom Tutor abzuzeichnen) In dieser Versuchsreihe soll das Frequenzverhalten von RC-Gliedern untersucht werden. Lesen Sie zur Vorbereitung der Versuchsreihe D.1 im Skript das Kapitel 2. Widerstände Diskrete Widerstände sind mit einem Farbcode für den Widerstandswert des Bauelements gekennzeichnet (vergl. Abb. D.1). Die Bedeutung der einzelnen Farbringe ist der nachstehenden Tabelle D.2 zu entnehmen. Aufgabe 1 ✍ Abbildung D.1: Farbcode für Widerstände. Geben Sie die Farbcodierung für die folgenden Widerstände an: 120Ω 82 Ω 30 kΩ Hardware-Praktikum 2008: Versuchsreihe 1 1 D Aufgabe 2 ✍ D.1: Versuchsreihe 1: Messtechnik Geben Sie die Widerstandswerte für die folgenden Farbcodes an: idealer Wert gemessener Wert rot schwarz gelb gold blau grau braun gold braun orange braun gold Tabelle D.1: Widerstände. Farbe keine silber gold schwarz braun rot orange gelb grün blau violett grau weiß Ring 1(1. Ziffer) 1 2 3 4 5 6 7 8 9 Ring 2(2. Ziffer) Ring 3(Multiplik.) 0 1 2 3 4 5 6 7 8 9 10−2 10−1 1 101 102 103 104 105 106 107 108 109 Ring 4(Toleranz) +/- 20% +/- 10% +/- 5% +/- 1% +/- 2% +/- 0.5% +/- 0.25% +/- 0.1% Tabelle D.2: Kodierung von Widerständen mittels Farbringen. Versuch 3 Prüfen Sie mit dem Digitalmultimeter, ob die Widerstände aus Aufgabe 2 den angegebenen Toleranzen genügen und tragen Sie die Messwerte in die Tabelle D.1 ein. In integrierten CMOS Schaltungen treten Widerstände vor allem als parasitäre Elemente auf, die sich aus den Prozessparametern ergeben. Da bei Leiterbahnen und 2 Hardware-Praktikum 2008: Versuchsreihe 1 D.1: Versuchsreihe 1: Messtechnik D Kontakten die Dicke d durch den Prozess vorgegeben ist, erhält man mit ρ als spezifischem Widerstand einen konstanten „Flächenwiderstand“ RA := dρ und bei Länge l und Weite w gilt l l R=ρ· = RA · w·d w Die Flächenwiderstände für verschiedene Materialien werden von IC-Herstellern meist als Technologieparameter zur Verfügung gestellt. Abbildung D.2 zeigt das Layout und die Technologieparameter einer einfachen CMOS Schaltung im Maßstab 5000:1. Der Abstand zwischen beiden CMOS Gattern soll 4 mm betragen und ist aus Platzgründen nicht maßstabsgetreu gezeichnet. Die Kontaktpunkte 3 und 4 bilden die Schaltungseingänge, Kontaktpunkt 7 ist der Schaltungsausgang. Hardware-Praktikum 2008: Versuchsreihe 1 3 D D.1: Versuchsreihe 1: Messtechnik Abbildung D.2: Layout und Technologieparameter einer einfachen CMOSSchaltung. 4 Hardware-Praktikum 2008: Versuchsreihe 1 D.1: Versuchsreihe 1: Messtechnik D Geben Sie die Transistorschaltung an, die das Layout in Abb. D.2 implementiert. Aufgabe 4 ✍ Berechnen Sie den Widerstand der Verbindung zwischen den Punkten 5 und 6 (Leitungswiderstand und Kontaktwiderstände berücksichtigen). Um die Widerstände von Polygonen zu berechnen, kann die in Abbildung D.3 skizzierte Näherungsmethode (Rechteckzerlegung) verwendet werden. Aufgabe 5 ✍ Abbildung D.3: Rechteckzerlegung. Hardware-Praktikum 2008: Versuchsreihe 1 5 D D.1: Versuchsreihe 1: Messtechnik Aufgabe 6 ✍ Berechnen Sie den Gesamtwiderstand für eine leitende Verbindung zwischen den Punkten 1 und 6, wenn für einen leitenden p-MOS Transistor ein Innenwiderstand von 1 kΩ angenommen wird und an den Eingängen 3 und 4 der Wert „0“ (Potential von VSS ) anliegt. Aufgabe 7 ✍ In fehlerfreien CMOS Schaltungen fließt, abgesehen von vernachlässigbaren Leckströmen, kein statischer Strom. Bei der Fertigung von CMOS Schaltungen können jedoch Fehler auftreten, die zu einem erhöhten statischen Strom führen. In der Netzliste aus Aufgabe 4 sei der n-MOS Transistor an Gateanschluss 6 durch einen Fehler ständig leitend. Ersetzen Sie in der Netzliste die Transistoren durch Widerstände und berechnen Sie im erhaltenen Widerstandsnetzwerk alle Teilströme und Teilspannungen für eine Betriebsspannung von 5 V. Für leitende Transistoren wird ein Innenwiderstand von 1 kΩ, für sperrende Transistoren wird ein Innenwiderstand von 10 MΩ angenommen. An beiden Schaltungseingängen liege der Wert „1“ (HIGH) an. 6 Hardware-Praktikum 2008: Versuchsreihe 1 D D.1: Versuchsreihe 1: Messtechnik Stecken Sie auf der Experimentierplatine das in Aufgabe 7 entworfene Widerstandsnetzwerk und legen Sie eine Betriebsspannung von 5 V an. Stellen Sie dazu vorher an der stabilisierten Spannungsquelle eine Spannung von 5 V ein und begrenzen Sie den Strom auf 25 mA. Gehen Sie wie folgt vor: Versuch 8 • Regeln Sie die Ausgangsspannung der Spannungsquelle auf 0 V. • Regeln Sie die Begrenzung des Ausgangstroms der Spannungsquelle auf 0 A. • Wählen Sie am Digitalmultimeter (DMM) den Messbereich 20 V DCV (Direct Current Voltage=Gleichspannung). • Stecken Sie die schwarze Messleitung in die Buchse COM am DMM. • Stecken Sie die rote Messleitung in die Buchse V/Ω am DMM. • Verbinden Sie die schwarze Messleitung mit dem Minuspol der Spannungsquelle. • Verbinden Sie die rote Messleitung mit dem Spannungsausgang der Spannungsquelle. • Regeln Sie langsam die Spannung an der Spannungsquelle auf 5 V ein. • Wählen Sie am zweiten Digitalmultimeter (DMM) den Messbereich 200 mA DCA (Direct Current Ampere = Gleichstrom) • Stecken Sie die schwarze Messleitung in die Buchse COM am DMM. • Stecken Sie die rote Messleitung in die Buchse A am DMM. • Verbinden Sie die schwarze Messleitung mit der Masse der Spannungsquelle. • Verbinden Sie die rote Messleitung mit dem Spannungsausgang der Spannungsquelle. • Regeln Sie langsam den Strom an der Spannungsquelle auf 25 mA ein. Messen Sie mit den Digitalmultimetern Teilströme und Spannungen und tragen Sie die Messwerte ins Versuchsprotokoll ein. Hardware-Praktikum 2008: Versuchsreihe 1 7 D Aufgabe 9 D.1: Versuchsreihe 1: Messtechnik ✍ Warum können Sie die Widerstände im Netzwerk nicht direkt messen? Kapazitäten Aufgabe 10 ✍ Gegeben sei das RC-Glied aus Abbildung D.4 (Tiefpass) mit einem Widerstand R von 10 kΩ und einer Kapazität C von 22 nF. Abbildung D.4: RC-Glied. Berechnen Sie die Zeitkonstante τ und skizzieren Sie den Signalverlauf am Ausgang, wenn am Eingang eine Rechteckspannung zwischen 0 V und 5 V mit einer Frequenz von 200 Hz anliegt. Aufgabe 11 8 ✍ Für das RC-Glied aus Aufgabe 10 sollen die Signallaufzeiten untersucht werden. Anstiegszeit, Abfallzeit und Verzögerungszeit eines Signals sind wie in Abbildung D.5 definiert. Die Verzögerungszeit beschreibt die Zeitdauer zwischen dem Zeitpunkt, an dem das Eingangssignal 50% Spannung erreicht, und dem Zeitpunkt, zu dem das Ausgangssignal 50% der Spannung erreicht (in Abbildung D.5 wird angenommen, dass das Eingangssignal die halbe Versorgungsspannung zum Zeitpunkt „0“ erreicht). Hardware-Praktikum 2008: Versuchsreihe 1 D.1: Versuchsreihe 1: Messtechnik D Berechnen Sie die Verzögerungszeit td für das RC-Glied aus Aufgabe 10. Es wird ein ideales Eingangssignal mit einer Anstiegszeit von 0 ns angenommen. Abbildung D.5: Charakteristische Größen von Signalen. Das Verhalten des RC-Glieds aus Aufgabe 10 soll experimentell überprüft werden. Bauen Sie hierzu auf der Experimentierplatine das RC-Glied aus Aufgabe 10 auf. Versuch 12 Stellen Sie am Funktionsgenerator eine Rechteckspannung mit einer Frequenz von f = 200 Hz ein. Gehen Sie dazu wie folgt vor: • Schalten Sie den Funktionsgenerator ein. Der Funktionsgenerator zeigt im Display die Signalform Sinus an (SINE). • Drücken Sie den Taster „>“ so oft, bis im Display die Signalform Rechteck (SQUARE) angezeigt wird. • Drücken Sie den Taster „Range/Attn“. Mit den Tastern „<“ und „>“ können Sie nun den Frequenzbereich vorwählen. Wählen Sie den Bereich „Range: 20-200“. • Drücken Sie wiederholt den Taster „Sub Func“ , bis im Display die Funktion „4. DC Offset: Off“ angezeigt wird. • Drücken Sie den Taster „>“ , um ein Offset zu ermöglichen. Im Display erscheint die Anzeige „4. DC Offset: On“. Hardware-Praktikum 2008: Versuchsreihe 1 9 D D.1: Versuchsreihe 1: Messtechnik • Stellen Sie mit dem Regler „Frequency“ die Frequenz von 200 Hz ein. Überprüfen Sie die Einstellungen mit Hilfe des Oszilloskops. Gehen Sie dazu wie folgt vor: • Schalten Sie das Oszilloskop ein. • Verbinden Sie den Ausgang „Func Out“ des Funktionsgenerators mit dem Eingang „Input CHI“ des Oszilloskops. • Drücken Sie den Taster „Auto Set“ am Oszilloskop. Damit wird das Oszilloskop automatisch eingestellt. • Auf dem Schirm sollte ein symmetrisches Rechtecksignal dargestellt werden. • Drücken Sie den Taster „AC/DC“ neben dem Eingang „Input CHI“ des Oszilloskops. Damit messen Sie Gleichspannungen. • Die Tastköpfe der Oszilloskope teilen das Eingangssignal im Verhältnis 1:10, d. h. am Oszilloskop werden nur 10% der Eingangsspannung gemessen. Berücksichtigen Sie dies bei der Wahl des Verstärkungsfaktors am Oszilloskop. Stellen Sie den Funktionsgenerator so ein, dass das Ausgangssignal zwischen 0 und 5 V schwingt. Gehen Sie dazu wie folgt vor: • Stellen Sie mit dem Regler Amplitude am Funktionsgenerator eine SpitzeSpitze-Spannung VP P =5 V ein. Am Oszilloskop wird die Spannung abgelesen. • Benutzen Sie den Regler DC Offset am Funktionsgenerator, um das Signal in den Spannungsbereich zwischen 0 und 5 V zu verschieben. Am Oszilloskop wird eine Parallelverschiebung des Signals sichtbar. Nehmen Sie mit dem Oszilloskop das Eingangs- und Ausgangssignal des RCGliedes für die Frequenz 200 Hz auf. Skizzieren Sie das Schirmbild des Oszilloskops. 10 Hardware-Praktikum 2008: Versuchsreihe 1 D.1: Versuchsreihe 1: Messtechnik Bestimmen Sie Anstiegs- und Abfallzeit des Signals (tr und Abfallzeit tf ) und protokollieren Sie Ihre Messwerte. tr D Versuch 13 tf Hardware-Praktikum 2008: Versuchsreihe 1 11 D D.1: Versuchsreihe 1: Messtechnik Mit Hilfe von RC-Gliedern (vgl. Abb. D.4) lassen sich eine Reihe von Effekten in CMOS Schaltungen wie etwa parasitäre Effekte von Verbindungsleitungen oder die Frequenzabhängigkeit des Schaltverhaltens modellieren. Wenn die Verbindungsleitungen zunächst vernachlässigt werden, kann das Verhalten von CMOS Gattern, deren Ausgänge weitere Gatter treiben, mit dem Ersatzschaltbild in Abbildung D.6 erklärt werden. Abbildung D.6: Ersatzschaltbild eines Gatters mit kapazitiver Last. Die Widerstände repräsentieren die Pull-Up und Pull-Down Netze des Gatters, die Kapazität CLast die Gatekapazitäten nachfolgender Gatter (die Gatekapazität setzt sich zusammen aus den Kapazitäten Gate/Source, Gate/Drain und Gate/Substrat). Verbindungsleitungen können wie in Abbildung D.7.a als Tiefpass modelliert werden, wobei der Widerstand den Leitungswiderstand und der Kondensator die Kapazität zwischen Leiterbahn und Substrat beschreibt. Ein noch genaueres Modell liefert die Zerlegung in Teilstücke (vgl. Abbildung D.7.b). Abbildung D.7: Modellierung einer Verbindungsleitung. Halbleiterhersteller geben meist einen Prozessparameter, die Flächenkapazität an, welche die Kapazität einer Verbindungsleitung für eine Flächeneinheit näherungsweise beschreibt (vergl. Abbildung D.2). In diesen Parameter gehen auch die Streukapazitäten zu anderen Leitungen ein. Zur Ermittlung der Leitungskapazität muss die Fläche der Leitung mit dem Parameter Flächenkapazität multipliziert werden. 12 Hardware-Praktikum 2008: Versuchsreihe 1 D.1: Versuchsreihe 1: Messtechnik D Berechnen Sie für das Layout aus Abbildung D.2 die Kapazität von Knoten 5, d. h. die Kapazität der an Kontakt 5 angeschlossenen Verbindungsleitung (es brauchen nur die Anteile berücksichtigt zu werden, die über Substrat liegen). Aufgabe 14 ✍ Modellieren Sie eine leitende Verbindung zwischen den Punkten 1 und 6 als RCGlied (vgl. Abb. D.7.a) und berechnen Sie die Zeitkonstante τ . Für einen leitenden Transistor wird ein Innenwiderstand von 1 kΩ angenommen. Bedenken Sie, dass auch das Gate am Knoten 6 umgeladen wird. Aufgabe 15 ✍ Skizzieren Sie den Signalverlauf am Ausgang des RC-Glieds aus Aufgabe 15 unter der Annahme einer 200 MHz Rechteckspannung am Eingang (Amplitude zwischen 0 V und 5 V). Aufgabe 16 ✍ Hardware-Praktikum 2008: Versuchsreihe 1 13 D Aufgabe 17 Versuch 18 14 D.1: Versuchsreihe 1: Messtechnik ✍ Mit Hilfe der Modellierung als RC-Glied lassen sich die Signallaufzeiten für die Verbindung aus Aufgabe 15 untersuchen. Berechnen Sie die Verzögerungszeit td für die leitende Verbindung aus Aufgabe 15. Es wird ein ideales Eingangssignal mit einer Anstiegszeit von 0 ns angenommen. Schalten Sie alle Geräte bis auf den Rechner aus. Überprüfen Sie, ob alle Leitungen, Multimeter und Tastköpfe aufgeräumt sind. Stellen Sie die Stühle an die Tische und vergewissern Sie sich nochmals, dass der Platz in ordnungsgemäßem Zustand ist. Lassen Sie bitte keinen Unrat unter den Tischen stehen! Hardware-Praktikum 2008: Versuchsreihe 1