PDF-File - Otto-von-Guericke

Werbung

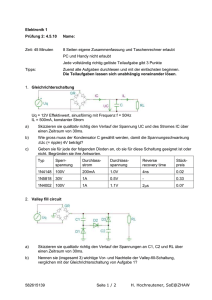

Otto-von-Guericke-Universität Magdeburg Fakultät für Naturwissenschaften Institut für Experimentelle Physik Praktikum „Elektrotechnik und Elektronik für das Lehramt“ und „Elektronik“ für den Studiengang Physik (B.Sc.) Inhaltsverzeichnis Analoge Schaltungen Versuch 1 Messungen mit dem Oszillographen 1.1 Wechselspannungsmessungen 1.2 Kapazitiver Wechselstromwiderstand 1.3 RC-Spannungsteiler: Tiefpass 1 1 1 2 Versuch 2 Verstärkerschaltungen mit Bipolartransistoren 2.1 Eigenschaften eines npn-Bipolartransistors 2.2 Methoden der Arbeitspunkteinstellung beim Transistor 3 3 Versuch 3 Operationsverstärker 3.1 Grundlegende Schaltungen 6 6 Versuch 4 Anwendungen des Operationsverstärkers 4.1 Differenzverstärker mit gewichteten Eingängen 4.2 Nichtinvertierender Verstärker 4.3 Differenziator und Integrator 4.4 Logarithmierer 3 8 8 9 10 11 Digitale Schaltungen Versuch 5 Kombinatorische Logikschaltungen 5.1 Eigenschaften von TTL-Logikbausteinen 5.2 Einfache logische Funktionen 5.3 Dekoderschaltungen 5.4 4-nach-1-Multiplexer 12 12 13 14 15 Versuch 6 Rückgekoppelte Logikschaltungen 6.1 Bistabile Kippschaltung (Flip-Flop) 6.2 Instabile Kippschaltungen 16 16 17 Versuch 7 Zähler und Schieberegister 7.1 JK-Flip-Flop 7.2 Asynchronzähler 7.3 Synchronzähler 7.4 Schieberegister 19 19 19 20 22 Versuch 8 Digital/Analog- und Analog/Digital- Wandler 8.1 Digital/Analog- Wandler 8.2 Analog/Digital- Wandler • Nachlaufverfahren • SAR • Dual slope 23 23 24 24 26 28 Versuch 9 Multiplikation und Division von Dualzahlen 9.1 Serielle Multiplikation 9.2 Serielle Division 31 31 34 Anhang 38 Hinweise sowie Anschlussbelegungen der verwendeten Bauteile Analoge Schaltungen Versuch 1 Messungen mit dem Oszillographen Vorbereitung: Lesen Sie nach, wie ein Oszillograph prinzipiell aufgebaut ist und versuchen Sie, anhand der Gerätebeschreibung die Funktion der Bedienelemente zu verstehen. Eignen Sie sich die Grundlagen über Wechselspannungen, komplexe Widerstände sowie den Tiefpass an. Versuch 1.1 Wechselspannungsmessungen Bestimmen Sie die Amplitude U0, Periodendauer T und Frequenz f einer Sinusschwingung mit Hilfe des Oszillographen. Machen Sie sich dabei mit der Wirkung der einzelnen Bedienelemente des Oszillographen vertraut. Multimeter Oszillograph Funktionsgenerator Vergleichen Sie die ermittelte Frequenz mit der Anzeige des Funktionsgenerators. Wie genau ist die Frequenzbestimmung (Spezifikation nachschlagen!)? Vergleichen Sie die verschiedenen angezeigten Werte. Woher kommt der Unterschied? Schalten Sie nun den Generator auf Dreieck- und Rechteckspannung um und vergleichen Sie wieder die verschiedenen angezeigten Werte. Versuch 1.2 Kapazitiver Wechselstromwiderstand Ermitteln Sie den Wechselstromwiderstand eines Kondensators mit dem Oszillographen im 2-Kanalbetrieb im Frequenzbereich ω=2πf= 2kHz…2MHz. Die Amplitude ist so zu wählen, dass der Übertrager nicht verzerrt (<1V). Warum ist die galvanische Trennung von Funktionsgenerator und Oszillograph durch den Übertrager notwendig? -1- Übertrager 1:1 Wie groß ist die Phasenverschiebung zwischen Spannung und Strom? Hängt diese von der Frequenz ab? Zeichnen Sie das Diagramm Xc(ω) im doppeltlogarithmischen Maßstab. Welchen Zusammenhang zwischen Xc und ω lesen Sie daraus ab? Versuch 1.3 RC-Spannungsteiler: Tiefpass Messen Sie die Frequenzabhängigkeit der Amplitude A(f) eines Tiefpasses. Zeichnen Sie dazu den Amplitudengang A(f) im doppelt-logarithmischen Maßstab (Bode-Diagramm). Ermitteln Sie aus dem Diagramm die 3dBGrenzfrequenz. Schalten Sie den Generator auf Rechtecksignal um und beobachten Sie die Signalform am Tiefpassausgang für verschiedene Frequenzen unterhalb und oberhalb der Grenzfrequenz. -2- Versuch 2 Verstärkerschaltungen mit Bipolartransistoren Vorbereitung: Lesen Sie nach, wie Bipolartransistoren aufgebaut sind, welche Eigenschaften sie besitzen, welche Ein- und Ausgangskennlinien typisch für diese Transistoren sind. Informieren Sie sich weiterhin, welche Eigenschaften die Grundschaltungen des Bipolartransistors besitzen und welche Methoden der Arbeitspunkteinstellung möglich sind. Führen Sie die in den Versuchen verlangte Dimensionierung durch. Bereiten Sie die in den Versuchen zu erstellenden Messdiagramme vor. Versuch 2.1 Eigenschaften eines npn-Bipolartransistors Messen Sie die statische Stromverstärkung B des npn-Bipolartransistors BCY58 für eine konstante Kollektor-Emitterspannung UCE = 10V. + - + - Bestimmen Sie B für fünf verschiedene Basisströme im Bereich IB = 3μA … 40μA und messen Sie die dazu gehörende Basis-Emitterspannung UBE. Bei welchem Kollektorstrom IC beginnt das Transistorgehäuse spürbar warm zu werden? Berechnen Sie die im Transistor dissipierte elektrische Leistung Pdiss für diese Messpunkte. Welche Temperatur wird dabei erreicht? Der thermische Widerstand zwischen Transistorgehäuse und umgebender Luft beträgt Rϑ = 0,5K/mW. Versuch 2.2 Methoden der Arbeitspunkteinstellung beim Transistor a) Arbeitspunkteinstellung durch Einprägen des Basisstromes IB Verwenden Sie den Transistor BCY58 aus Teilversuch 2.1 mit dem von Ihnen ermittelten Stromverstärkungsfaktor B. -3- + - Bei einer Betriebsspannung UB = 10V und einem Kollektorwiderstand von RC = 2,2kΩ soll die „Ausgangsspannung“ UCE = 6V betragen. Berechnen Sie den für diesen Arbeitspunkt notwendigen Basiswiderstand RB und bauen Sie die Schaltung auf. Messen Sie UCE und bestimmen Sie den Kollektorstrom IC. Erwärmen Sie jetzt den Transistor mit zwei Fingern und beobachten Sie dabei das Verhalten von UCE. Tauschen Sie den Transistor gegen ein anderes Exemplar vom gleichen Typ aus und messen Sie wieder UCE. Wie bewerten Sie danach die Eigenschaft dieser Methode der Arbeitspunkteinstellung bezüglich Stabilität und Exemplarstreuung? b) Arbeitspunkteinstellung durch Einprägen der Basis-Emitter-Spannung UBE Dimensionieren Sie die Schaltung für die folgenden Werte: UB = 10V, UCE = 5V, RC = 2,2kΩ und R1 = 10kΩ. RC + - Bauen Sie die Schaltung auf und messen Sie UBE, IB, UCE und IC. Vergleichen Sie die berechneten und die gemessenen Werte miteinander. Welchen Einfluss haben die Strommessgeräte? Erwärmen Sie wiederum den Transistor bzw. tauschen Sie Ihn aus und beobachten Sie dabei die Änderung von UCE. Bewerten Sie die Stabilitätseigenschaften dieser Schaltung. -4- c) Arbeitspunkteinstellung durch Stromgegenkopplung Ergänzen Sie jetzt die Schaltung durch Einfügen eines Emitterwiderstandes RE, der eine Stromgegenkopplung bewirkt. RC + - Dimensionieren Sie die Schaltung für folgende Parameter: UB = 10V, UCE = 5V, IC = 2mA und RC = 2,2kΩ. Wie groß muss RE sein? Messen Sie dazu die folgenden Größen: UBE, UCE, IB und IC. Merke: Zum Test eines Transistors im leitenden Betrieb immer zuerst UBE messen. Wie groß muss UBE bei einem Si-Transistor ungefähr sein? Wie gut stimmen diese Werte mit den berechneten überein? Prüfen Sie jetzt die Stabilität der Arbeitspunkteinstellung gegenüber Temperaturschwankungen und Exemplarstreuungen (Transistor auswechseln!) und vergleichen Sie das Ergebnis qualitativ mit den Ergebnissen der Teilversuche a) und b). -5- Versuch 3 Operationsverstärker Vorbereitung: Machen Sie sich mit den Eigenschaften eines Operationsverstärkers vertraut. Informieren Sie sich über Gegenkopplungsmethoden und über die Berechnung von gegengekoppelten Operationsverstärkerschaltungen. Machen Sie sich klar, welche Eigenschaften den idealen Operationsverstärker charakterisieren. Welche Merkmale weist der ideale Operationsverstärker auf? Versuch 3.1 Grundlegende Schaltungen Hinweis: Grundsätzlich werden die Anschlüsse der Betriebsspannungen UB+ und UBnicht in die Schaltungen gezeichnet, da deren Anschluss Grundvoraussetzung für den Betrieb ist (s. Skizze). UB+ = +15V Offset UE- UB+ UE+ UA UB- Offset UEUE+ UA UB- = -15V a) Invertierender Verstärker Bauen Sie einen invertierenden Verstärker mit Hilfe eines integrierten Differenzverstärkers sehr hoher Verstärkung (Operationsverstärker) auf. UB+ = +15V UEUe UA UE+ Ua UB- = -15V Messen Sie die Verstärkung und überlegen Sie sich die Wirkungsweise der Gegenkopplung. Überzeugen Sie sich davon, dass die Spannung UEunabhängig von der Eingangsspannung Ue gleich UE+ ist (virtueller Nullpunkt). -6- Welche Ausgangsspannung erhält man, wenn man den Gegenkopplungswiderstand entfernt? Welche Eigenschaften des Operationsverstärkers sind dafür verantwortlich? Berechnen Sie wie groß der Gegenkopplungswiderstand für eine andere Verstärkung, die Sie selbst festlegen können, ist. Welche Freiheit besteht bei der Wahl der Widerstände? Messen Sie die Verstärkung der veränderten Schaltung und vergleichen Sie den berechneten mit dem experimentell bestimmten Wert. Was geschieht, wenn in der oben angegebenen Schaltung der Eingang E+ des Operationsverstärkers offen gelassen wird? Warum ist es mit der angegebenen Schaltung nicht einfach möglich, durch Vertauschen der beiden Eingänge einen nichtinvertierenden Verstärker aufzubauen? b) Schmitt-Trigger Zeigen Sie, dass die Schaltung mit „vertauschten“ Eingängen die Eigenschaften eines Schwellwertschalters (Schmitt-Trigger) besitzt. 10k R2 1k R1 Ue Ua Beobachten Sie dazu den Kurvenverlauf am Schaltungsausgang mit dem Oszillographen, wenn am Eingang die Spannung langsam erhöht wird. Skizzieren Sie das Schirmbild des Oszillographen (Eingangs- und Ausgangsspannung). Messen Sie zusätzlich Ua als Funktion von Ue, indem Sie den Oszillographen im XY-Betrieb betreiben. Sie können dann die Schalthysterese beobachten. Bei welchem Spannungswert liegt die Schaltschwelle? Ändern Sie die Schaltschwelle des Schmitt-Triggers durch Variation des 1kΩ-Widerstandes. -7- Versuch 4 Anwendungen des Operationsverstärkers Vorbereitung: Lesen Sie nach, welche Arten der externen Beschaltung eines Operationsverstärkers möglich sind, welche Eigenschaften diese Schaltungen dann besitzen und wie die Schaltungen zu dimensionieren sind. Führen Sie diese Berechnungen an den vorgegebenen Schaltungen durch. Befassen Sie sich damit, welche Unterschiede zwischen einem idealen und einem realen Operationsverstärker bestehen, wenn die Eigenschaften eines realen Operationsverstärkers berücksichtig werden müssen und wie gegebenenfalls diese Eigenschaften schaltungstechnisch kompensiert werden können. Versuch 4.1 Differenzverstärker mit gewichteten Eingängen Zeigen Sie, dass die folgende Schaltung ein Differenzverstärker mit unterschiedlich gewichteten Eingängen ist. Messen Sie dazu die Ausgangsspannung in Abhängigkeit von der Eingangsspannung getrennt für beide Eingänge, indem Sie den jeweils nicht benötigten Eingang auf Masse legen. Geben Sie die Verstärkung bezüglich der Eingänge E1 und E2 an. Formulieren Sie anschließend die Ausgangsfunktion A (E1, E2) in Abhängigkeit beider Eingänge. Messen Sie diesen Zusammenhang für E1 = +E2 und E1 = -E2 nach. -8- Versuch 4.2 Nichtinvertierender Verstärker Bauen Sie mit einem Operationsverstärker einen nichtinvertierenden Verstärker auf. Ue Ua R1 R2 = 220 Dimensionieren Sie die Schaltung durch R1 so, dass sie eine Verstärkung von V = 10 hat. Messen Sie die Gleichspannungsverstärkung. Nutzen Sie hierzu die OffsetEinstellung am Funktionsgenerator bei ausgeschalteter Wechselspannung. Versuchen Sie, den Eingangswiderstand zu bestimmen. Machen Sie sich auf Grund dieses Ergebnisses klar, warum die angegebene Schaltung den Namen „Elektrometerverstärker“ besitzt. Erhöhen Sie die Verstärkung auf V = 50 durch Änderung von R1. Beobachten Sie das Frequenzverhalten durch Ansteuerung mit einem Rechtecksignal (f=10kHz). Wie ändert sich die Kurvenform am Verstärkerausgang, wenn die Ausgangsspannung Ua von ca. 1VSS auf ca. 20 VSS erhöht wird? Skizzieren Sie die beobachteten Kurvenformen. Wie groß ist also die maximale zeitliche Änderung der Ausgangsspannung („slew rate“)? Erhöhen Sie die Verstärkung der Schaltung auf V = 330, und messen Sie die Ausgangsspannung für UE = 0V. Berechnen Sie daraus die EingangsOffsetspannung. Überlegen Sie, welche Möglichkeiten zur Kompensation dieser Spannung denkbar sind. Wählen Sie die angegebene Methode, welche die am Operationsverstärker vorhandenen Kompensationseingänge benutzt. Ue Ua R1 R2 -9- Versuch 4.3 Differenziator und Integrator Untersuchen Sie in den beiden folgenden Teilversuchen die Eigenschaften frequenzabhängig gegengekoppelter Operationsverstärker im Zeitbereich. Beobachten Sie dazu jeweils den Ausgang der Schaltung bei einer Ansteuerung mit einer Sinus-, Dreieck- und Rechteckspannung. a) Umkehr-Differenziator (f=500Hz) Ue Ua Welchen Einfluss hat der Innenwiderstand der Signalquelle auf den nutzbaren Frequenzbereich der Schaltung? Prüfen Sie dies durch Erhöhen des Innenwiderstandes des Signalgenerators, indem Sie einen Widerstand von 10kΩ zwischen den Funktionsgenerator und dem Schaltungseingang einfügen. b) Umkehrintegrator (f=100Hz) Ue Ua Welche Funktion hat der zum Kondensator parallel geschaltete Widerstand? Zur Beantwortung dieser Frage können Sie den Eingang der Schaltung auf Masse legen, den Parallelwiderstand entfernen und den Ausgang mit einem empfindlichen Voltmeter beobachten. Welche Eigenschaft des realen Operationsverstärkers ist verantwortlich für diesen Effekt? - 10 - Versuch 4.4 Logarithmierer Zur Einengung der Dynamik einer Messgröße verwendet man oft den Logarithmus einer Größe (dB-Skala!). Es kann deshalb vorteilhaft sein, direkt den Logarithmus einer Größe zu messen. Man bedient sich hierzu Schaltungen, deren Gegenkopplung einen nichtlinearen Widerstand mit exponentieller Kennlinie enthält. Eine Halbleiterdiode besitzt im Durchlassbereich eine solche exponentielle Abhängigkeit. Bauen Sie die Schaltung auf und prüfen Sie deren Funktionsweise, in dem Sie Ua in Abhängigkeit von Ue messen und anschließend den Zusammenhang Ua (Ue) in einem Diagramm (einfach log. Darstellung) graphisch darstellen. Ue Ua - 11 - Digitale Schaltungen Versuch 5 Kombinatorische Logikschaltungen Vorbereitung: Welche logischen Grundverknüpfungen gibt es und welche Beziehungen bestehen zwischen diesen? Lernen Sie den Umgang mit einer Funktionstabelle („Wahrheitstabelle“) und einem KARNAUGH-Diagramm. Informieren Sie sich, wie Logikschaltungen, speziell in TTL-Technik, realisiert sind und welche Eigenschaften diese Schaltkreise besitzen. Welche Spannungspegel sind den logischen Zuständen zugeordnet? Lesen Sie nach, wie LEDs prinzipiell funktionieren und wie die im Praktikum verwendeten Anzeigemodule zu beschalten sind. Machen Sie sich außerdem mit der binären und der hexadezimalen Zahlendarstellung vertraut. Versuch 5.1 Eigenschaften von TTL-Logikbausteinen a) Prüfen Sie die Funktion eines TTL-Gatters 74 LS 00 (NAND für positive Logik) durch jeweiliges Verbinden der Eingänge mit VCC -Potential (+5V) bzw. Masse. Tragen Sie das Ergebnis in eine Funktionstabelle ein. Der Ausgang soll mit einem Voltmeter und dem LED-Modul beobachtet werden. Bei welchem Eingangspotential leuchtet das LED-Modul? Welchem logischen Zustand entspricht dies? Wie groß ist der Gattereingangsruhestrom für die beiden Eingangspotenziale zusammen? VCC 14 E1 E2 7 b) Überprüfen Sie für einen Eingang eines Gatters, welcher Spannungsbereich für die beiden logischen Zustände erlaubt ist (den anderen Eingang auf Vcc = +5V legen). Oszillographieren Sie dazu im XY-Betrieb! Übertragen Sie das beobachtete Bild in ein Diagramm (Übertragungskennlinie). Zeichnen Sie in das Diagramm die definierten TTL-Pegel für die Eingänge und den Ausgang ein. - 12 - Versuch 5.2 Einfache logische Funktionen Berechnen Sie mit Hilfe der Regeln der Schaltalgebra die Ausgangsfunktion folgender Schaltungen und prüfen Sie anschließend experimentell Ihre Rechnung nach. a) OR-Funktion aus NAND-Gattern A1 E1 A3 A2 E2 Als Zwischenschritt sollten auch die Zustände an den Punkten A1 und A2 in die Tabelle aufgenommen werden. b) XOR-Funktion (Exclusive-OR bzw. Antivalenzfunktion) aus NAND –Gattern A2 E1 A1 A4 E2 A3 - 13 - Überlegen Sie, welcher Teil eines Halbaddierers für 1-Bit-Dualzahlen (ohne Übertrag der vorhergehenden Stelle) mit dieser Schaltung verwirklicht ist. Ergänzen Sie die Schaltung zu einem Halbaddierer mit je einem Ausgang für die Summe (∑) und den Übertrag (CO). Versuch 5.3 Dekoderschaltungen a) Eine 2-Bit-Dualzahl (angegeben durch E1 und E2) soll dekodiert werden, dass für jede Zahl genau ein Ausgang der Schaltung aktiviert wird (1-aus-4-Dekoder). Bauen Sie die Schaltung auf, testen Sie deren Funktion und ermitteln Sie die Funktionstabelle. Welcher Ausgangszustand ist dabei der aktive? E2 E1 b) Für viele praktische Anwendungen sind binärkodierte Dezimalzahlen (BCDZahlen) besonders wichtig. Ein häufig auftretendes Problem ist deshalb die direkte Anzeige einer solchen Zahl (z.B. in Digitalmultimetern, etc.). Meist bedient man sich dabei einer 7-Segment- Anzeige. Die Dezimalzahl wird durch geeignete Kombinationen von leuchtenden und nichtleuchtenden Segmenten dargestellt. Überzeugen Sie sich, wie die Zuordnung der Dezimalzahl zur Dualzahl und zu den Anzeigesegmenten der verwendeten 7-Segment-Anzeige erfolgt, indem Sie die vier Eingänge des LED-Moduls und der 7-Segment-Anzeige parallel schalten und an den jeweiligen Eingängen die der Dualzahl entsprechenden Pegel anlegen (Bsp.: „1“ 0001 L L L H ). Achten Sie dabei auf die BitWertigkeit. Vervollständigen Sie dann die nachfolgende Tabelle. Achten Sie auf die Pseudotetraden. - 14 - Dezimalzahl Dualzahl MSB 7-Segment-Anzeige LSB 0 0000 1 0001 2 0010 … … … 15 1111 (?) Versuch 5.4 4-nach-1-Multiplexer Bauen Sie einen 4-nach-1-Multiplexer auf, der in Abhängigkeit von den Pegeln an den Steuereingängen A0 und A1 die Dateneingänge D0 … D3 zum Ausgang Q durchschaltet. Die in der Schaltung angegebenen AND- bzw. OR-Funktionen mit jeweils 4 Eingängen sind dabei mit Hilfe von 4-fach-NAND-Gattern zu realisieren. Nutzen Sie dazu den Schaltkreis 74 LS 20. Zeichnen Sie die Schaltung entsprechend um und testen Sie diese. Ermitteln Sie die Funktionstabelle der Multiplexerschaltung (Ausgang Q in Abhängigkeit von den Steuer- und den Dateneingängen). A0 A1 D0 D1 D2 D3 - 15 - Versuch 6 Rückgekoppelte Logikschaltungen Vorbereitung: Welche Eigenschaften besitzen die rückgekoppelten Logikbausteine RS-Flip-Flop und D-FlipFlop? Erläutern Sie die Funktionsweise eines Pulsformers (Impulsverkürzer) und eines Toggle-Flip-Flops. Wie lassen sie sich realisieren? Hinweis: Achten Sie beim Schaltungsbau auf kurze Verbindungsleitungen, d. h. verwenden Sie möglichst feste Brücken, um einen übersichtlichen Versuchsaufbau zu gewährleisten. Versuch 6.1 Bistabile Kippschaltung (Flip-Flop) a) Bauen Sie ein RS-Flip-Flop aus integrierten NAND-Gattern auf. Ermitteln Sie die Funktionstabelle dieser Schaltung für die Ausgänge Q und Q. Bei welcher Eingangswahl sind beide Ausgänge gleich und also eigentlich falsch bezeichnet? Was geschieht, wenn man diesen Zustand verlässt? b) Erweitern Sie das RS-Flip-Flop zu einem transparenten D-Latch. Ermitteln Sie R und S für die vier Eingangskombinationen von D und CLK. Überzeugen Sie sich, dass bei CLK = 1 der Eingang D nach Q übertragen wird. Was geschieht, wenn während dieser Zeit D geändert wird? Welcher Zustand wird also gespeichert? (Verwenden Sie für diesen Versuch die entprellte Taste an CLK.) c) Erweitern Sie das transparente D-Latch zu einem D-Flip-Flop, das D nur an einer Flanke des Taktes übernimmt. Bauen Sie zunächst hierfür folgende Schaltung eines Pulsformers (Impulsverkürzer) auf: - 16 - A Überzeugen Sie sich, dass die Schaltung aus einer negativen Flanke (H L) von T einen kurzen positiven bzw. negativen Puls erzeugt. Die hierzu angewandte Methode verstehen Sie, wenn Sie T an den TTL-Ausgang des Funktionsgenerators legen und beide Eingänge des Gatters A gleichzeitig mit dem Oszillographen beobachten. Was geschieht bei der anderen Flanke? Welche Dauer hat der erzeugte Puls am Ausgang des Gatters A? Welche Bauteile bestimmen die Pulsdauer? Verändern Sie die Pulsdauer durch Variation von C. Verbinden Sie jetzt den kurzen positiven Impuls mit dem Takteingang CLK des D-Latch aus Teilaufgabe b). Benutzen Sie am Pulsformereingang die entprellte Taste. Überzeugen Sie sich, dass der Wert am Eingang D nur zur Zeit der aktiven Flanke übernommen wird, zu allen anderen Zeiten D dagegen keinen Einfluss auf Q hat. (Der Pulsformer wird nochmals für Versuch 6.2 b benötigt.) d) Industriell wird das D-Flip-Flop z.B. im integrierten Schaltkreis 74 LS 74 (einflankengetriggertes zweifach D-Flip-Flop) als Master-Slave-Flip-Flop angeboten. Realisieren Sie mit Hilfe dieses Schaltkreises ein Toggle-Flip-Flop. Verbinden Sie hierzu Q mit D und takten Sie das T-Flip-Flop mit der entprellten Taste. Benutzen Sie anstelle der entprellten Taste auch den TTL-Ausgang des Funktionsgenerators. Hinweis: Bleiben die Eingänge S1 und S2 des 74 LS 74 (wie in diesem Fall) unbeschaltet, sind diese für den störungsfreien Betrieb auf High zu legen. Versuch 6.2 Instabile Kippschaltungen a) Erfolgt die Rückkopplung beim RS-Flip-Flop nicht galvanisch, sondern über einen Hochpass, dann „kippt“ die Schaltung ständig von einem Zustand in den anderen (astabile Kippschaltung, Multivibrator). Wenn Sie die Schaltung unter Spannung setzen, schwingt sie möglicherweise nicht von selbst an. Öffnen Sie dann kurz die Verbindung S. Überlegen Sie, wie die Rückkopplung wirkt und messen Sie mit dem Oszillographen die Spannung an den Punkten C und Q. Wodurch ist die Zeitkonstante des Multivibrators bestimmt? - 17 - S b) Erfolgt nur eine Rückkopplung über einen Hochpass, die andere dagegen galvanisch, so erhält man eine monostabile Kippschaltung (Mono-Flop): C Bauen Sie die Schaltung auf und überlegen Sie, welcher Zustand der Schaltung stabil und welcher instabil ist. Wovon hängt die „Lebensdauer“ des instabilen Zustandes ab? Wie kann der instabile Zustand ausgelöst werden? Welchen Zustand muss CLK nach Auslösung des instabilen Zustandes (Triggerung) annehmen? Triggern Sie das Mono-Flop mit einem „Pulsgenerator“. Der sich aus dem Funktionsgenerator (f=2kHz) mit nachgeschaltetem Pulsformer (s. Versuch 6.1 c) zusammensetzt. Welchen Ausgang des Pulsformers müssen Sie benutzen? Skizzieren Sie den Spannungsverlauf an den Punkten CLK, Q und C. Verändern Sie die Generatorfrequenz. - 18 - Versuch 7 Zähler und Schieberegister Vorbereitung: Informieren Sie sich über flankengesteuerte Flip-Flops, Asynchron- und Synchronzähler sowie über Schieberegister. Versuch 7.1 JK-Flip-Flop Der integrierte Baustein 74 LS 107 enthält zwei JK-Flip-Flops, die in sich die Funktion des D- und des T-Flip-Flops vereinigen. Bestimmen Sie die Funktionstabelle des JK-Flip-Flops (Ausgang Q und Q als Funktion von J und K). Verwenden Sie zur Taktung die entprellte Taste und beobachten Sie, bei welcher Flanke der Zustand der Ausgänge sich ändert. Beachten Sie besonders das Verhalten der Schaltung, wenn J = K = 1 ist! Welche Anwendung ergibt sich hieraus? Versuch 7.2 Asynchronzähler Bauen Sie zunächst einen 4-stufigen Binärasynchronzähler aus zwei Schaltkreisen vom Typ 74 LS 107 auf. Verwenden Sie als Ausgangsanzeige sowohl das LED-Modul als auch die 7-Segment-Anzeige und als Taktgenerator die entprellte Taste. Beobachten Sie, wie die Anzeige im Binärcode zählt. Was geschieht nach 15 Takten? - 19 - Verwenden Sie jetzt zur Taktung den Funktionsgenerator (TTL-Ausgang). Ozillographieren Sie gleichzeitig den Takteingang (Kanal I) und nacheinander alle Zählerausgänge 20 … 23 (Kanal II) und beobachten Sie das zeitverzögerte Schalten der einzelnen Flip-Flop-Stufen. Triggern Sie dazu den Ozillographen extern mit Ausgang 23. Warum? Verwenden Sie zur Sichtbarmachung beider Flanken die Funktion „Trigger-Delay“. Warum ist es für die Beobachtung der asynchronen Schaltflanken sinnvoll, die Zählerschaltung mit relativ hohen Taktfrequenzen anzusteuern? Wie groß ist bei dieser Schaltungsvariante die zeitliche Verzögerung zwischen dem Eingang und dem Ausgang 23, wie groß ist demnach also die Schaltverzögerung einer einzelnen Flip-Flop-Stufe? Bei welcher Grenzfrequenz wäre der Zählerstand zu keiner Zeit richtig und worin besteht somit der Nachteil des Asynchronzählers bzgl. längerer Zählerketten? Versuch 7.3 Synchronzähler a) Ändern Sie jetzt den Asynchronzähler durch die Verschaltung zweier zusätzlicher AND-Gatter (74 LS 08 s. Anhang) zu einem Synchronzähler entsprechend der nachfolgenden Schaltung um. Bei dieser Zählerschaltung werden im Gegensatz zum obigen Zählertyp alle vier JK-Flip-Flops gleichzeitig getaktet. Überprüfen Sie auch hier zunächst dessen Funktion, indem Sie als Taktgenerator erneut die prellfreie Taste verwenden. Benutzen Sie anschließend wiederum den Funktionsgenerator zur Takterzeugung und beobachten Sie mit dem Oszillographen das gleichzeitige Schalten der Ausgänge, indem Sie einen Kanal des Oszillographen als Referenz fest am Ausgang 20 angeschlossen lassen, den zweiten nacheinander an die Ausgänge 20 … 23 anschließen und die Schaltflanken miteinander vergleichen. Steuern Sie zur Sichtbarmachung der synchronen Schaltflanken die Schaltung mit relativ hohen Taktfrequenzen (f≈3MHz) an. (Triggerung entsprechend Teilaufgabe 7.2). - 20 - 20 21 22 b) Aus dem 4-stufigen Binärsynchronzähler (Modulo-16-Zähler) soll ein dekadischer Zähler (Modulo-10-Zähler) gebaut werden. Man erreicht dies, indem man den Zähler unmittelbar vor Erreichen des Zählerstandes „10“ automatisch auf „0“ zurücksetzt. Dies lässt sich relativ einfach mit einem NAND-Gatter erreichen. Ergänzen Sie die Schaltung entsprechend und prüfen Sie, wie die Schaltung nun als dekadischer Zähler arbeitet. c) Der Schaltkreis 74 LS191 enthält einen kompletten 4-Bit-Binärsynchronzähler, der nach dem Schaltprinzip des Zählers aus Teilaufgabe 7.3 a arbeitet. Überprüfen Sie dessen Funktion und beobachten Sie auch hier das gleichzeitige Schalten aller vier Zählerausgänge Q0 … Q3. (Triggerung und Taktfrequenz entsprechend Teilaufgabe 6.2). Welche ist die aktive Flanke des Zählereingangs? - 21 - 23 Versuch 7.4 Schieberegister a) Bauen Sie aus vier JK-Flip-Flops ein Schieberegister auf. Schreiben Sie eine „1“ in das erste Flip-Flop durch Anlegen eines High-Pegels am seriellen Eingang D und einmaliges Drücken der Takttaste CLK. Setzen Sie an schließend den Eingang auf Low und beobachten Sie, wie bei jedem erneuten Tastendruck die „1“ um eine Position verschoben wird, bis sie schließlich das Register verlässt. Welcher arithmetischen Operation im Binärcode entspricht eine solche Verschiebung, wenn man den Ausgängen Q eine Stellenwertigkeit zuordnet? b) Wiederholen Sie den Teilversuch a) mit dem Unterschied, dass Sie nach dem Einschreiben der „1“ in das Register den Eingang nicht auf Low legen, sondern mit dem Ausgang 23 verbinden. Beobachten Sie, wie beim Takten die Information jetzt zyklisch durch das Register geschoben wird (Ringzähler). - 22 - Versuch 8 Digital/Analog- und Analog/Digital-Wandler Vorbereitung: Informieren Sie sich über die Funktion von D/A- und A/D-Wandlern. Dimensionieren Sie die Schaltungen, soweit erforderlich. Welche Verfahren der A/D-Wandlung sind gebräuchlich? Informieren Sie sich über die Vorzüge und Nachteile der Verfahren. Welche Verfahren der besten Annäherung des Analogwertes sind Ihnen bekannt? Erläutern Sie, warum das Sukzessive-Approximations-Register (SAR) eine zeitoptimierte Variante ist. Versuch 8.1 Digital/Analog-Wandler a) Die prinzipielle Funktionsweise eines Digital/Analog-Wandlers soll mit folgender Schaltung eines 4-Bit-D/A-Wandlers überprüft werden: Die Widerstände R1 … R4 werden mittels gleichwertiger Widerstände von 100kΩ durch Reihen- bzw. Parallelschaltung realisiert. Der Widerstand R5 wird durch Reihenschaltung von einem Festwiderstand und einem veränderlichen Widerstand (Spindelpotentiometer) gebildet. Dimensionieren Sie die Schaltung so, dass für die Referenzspannung 5V (TTL-Spannungsversorgung) das niederwertigste Bit (LSB) sich um 0,1V ändert (alle Eingänge geschlossen entspricht UA = 1,5V). b) Erweitern Sie die Schaltung dadurch, dass die Digitaleingänge von den Ausgängen eines Zählers angesteuert werden. Durch den Schaltkreis HCT 191 ist gewährleistet, dass die Ausgangspegel stets definiert sind. - 23 - Verwenden Sie zwei getrennte Experimentierplatinen für Analog- bzw. Digitalteil. (Beide Schaltungsteile werden in den nachfolgenden Schaltungen noch erweitert). Takten Sie den Zähler mit dem TTL-Ausgang des Funktionsgenerators und beobachten Sie das Ausgangssignal des Wandlers (Oszillograph mit dem Analogausgang triggern). Sie können jetzt die Treppenfunktion des Wandlers beobachten. Vergleichen Sie den Nullpunkt und den Maximalwert mit dem Ergebnis aus Teilaufgabe a). Korrigieren Sie mögliche Abweichungen des Maximalwertes durch Abgleich mit R5. Versuch 8.2 Analog/Digital-Wandler a) Analog/Digital-Wandler nach dem Nachlaufverfahren Erweitern Sie Versuch 8.1 b) zu einem A/D-Wandler nach folgender Prinzipschaltung: Der Zählerstand wird so lange erhöht, bis die vom D/A-Wandler gelieferte Analogspannung die zu messende Eingangsspannung übersteigt. Das dabei gelieferte Komparatorsignal D sperrt das Tor, und der Zählerstand entspricht dem über dem Eingangssignal liegenden Wert. - 24 - - 25 - A/D-Wandler nach dem Nachlaufverfahren Bauen Sie den Wandler auf und überzeugen Sie sich von dessen Funktionsweise. Erzeugen Sie dabei die benötigte Analogspannung aus der Offsetspannung des Funktionsgenerators bei abgeschalteter Wechselspannung. Welche Polarität muss die Spannung am Analogeingang besitzen, damit der A/D-Wandler arbeitet? Welche Größe bestimmt die Wandlungszeit? Beurteilen Sie, ob die Wandlungszeit zeitoptimal ist. Wie kann prinzipiell die Genauigkeit erhöht werden? b) Sukzessives-Approximations-Register (SAR) Eine zeitoptimierte Strategie zum Setzen der entsprechenden Schalter des D/AWandlers für die beste Annäherung an den zu messenden Analogwert lässt sich mit Hilfe des Sukzessiven-Approximations-Registers (SAR) realisieren, wie es in der folgenden Prinzipschaltung wiedergegeben ist: Vom MSB beginnend wird nacheinander jedes Bit versuchsweise gesetzt, und in Abhängigkeit vom Komparatorstand wird es belassen oder zurückgesetzt. Das SAR realisiert man günstig aus einem Schieberegister mit gleicher Anzahl von Stufen wie der D/A-Wandler an Bit Auflösung hat und gleicher Anzahl von D-Flip-Flops, die die Ergebnisse speichern. Aus dem Prinzipschaltbild (siehe z.B. Tietze/Schenk, S. 782) resultiert folgende Wirkungsweise für jedes Bit: Zi D - 26 - Das gesetzte Flip-Flop des Schieberegisters setzt über ein ODER-Gatter den D/AWandler. Der Komparatorstand D wird wie oben beschrieben im oberen D-FlipFlop gespeichert und verbleibt als Ergebnis für das betrachtete Bit. Die Schaltung für das SAR zeigt das folgende Bild. Bauen Sie den Wandler auf und überzeugen Sie sich von dessen Funktion! (Die nicht benötigten Eingänge ( S1 und S2 ) des 74LC74 sind auf High zu legen!) Z3 Z2 Z1 Z0 Einige Details sollen durch nachstehende Hinweise erläutert werden: • Die verwendeten D-Flip-Flops im 74 LS 74 sind positiv flanken getriggert. Die Schieberegisterkette (untere Reihe im Schaltbild) lässt sich hieraus problemlos aufbauen, wobei die Ausgänge des 1. Flip-Flops vertauscht sind, um den Anfangswert gleich bei Nullsetzung zu erreichen. • Das Ergebnis des probeweisen Setzens liegt erst nach einer Entscheidungszeit des A/D-Wandlers und des Komparators als Signal D vor. Deshalb kann erst die „Abschaltflanke“ des Schieberegisters zur Taktung des oberen Auffangregisters genutzt werden. Diese „Abschaltflanke“ liegt als positive Flanke am invertierenden Ausgang des Schieberegisters vor. Die notwendige ODER-Funktion wird mit NAND-Gattern realisiert (DE MORGAN), woraus sich die Nutzung der invertierten Ausgänge sowohl am Schieberegister als auch am Auffangregister erklärt. • Hinweis: Der Schaltkreis 74 LS 74 enthält ein oberes und ein unteres D-Flip-Flop. Die gleiche Aufteilung wie im Schaltplan führt zu einem übersichtlichen Aufbau. Weiterhin ist es günstig, den 74 LS 00 mittig zwischen die vier 74 LS 74 zu stecken. - 27 - c) Analog/Digital-Wandler nach dem Dual-slope-Verfahren Die in der Literatur (z.B. Tietze/Schenk, S.787) angegebenen schematischen Schaltungen zum Dual-slope-Verfahren zeigen drei mechanische Schalter. Die kontaktlose Realisierung erfolgt in der hier angegebenen Schaltung mit dem CMOS- Schaltkreis 4066. Dabei ist zu berücksichtigen, dass dieser nur Spannungen zwischen 0V und der Betriebsspannung (hier +5V wegen der steuernden TTL-Schaltkreise) schalten kann. Im Versuchsaufbau wird deshalb die geschaltete positive Messspannung UMeß invertiert (IS7 s. Schaltung), woraus sich erklärt, dass die Dreieckspannung am Ausgang des Integrators (IS9 s. Schaltung) positiv ist. Demgegenüber erfolgt das Abintegrieren mit einer positiven Referenzspannung URef, die nach dem Schalten auf 10V verstärkt wird (IS8 s. Schaltung), damit sich eine einfache Beziehung zwischen Zählerstand und Messspannung ergibt. Kernstück des Digitalteils sind die beiden RS-Flip-Flops, welche entsprechend dem zeitlichen Ablauf der Messung die Steuerung der Schalter und des Zählers übernehmen. Mit Hilfe des entprellten Tasters wird die Messung durch Setzen der RS-Flip-Flops gestartet, wobei ein zusätzlicher Pulsformer die Blockierung der FlipFlops vermeidet. Die Phase des Aufintegrierens wird durch den Übertragsausgang (CO) des Zählers beendet, die Phase des Abintegrierens beendet der (im Analogteil befindliche) Nullkomparator, gleichzeitig wird das Weiterzählen durch das Tor 1 gestoppt. Bauen Sie die Schaltung in der vorgeschlagenen Dimensionierung auf, wobei zunächst eine Taktfrequenz f = 10 kHz zu wählen ist! Der regelbare Widerstand im Analogteil ist so einzustellen, dass die Referenzspannung +URef nach der Verstärkung 10 V beträgt. Nutzen Sie als Messspannung (Analogeingang) wieder die Offset-Einstellung des Funktionsgenerators bei ausgeschalteter Wechselspannung. Schalten Sie die Messspannung erst dann zu, wenn die Betriebsspannung für die gesamte Schaltung anliegt. Ermitteln Sie den Zählerstand und das Maximum der Dreieckspannung am Ausgang des Umkehrintegrators (oszillografisch) in Abhängigkeit von der Eingangsspannung! Wiederholen Sie diesen Punkt bei Änderung der Taktfrequenz um ± 20% und um ± 50%. Ändern Sie zusätzlich bei einer konstanten Taktfrequenz von f = 10 kHz die Kapazität im Rückkopplungskreis des Umkehrintegrators um +10% und ermitteln Sie nochmals den Zählerstand und das Maximum der Dreieckspannung! Hinweis: Digitalteil- und Analogteil lassen sich günstig auf zwei getrennten Steckplatinen realisieren. Eine weitgehende Verwendung von festen Steckbrücken ermöglicht einen übersichtlichen Aufbau und wird empfohlen. Die vorgegebene Pin-Belegung der Schaltkreise im Digitalteil erleichtert den Versuchsaufbau. Nutzen Sie für die beiden RSFlip-Flops einen 74 LS 00 (IS3 s. Schaltung). - 28 - - 29 IS1 IS2 IS3 Digitalteil des A/D-Wandler nach dem Dual-slope-Verfahren IS4 IS7 - 30 IS9 IS10 IS8 Analogteil des A/D-Wandler nach dem Dual-slope-Verfahren Versuch 9 Multiplikation und Division von Dualzahlen Vorbereitung: Informieren Sie sich, wie in digitalen Rechenschaltungen die Multiplikation und Division von Dualzahlen realisiert werden können. Welche Unterschiede bestehen zwischen den Verfahren der seriellen und der parallelen Multiplikation? Wie sind Volladdierer aufgebaut, wie lassen sie sich schaltungstechnisch realisieren und worin besteht der Unterschied zu einem Halbaddierer? Was versteht man unter der Zweierkomplementdarstellung einer Binärzahl? Durch welche logische Operation wird eine bitweise Multiplikation erreicht? Versuch 9.1 a) Serielle Multiplikation Verdeutlichen Sie sich zunächst an dem Beispiel 13 x 11 = 143 den generellen Ablauf der Multiplikation von Dualzahlen. Machen Sie sich anschließend klar, dass die übliche mehrfache Summation schaltungstechnisch durch die sukzessive Addition zweier 4-Bit Zahlen (mit Übertrag) unter Bildung von Zwischensummen ersetzt wird. Anfangswert: „0“ + Ergebnis aus der 1. Multiplikation mit „13“ Ü= Ü= Ü= Ü= 1.Zwischenergebnis: LSB ins Ergebnis; MSB wird aufgefüllt (Ü) + Ergebnis aus der 2.Multiplikation mit „13“ 2.Zwischenergebnis: LSB ins Ergebnis; MSB wird aufgefüllt (Ü) + Ergebnis aus der 3. Multiplikation mit „13“ 3.Zwischenergebnis: LSB ins Ergebnis; MSB wird aufgefüllt (Ü) + Ergebnis der letzten Multiplikation mit „13“ Ergebnis aus den LSBs der 1.-3. Zwischenergebnisse und der letzten Addition (Multiplikation mit „13“ und der 3. Zwischensumme). - 31 - - 32 IS1 IS2 IS3 Serielle 4-Bit Multiplikation b) Überprüfen Sie an verschiedenen selbstgewählten Additionsbeispielen die Funktion des Volladdierers 74 LS 283. Achten Sie auf die Bitwertigkeit (LSB und MSB) der Eingänge und des Ausgangs. Warum muss der Übertragseingang C0 auf Low gesetzt werden? c) Testen Sie anschließend die Funktion des Schieberegisters 74 LS 194. Zeigen Sie, dass die an den Dateneingängen D0 … D3 anliegenden Informationen bei Takt auf Q0 … Q3 übertragen werden (parallele Dateneingabe bzw. Daten – übernahme). Löschen Sie jeweils die Inhalte des Registers, indem Sie RD kurz auf Low setzen. Überzeugen Sie sich dann, dass die Funktion Rechtsschieben bzw. Linksschieben einer Division bzw. einer Multiplikation mit der Zahl 2 entspricht. Achten Sie auf die Pegel der Steuereingänge S1 und S2 sowie DSR und DSL (s. Anhang). d) Die bitweise Multiplikation wird hier durch vier AND-Gatter (74 LS 08) realisiert, wobei das nächsthöhere Bit des Multiplikators jeweils durch Rechtsschieben bereitgestellt wird. Von der Zwischensumme wird schrittweise das sich nicht mehr ändernde LSB (∑0) abgespalten und in das Ergebnis übertragen. Die schrittweise Erhöhung der Stellenwertigkeit bei der Addition erfolgt schaltungstechnisch unter Nutzung des Übertrags. Bauen Sie nun die gesamte Rechenschaltung entsprechend dem vorgegebenen Schaltplan auf und erproben Sie die serielle Multiplikation an drei selbstgewählten Beispielen. Zur Vorbereitung sind Multiplikand A und Multiplikator B durch Low- bzw. High-Setzen zu stecken. Anschließend sind eventuelle Inhalte der beiden Auffangregister zu löschen ( RD von IS2 und IS3 kurz auf Low setzen). Dann ist die Zahl B mittels Datenübernahme (Eingang S2 des IS3 auf High setzen und Taktpuls) in den Schaltkreis zu übernehmen. Bei der Ausführung der Multiplikation wird der Schaltkreis IS3 in die Funktion „Rechtsschieben“ gesetzt (Eingang S2 auf Low), und nach vier Takten kann das Ergebnis im 8-Bit-Dualform an den Einzelbitanzeigen abgelesen werden. Überprüfen Sie die angezeigten Zwischensummen nach jedem Takt. Hinweis: Es ist günstig, die Einzelbitanzeigen (LED-Module) direkt über den Ausgängen (Q0 …Q3) der Schaltkreise 74 LS 194 anzuordnen, wodurch ein übersichtlicher Versuchsaufbau ermöglicht wird. Für die jeweils nebeneinander liegenden 4 Bit sind 4-fach Datenleitungen vorteilhaft. - 33 - Versuch 9.2 a) Serielle Division Bei der üblichen Art „schriftlich“ zu dividieren, wird im dekadischen System so vorgegangen, dass beginnend mit den höherwertigen Stellen des Dividenden ein n-faches des Divisors abgezogen wird. Ist das Ergebnis negativ, so wird n verkleinert bzw. 0 gesetzt. Anschließend wird durch sukzessives Weiterrücken und Übernehmen der nächsten Stelle der Vorgang wiederholt. Verdeutlichen Sie sich anhand des folgenden Rechenbeispiels 63 / 7 = 9, dass im Binärsystem ähnlich verfahren wird. Zusätzlich vereinfacht sich dieses Verfahren, da nur der Divisor selbst (n=1) oder nichts abgezogen werden kann (n=0). Die Differenzbildung kann in jedem Schritt vorgenommen werden. Es müssen nur zwei Fälle unterschieden werden: • • Das Ergebnis ist positiv: 1) Im Quotienten wird eine „1“ eingetragen. 2) Die Differenz wird in der Wertigkeit erhöht (eine Stelle nach links gerückt) und als LSB wird das nächste Bit des Dividenden zur folgenden Differenzbildung angefügt. Das Ergebnis ist negativ: 1) Im Quotienten wird eine „0“ eingetragen. 2) Der ursprüngliche Minuend wird in der Wertigkeit erhöht (wiederum gerückt) und als LSB wird ebenfalls das nächste Bit des Dividenden zur folgenden Differenzbildung angefügt. b) Hinweis: Machen Sie sich dann klar, dass die im Beispiel ausgeführte Differenzbildung durch die Addition des Zweierkomplements des Divisors im 4-Bit-Format vorgenommen werden kann. Somit ergibt sich für das obige Divisionsbeispiel zweier Dualzahlen folgender Rechenablauf. Das Zweierkomplement der Dualzahl 7 (0111), ergibt sich aus: dem Einerkomplement (bitweise Negation) von 7 (‘1000‘) + 1 (‘0001‘) = ‘1 0 0 1‘. - 34 - Zweierkomplement Ergebnis im Zweierkomplement 0 LSB wird angefügt MSB = 0, d.h. Ergebnis im Quotienten =1! Zweierkomplement Ergebnis im Zweierkomplement MSB = 1, d.h. Ergebnis im Quotienten =0! 1 Zweierkomplement Ergebnis im Zweierkomplement 1 MSB = 1, d.h. Ergebnis im Quotienten =0! Zweierkomplement Ergebnis im Zweierkomplement MSB = 0, d.h. Ergebnis im Quotienten =1! 0 Da bei der Differenzbildung mit Hilfe des Zweierkomplements das Ergebnis ebenfalls im Zweierkomplement erscheint, kann das MSB der Zwischendifferenz jeweils zur Entscheidung genutzt werden. Gleichzeitig ist das Komplement des MSB die einzutragende Stelle des Quotienten. c) Ändern Sie die Schaltung der seriellen Multiplikation zur seriellen Division entsprechend der angefügten Schaltung um. Achten Sie dabei darauf, dass aufgrund des nahezu ähnlichen Schaltungsaufbaus die Grundschaltkreise (außer 74LS08) sowie einige Verbindungsleitungen (Versorgungsspannungen, Takt, etc.) erhalten bleiben können. Unter Beachtung dieser Tatsache ist ein schneller und übersichtlicher Schaltungsumbau gewährleistet. Erproben Sie dann die Schaltung der schrittweisen Division zuerst an dem oben erläuterten Beispiel. Überprüfen sie die Zwischenschritte an dem zusätzlichen 3. LED-Modul (Zwischenergebnis). Führen Sie anschließend zwei weitere selbstgewählte Rechenbeispiele durch, bei denen der zu erreichende Quotient vorerst eine ganze Zahl ≤ 15, d.h. ohne Rest, ist. Für den fehlerfreien Ablauf der seriellen Division ist es zunächst wieder notwendig, die Inhalte der Schieberegister 74LS194 (RD von IS 2 und IS 3 kurz auf Low setzen) zu löschen. Der Divisor ist zu setzen. Der Dividend muss darauf in die kaskadierten Schieberegister eingetragen werden, wobei zu erkennen ist, dass höchstens das Bit 26 = 64 besetzt sein darf. Im ersten Schritt werden dann die höchsten 4 Bit (Stellenwertigkeit 23 … 26 des Dividenden) über den Volladdierer mit dem Zweierkomplement des Divisors verarbeitet. Die Zweierkomplementbildung erfolgt durch bitweises Negieren des Divisors, Setzen des MSB und Addition von „1“ über Setzen des Eingangsübertrages Co. - 35 - Das rechte Schieberegister (IS3) ist ständig in der Funktion Schieben links gesetzt. Der linke Schaltkreis (IS2) wird in Abhängigkeit vom Ergebnis der Differenzbildung in seiner Funktion geändert, wobei das MSB des Volladdieres - wie oben erläutert – das Eintragen des Ergebnisses in das rechte Schieberegister über DSL steuert. Gleichzeitig wird in Abhängigkeit vom MSB des Volladdieres das linke Schieberegister in seiner Funktion verändert. Bei positiver Zwischendifferenz (MSB = 0) werden die restlichen 3Bit der Differenz in das linke Schieberegister beim Taktpuls eingetragen (Funktion Datenübernahme des 74LS194). Die Erhöhung der Wertigkeit ist hardwaremäßig realisiert. Bei negativer Zwischendifferenz wird das linke Schieberegister in die Funktion Schieben links gesetzt, und beim Taktpuls wird der ursprüngliche Inhalt des kaskadierten Schieberegisters nach links geschoben, d.h. in seiner Stellenwertigkeit erhöht. Gleichzeitig wird ebenfalls das Ergebnis in das rechte Register eingetragen. Das Ergebnis der seriellen Division steht nach vier Taktpulsen im rechten Schieberegister. d) Testen Sie anschließend die Schaltung hinsichtlich des Falls, dass der Dividend kein ganzzahliges Vielfaches des Divisors ist und somit bei der Quotientenbildung ein „Rest“ überbleibt. Wie ist dieser in der Schaltung zu erkennen? Rechnen Sie dazu auch eine Divisionsaufgabe schriftlich im Dualformat durch und vergleichen Sie diese mit dem Rechenablauf. e) Aus der schaltungstechnischen Realisierung (4-Bit-Volladdierer, 2x4 BitSchieberegister) ergibt sich eine Begrenzung des Wertevorrates der Division: Quotient: Divisor: höchstens höchstens 1 1 1 1 = 15 1 1 1 = 7. Wie könnte die vorliegende Schaltung für einen größeren Wertevorrat (Quotient ≤ 255, Divisor ≤ 127) konzipiert werden. Welche zusätzlichen Bauelemente werden dann benötigt? - 36 - - 37 IS1 IS2 IS3 Serielle 4-Bit Division Anhang - 38 - - 39 - interne Verdrahtung des Schaltbrettes Einzel-LED-Anzeige LED-Modul steckbar Die Module werden auf der Platine am besten so platziert, dass der +5V Stift in die oberste Querreihe und der Masse Stift in die zweitoberste Querreihe gesteckt werden. - 40 - Ausgangskennlinienfeld Si- npn-Bipolartransistor BCY 58 Blick von unten Ausgangskennlinienfeld Ausgangskennlinienfeld - 41 - - 42 - UB+ A UB- - 43 - - 44 - - 45 - Die Dateneingänge D0, D1, D2 und D3 werden – wenn nicht benötigt - auf Masse gelegt. Die Dateneingänge D0, D1, D2 und D3 werden – wenn nicht benötigt - auf Masse gelegt. - 46 - DSR DSL - 47 - - 48 -