Übung 1 - Lehrstuhl für Informatik 12

Werbung

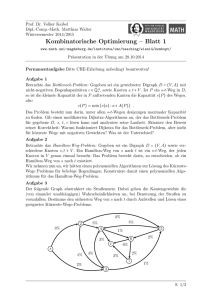

Lehrstuhl für Informatik 12 Cauerstraße 11 91058 Erlangen TECHNISCHE FAKULTÄT 1. Übung zur Vorlesung Parallele Systeme Aufgabe 1 (Performanz) Auf einem Prozessor mit einer Taktrate von 2,24 GHz soll ein aus 200000 Instruktionen bestehender Objekt-Code ausgeführt werden. Der Code besteht aus vier verschiedenen Instruktionstypen unterschiedlicher Häufigkeit und Ausführungszeit (CPI = Cycles per Instruction), wie in nachfolgender Tabelle angegeben. Instruktions-Typ arithmetisch/logisch laden/speichern mit Cache-Hit Verzweigung Speicherzugriff bei Cache-Miss CPI 1 2 4 8 Häufigkeit 60% 18% 12% 10% a) Welche Ausführungszeit benötigt das oben beschriebene Programm? b) Bestimmen Sie die MIPS-Rate des Prozessors. Aufgabe 2 (PRAM-Modell) Entwerfen Sie einen Algorithmus, um das Maximum von n ganzzahligen Werten in O(log n) Zeitschritten für ein EREW-PRAM Modell zu bestimmen. Nehmen Sie an, dass zur Initialisierung jeder zur Verfügung stehende Prozessor bereits einen Eingabewert geladen hat. 1 Aufgabe 3 (Klassifikation von Parallelrechnern) Unterscheiden Sie nachfolgende Architekturen gemäß in der Vorlesung vorgestellten Kriterien und klassifizieren Sie die Architekturen nach Flynns Schema. a) Der Tianhe-2 (“Milchstraße-2”) besteht aus 16000 Knoten, die jeweils zwei Intel XeonMehrkernprozessoren sowie drei Vielkernbeschleuniger des Typs Intel Xeon Phi beherbergen (siehe Abb. 1). 32 GB Proprietäres Highspeed-Netzwerk 16x PCIE Network Interface Chip 8 GB Gb-LAN Xeon (12 Kerne) 16x PCIE Xeon Phi Platform Controller Hub Intel QPI 8 GB Xeon Phi 8 GB Xeon Phi 16x PCIE 16x PCIE Xeon (12 Kerne) Steuerungschip 32 GB Überwachung, Steuerung Beschleuniger (jeweils 57 Kerne) Abbildung 1: Tianhe-2 Knoten Die 16000 Knoten sind in Form eines Fat Tree zusammengeschlossen (d.h. die Bandbreite der Verbindungen nimmt von unten nach oben zu; siehe Abb. 2). Top-Level Switches ··· 0 0 ··· ··· 124 3 0 ··· ··· ··· 125 Racks 3 ··· Abbildung 2: Tianhe-2 Netzwerk 2 500 Frames 16.000 Knoten b) Der Wavetracer Data Transport Computer besitzt 32768 1-Bit-Prozessorelemente, die mittels eines dreidimensionalen Kubus-Netzwerkes miteinander verbunden sind (Abb. 3). Jedes Prozessorelement beinhaltet 2 Kilobit lokalen Speicher. Die Operationensteuerung wird von einem AMD-RISC-Prozessor zentral durchgeführt. Knoten 2 Kilobit SRAM 1-Bit-Prozessor Über Kubusnetzwerk Externer RAM Abbildung 3: Wavetracer DTC c) Im Intel Paragon XP/S sind bis zu 1024 Knoten mittels eines 2D-Gitternetzwerks miteinander verbunden (Abb. 4). Jeder Knoten besteht aus 5 Mikroprozessoren des Typs Intel i860XP und lokalem Speicher, auf den nur innerhalb eines Knotens zugegriffen werden kann. I/O System Application I/O Application Processor 1 i860XP Cache Level 2 .. . .. . Application Processor 4 i860XP Cache Level 2 Message Processor i860XP Cache Level 2 Data Transfer Engine Network Interface Performance Monitor Abbildung 4: Intel Paragon XP/S 3 Memory 400 MB/s 50 MHz single cycle d) Die CRAY X/MP-4 besteht aus der Kopplung von vier Cray-1 Vektorprozessoren, die mittels explizit ausgewiesener Speicherbereiche miteinander kommunizieren (Abb. 5). Interprocessor Communication Real-time Clock Vector Unit Scalar Unit CPU 1 (CRAY-1) Address Unit Control Unit I/O Main Memory (32 Banks) CPU 2 (CRAY-1) CPU 4 (CRAY-1) Interface Peripherals Abbildung 5: CRAY X/MP-4 4