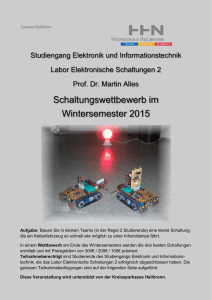

mikroprozessor schaltkreise

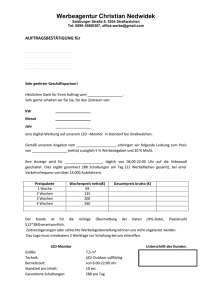

Werbung