Protokoll zu Grundelemente der Digitaltechnik

Werbung

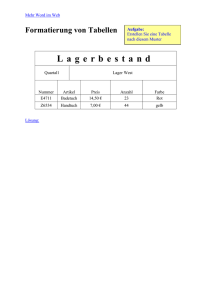

Protokoll zu Grundelemente der Digitaltechnik Ronny Harbich 22. Juli 2005 Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 2 Vorwort Das hier vorliegende Protokoll wurde natürlich mit größter Sorgfalt angefertigt. Trotzdem sind mit an Sicherheit grenzender Wahrscheinlichkeit Fehler in dieser Aufzeichnung enthalten. Falls der Leser ein Fehler erkennt, möge er mir bitte diesen unter [email protected] mitteilen. Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 3 Inhaltsverzeichnis 1. VORBEREITUNGSAUFGABEN 4 1.1. Logische Basisgatter 4 1.2. D-Flip-Flop und JK-Master-Slave-Flip-Flop 1.2.1. Das D-Flip-Flop Das JK-Master-Slave-Flip-Flop 1.2.2. 5 5 5 1.3. Von der Wahrheitstabelle zur kombinatorischen Schaltung 5 1.4. 4-Bit parallel-in/-out Register 6 1.5. 4-Bit seriell-in/parallel-out Register 6 1.6. Synchroner und asynchroner 4-Bit-Binärzähler 1.6.1. Synchroner Zähler Asynchroner Zähler 1.6.2. 1.6.3. Impuls-Diagramm zum 4-Bit-Binärzähler 7 7 7 8 1.7. Kenngrößen digitaler Gatter 8 2. VERSUCHSAUFGABEN 9 2.1. Basisgatter 9 2.2. Code-Wandler 9 2.3. Kombinatorische Schaltung 10 2.4. Flip-Flops 2.4.1. D-Flip-Flop 2.4.2. JK-Flip-Flop 11 11 12 2.5. Register 2.5.1. 4-Bit parallel-in/-out Register 2.5.2. 4-Bit seriell-in/parallel-out Register 12 12 13 2.6. Zähler 2.6.1. Asynchroner 4-Bit-Binärzähler 2.6.2. Synchroner 4-Bit-Binärzähler 13 13 16 2.7. 16 Dynamisches Verhalten Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 4 1. Vorbereitungsaufgaben 1.1. Logische Basisgatter Gatter NOT (nicht) algebraisches Symbol ¬ oder Schaltnetz-Symbol x ¬x x ¬x x AND (und) oder 1 x y x y & x y x y NAND (nicht und) oder + & 1 x y oder >= 1 >= 1 x y x y x y x y ¬x 0 1 1 0 x y 0 0 1 1 0 1 0 1 x y 0 0 0 1 x y x y 0 0 1 1 0 1 0 1 1 1 1 0 y x y y 0 0 1 1 x y x y x y x x y NOR (nicht oder) EXOR (exklusives oder) x y ¬x x x x =1 x Beschreibung Das NOT-Gatter (auch Negator) dient zum Invertieren der beiden logischen Wahrheitswerte Null und Eins. Dies bedeutet, dass am Ausgang des Gatters genau dann die logische Eins anliegt, wenn der Eingang mit der logischen Null belegt ist und dann und nur dann eine Null am Ausgang anliegt, wenn der Eingang mit Eins belegt ist. x y x y OR (oder) Wahrheitstabelle x Am Ausgang des AND-Gatters liegt dann und nur dann eine logische Eins an, wenn die beiden Eingänge jeweils den Wert logisch Eins haben. Am Ausgang des NAND-Gatters liegt im Gegensatz zum ANDGatter immer nur dann eine logische Eins an, wenn an beiden Eingängen nicht jeweils der Wert Eins anliegt. Mit Hilfe des NANDGatters lassen sich alle anderen Gatter realisieren, was dieses Gatter aufgrund einfacher technischer Bauweise geradezu für den technischen Einsatz prädestiniert. y 0 1 0 1 0 1 1 1 Bei dem OR-Gatter hat der Ausgang den Wert logisch Eins genau dann, wenn an beiden Eingängen nicht jeweils eine logische Null anliegt. x y x y 0 0 1 1 0 1 0 1 1 0 0 0 Am Ausgang des NOR-Gatters liegt im Gegensatz zum ORGatter immer nur dann eine logische Eins an, wenn an beiden Eingängen jeweils der Wert Null anliegt. y x y y 0 0 1 1 0 1 0 1 x y 0 1 1 0 Bei dem EXOR-Gatter wird der Ausgang nur dann den Wert Eins annehmen, wenn beide Eingänge zueinander unterschiedliche Wahrheitswerte haben. EXOR 1 wird daher auch als Antivalenz bezeichnet. Antivalenz (Wertungleichheit) ist das Gegenteil von Äquivalenz (Wertgleichheit) Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 5 1.2. D-Flip-Flop und JK-Master-Slave-Flip-Flop 1.2.1. Das D-Flip-Flop Reset Q Data Q Set Clock RS-Flip-Flop Abbildung 1: D-Flip-Flop Das D(elay)-Flip-Flop (Abbildung 1) ist ein besonderes Flip-Flop, welches aus den beiden Eingänge Data und Clock besteht. An dem Data-Eingang liegt zu jeder Zeit entweder das Datum Null oder Eins an. Sobald am Clock-Eingang eine logische Eins an liegt, wird das zu diesem Zeitpunkt am DataEingang befindliche Datum an den Ausgang Q weiter geleitet, anderen Falls behält dieser Ausgang seinen ursprünglichen Zustand bei. Die nun folgende Zustandstabelle fasst die genannten Sachverhalte zusammen: Clock Data Q n +1 Q n +1 0 0 Qn Qn 0 1 Qn Qn 1 1 0 1 0 1 1 0 1.2.2. Das JK-Master-Slave-Flip-Flop J K R Q R Q QJK S Q S Q QJK Clock Abbildung 2: JK-Master-Slave-Flip-Flop Wie sich in Abbildung 2 erkennen lässt besteht das JK-Master-Slave-Flip-Flop aus zwei hintereinander geschalteten JK-Flip-Flops. 1.3. Von der Wahrheitstabelle zur kombinatorischen Schaltung x1 x2 xn f1,n ( x1 , x 2 , , xn ) x1,1 x1,2 x1,n y1,1 y1,m x 2n ,1 x 2n ,2 x 2n ,n y 2n ,1 y 2n ,m Abbildung 3: Wahrheitstabelle W f m,n ( x1 , x 2 , , xn ) Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik Es sei die durch die n-stelligen boole’schen Funktionen fi,n : 6 {0;1} {0;1} n mit i = 1, ,m; ; m < 2 induzierte Wahrheitstabelle W (Abbildung 3) gegeben. Um nun eine kombinatorische Schaltung zu Erzeugen, ist es zunächst notwendig die so genannten disjunktiven Normalformen (DNF) der einzelnen boole’schen Funktionen f i,n aus dieser Wahrheitstabelle zu erzeugen. Dies 2n n, m geschieht mit Hilfe des folgenden Algorithmus, der die Normalform zur Funktion fi,n liefert: function getDNF ( W,i ) for ( j = 1; j 2n ; j + + ) if ( y j,i == 1) for ( k = 1; k n; k + + ) konj := konj ( x j,k == 1) ? "x k " : " ¬x k " end for DNF := DNF konj konj := "" end if end for return DNF end function ( ) Als nächstes können die einzelnen Normalformen noch mittels Karnaugh-Veitch-Diagramm oder algebraischer Gesetze vereinfacht werden. Schlussendlich muss nur noch entsprechend der vereinfachten disjunktiven Normalformen die kombinatorische Schaltung mittels der Basis-Gatter aufgebaut werden. 1.4. 4-Bit parallel-in/-out Register Die folgende Abbildung 4 zeigt ein 4-Bit parallel-in/-out Register, welches aus D-Flip-Flops aufgebaut ist: Q1 Q2 Q3 Q4 D Q D Q D Q D Q >C Q >C Q >C Q >C Q Clock D1 D2 D3 D4 Abbildung 4: 4-Bit parallel-in/-out Register 1.5. 4-Bit seriell-in/parallel-out Register Abbildung 5 veranschaulicht ein 4-Bit seriell-in/parallel-out Register, das mit D-Flip-Flops realisiert wurde: Q1 Data Q2 Q3 Q4 D Q D Q D Q D Q >C Q >C Q >C Q >C Q Clock Abbildung 5: 4-Bit seriell-in/parallel-out Register Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 7 1.6. Synchroner und asynchroner 4-Bit-Binärzähler 1.6.1. Synchroner Zähler Die nachstehende Abbildung 6 zeigt einen mittels JK-Flip-Flops realisierten synchronen 4-Bit-Binärzähler: Q1 Q2 Q4 Q J >C 1 Q3 J K Q Q >C J K Q >C >C K Q K Q Q J Q Clock Abbildung 6: Synchroner 4-Bit-Zähler 1.6.2. Asynchroner Zähler Die Abbildung 7 stellt einen asynchronen 4-Bit-Binärzähler dar: Q1 J Clock 1 Q Q2 J Q Q3 J Q Q4 J Q >C >C >C >C K Q K Q K Q K Q Abbildung 7: Asynchroner 4-Bit-Binärzähler Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 8 1.6.3. Impuls-Diagramm zum 4-Bit-Binärzähler Abbildung 8 veranschaulicht das Impuls-Diagramm (9 Impulse) zum 4-Bit-Binärzähler (positiv flankengesteuert): Clock Q1 Q2 Q3 Q4 Abbildung 8: Impuls-Diagramm zum 4-Bit-Binärzähler 1.7. Kenngrößen digitaler Gatter Gatter-Kenngrößen: • Pegelspannungen • Schaltzeit • Störabstand • Signalverzögerungszeiten • Störsicherheit • Signalübergangszeiten (Impulsflankendauer) Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 9 2. Versuchsaufgaben 2.1. Basisgatter • 74HC00 (NAND-Gatter) A = x y = ¬ ( x • 74HC10 (NAND-Gatter) A = y) : x y A 0 0 1 1 0 1 0 1 1 1 1 0 (( x y ) ( x y)) • 74H02 (NOR-Gatter) A = x y = ¬ ( x • 74H86 (EXOR-Gatter) A = x ( z = ¬ ¬(¬( x x y z A 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 0 ) y )) z : y) : x y A 0 0 1 1 0 1 0 1 1 0 0 0 x y A 0 0 1 1 0 1 0 1 0 1 1 0 y: 2.2. Code-Wandler Die folgende Wahrheitstabelle repräsentiert einen 1-aus-4-Decoder: Eingang Ausgang S5 S6 Y1 Y2 Y3 Y4 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 Eine Realisierung des Code-Wandlers mittels NAND-Gatters soll an dieser Stelle erfolgen. Zunächst einmal werden die disjunktiven Normalformen der einzelnen Ausgänge gebildet und anschließend zu Gleichungen mit nur NAND-Gattern umgeformt: Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik Y1 = ¬S5 Y2 = ¬S5 Y3 = S5 Y4 = S5 10 ( ¬S6 = ¬ ( ¬ ( ¬S5 ¬S6 ) ) = ¬ ¬S5 ¬S6 ( ) ¬S ) ) = ¬ ( S ¬S ) S ) ) = ¬ (S S ) S6 = ¬ ( ¬ ( ¬S5 S6 ) ) = ¬ ¬S5 S6 ¬S6 = ¬ ( ¬ ( S5 S6 = ¬ ( ¬ ( S5 6 5 6 5 ) 6 6 Als nächstes wird das Schaltnetz mit NAND-Gattern erstellt: Y1 Y2 Y3 S5 S6 Y4 Abbildung 9: 1-aus-4-Decoder mit NAND-Gattern Im weiteren Verlauf soll nun der gleiche Code-Wandler mit NOR-Gattern realisiert werden: Y1 = ¬S5 ¬S6 = ¬ ( S5 S6 ) = S5 S6 Y2 = ¬S5 S6 = ¬ ( ¬ ( ¬S5 S6 ) ) = ¬ ( S5 ¬S6 ) = S5 ¬S6 Y3 = S5 ¬S6 = ¬ ( ¬ ( S5 S6 ) ) = ¬ ( ¬S5 S6 ) = ¬S5 S6 Y4 = S5 S6 = ¬ ( ¬ ( S5 S6 ) ) = ¬ ( ¬S5 ¬S6 ) = ¬S5 ¬S6 Y4 Y3 Y2 S5 S6 Y1 Abbildung 10: 1-aus-4-Decoder mit NOR-Gattern 2.3. Kombinatorische Schaltung Die nachstehende Tabelle stellt die Schaltbelegungen einer zu entwerfenden kombinatorischen Schaltung dar: Eingang Ausgang S1 S2 S3 S4 Y2 Y1 Y0 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 0 0 0 0 0 0 1 1 0 1 0 1 Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 1 1 1 1 1 11 0 0 Anhand der Schaltbelegungstabelle lassen sich leicht die disjunktiven Normalformen der einzelnen Ausgänge bilden und mit Vereinfachung und mit Umwandlung in NAND-NOR-Gleichungen entstehen kommende Gleichungen für die Ausgänge Y0 , Y1 und Y2 : Y0 = ( ¬S1 S2 ) ( ¬S3 S4 ) = ¬ ¬ ( ( ¬S1 S2 ) ( ¬S3 S4 ) ) ( = ¬ ( ¬S1 S2 ) ¬ ( ¬S3 S4 ) = ¬S1 S2 ¬S3 S4 ( ) ( ) ) ( Y1 = ( ¬S1 S3 ) = ¬ ( ¬ ( ¬S1 S3 ) ) = S1 ¬S3 Y2 = S1 ) Im nächsten Schritt werden die Gleichungen mittels Basis-Gatter zu einer kombinatorischen Schaltung realisiert: S1 S2 Y0 S3 S4 BCD 7-Seg. Y1 0 Y2 Abbildung 11: kombinatorische Schaltung Schlussendlich soll noch eine Betrachtung der Ausgangswerte bei nicht definierten Eingangswerten unternommen werden: Eingang Ausgang S1 S2 S3 S4 Y2 Y1 Y0 7-Seg. 0 0 0 0 1 1 1 1 1 1 1 0 1 1 1 0 0 0 0 1 1 1 1 0 0 1 0 0 1 1 0 0 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 1 0 1 0 0 0 1 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 2 1 1 3 4 5 4 4 4 5 4 2.4. Flip-Flops 2.4.1. D-Flip-Flop Zustandstabellen eines D-Flip-Flops im 74HC74 Schaltkreis: Clock Data Qn Q n +1 0 0 0 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0 Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 1 1 1 0 1 1 1 0 1 12 0 1 1 Clock Data Q n +1 0 0 Qn 0 1 Qn 1 1 0 1 0 1 Das D-Flip-Flop ist positiv flankengesteuert. 2.4.2. JK-Flip-Flop Zustandstabellen eines JK-Flip-Flops im 74HC76Schaltkreis: J K Qn Q n +1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0 speichern rücksetzten setzen wechseln J K Q n +1 0 0 Qn speichern 0 1 1 0 0 1 rücksetzten setzen 1 1 Qn wechseln Das JK-Flip-Flop ist negativ flankengesteuert. 2.5. Register 2.5.1. 4-Bit parallel-in/-out Register Das 4-Bit parallel-in/-out Register wurde nach dem in Abschnitt 1.4 angefertigten Schaltnetz aufgebaut und folgend die Bits 0, 0, 1 und 1 an den Eingängen D1 , D 2 , D3 und D 4 angelegt. Wie zu erwarten lagen dann an den Ausgängen Q1 bis Q4 die gleichen Bits an. Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 13 2.5.2. 4-Bit seriell-in/parallel-out Register Analog wurde auch hier das Register nach dem Schaltnetz in Abschnitt 1.5 aufgebaut. Das Verhalten der Ausgänge Q1 bis Q 4 bei der Eingabe des Wortes 0011 zeigt das nachstehende ImpulsDiagramm: T1 T2 T3 T4 T5 T6 T7 Clock Data Q1 Q2 Q3 Q4 Abbildung 12: Impuls-Diagramm des 4-Bit seriell-in/parallel-out Registers Ab dem 7. Takt wird das Wort 0011 aus dem Register heraus geschoben. 2.6. Zähler 2.6.1. Asynchroner 4-Bit-Binärzähler Ein im Versuch realisierter asynchroner Zähler mit Impuls-Diagramm: 1 J Clock Q J Q J Q J Q >C >C >C >C K Q K Q K Q K Q Q1 BCD Q2 7-Seg. Q3 Q4 Abbildung 13: Asynchroner 4-Bit-Binärzähler T8 Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 0 1 2 3 4 5 6 14 7 8 Clock Q1 Q2 Q3 Q4 Abbildung 14: Impuls-Diagramm des asynchronen Binärzählers Im Folgenden wurden die einzelnen Ausgänge Q1 bis Q4 über dem Taktsignal (Clock) oszil- lographiert (negativ flankengesteuert): • Der Ausgang Q1 invertiert mit jedem Takt seinen logischen Zustand: Abbildung 15: Taktsignal (gelb) und Ausgang Q1 (blau) Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik • Der Ausgang Q2 invertiert mit jedem zweiten Takt seinen logischen Zustand: Abbildung 16: Taktsignal (gelb) und Ausgang Q 2 (blau) • Der Ausgang Q3 invertiert mit jedem viertem Takt seinen logischen Zustand: Abbildung 17: Taktsignal (gelb) und Ausgang Q 3 (blau) 15 Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 16 • Der Ausgang Q4 invertiert mit jedem achtem Takt seinen logischen Zustand: Abbildung 18: Taktsignal (gelb) und Ausgang Q 4 (blau) Allgemein invertiert der Q n -te Ausgang seinen logischen Wert mit jedem 2n 1 -ten Takt. 2.6.2. Synchroner 4-Bit-Binärzähler Ein synchroner Zähler, der aber im Versuch nicht aufgebaut und weiter untersucht wurde: BCD 7-Seg. Q1 J 1 Q2 Q3 Q4 Q >C K Q J Q >C J K Q >C >C K Q K Q Q J Q Clock Abbildung 19: Synchroner 4-Bit-Binärzähler 2.7. Dynamisches Verhalten Im weiteren Verlauf wurde ein reales NAND-Gatter mittels Digital-Oszilloskop untersucht. Hierzu wurde ein Taktsignal, das in den folgenden Abbildungen gelb dargestellt ist, an den beiden Eingängen angelegt. Der blau gekennzeichnete Verlauf in den Oszillogrammen veranschaulicht den Ausgang des NAND-Gatters. Das Oszilloskop zeigt interessante Eigenschaften des Gatters: Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 17 • Die nachstehende Abbildung 20 veranschaulicht den Verlauf der Eingangsspannung (gelb) und den der Ausgangsspannung (blau). Leicht lässt sich erkennen, dass das Eingangssignal, wie gewünscht, invertiert wird und, dass die Signale zu den Flanken hin nicht wirklich rechteckförmig sind: Abbildung 20: Eingang (gelb) und Ausgang (blau) eines NAND-Gatters Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 18 • Abbildung 21 verdeutlicht besonders gut die Verzögerung mit der das Gatter den Ausgangswert setzt. So beginnt das Gatter den Ausgangswert erst ab einer bestimmten Spannung, der so genannten Pegelspannung (hier high), auf low zu setzen. Dieses Verfahren ist unbedingt notwendig, um sicher zu gehen, dass das Gatter nicht Aufgrund von Störeinflüssen sein Ausgangswert ändert. Die sich daraufhin ergebene Gatterlaufzeit beträgt bei dem betrachtetem NAND-Gatter etwa 60ns: Abbildung 21: Detaillierte Betrachtung der Signale bei steigender Flanke des Taktsignals Ronny Harbich Protokoll zu Grundelemente der Digitaltechnik 19 • Ein analoges Verhalten des Gatters zeigt sich bei der Betrachtung des Eingangssignals an der fallenden Flanke: Abbildung 22: Detaillierte Betrachtung der Signale bei fallender Flanke des Taktsignals