erhält man dargestellt

Werbung

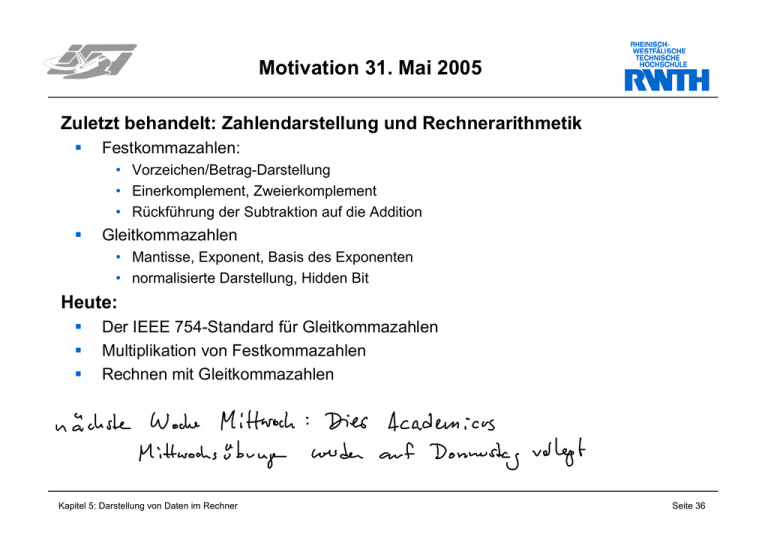

Motivation 31. Mai 2005 Zuletzt behandelt: Zahlendarstellung und Rechnerarithmetik Festkommazahlen: • Vorzeichen/Betrag-Darstellung • Einerkomplement, Zweierkomplement • Rückführung der Subtraktion auf die Addition Gleitkommazahlen • Mantisse, Exponent, Basis des Exponenten • normalisierte Darstellung, Hidden Bit Heute: Der IEEE 754-Standard für Gleitkommazahlen Multiplikation von Festkommazahlen Rechnen mit Gleitkommazahlen Kapitel 5: Darstellung von Daten im Rechner Seite 36 Wiederholung: Gleitkommadarstellung Bei der Gleitkommadarstellung (halblogarithmische Darstellung) wird jede Zahl in der Form z = ± m × b±d dargestellt. m heißt Mantisse, d Exponent und b ist die Basis für den Exponenten Als Basis des Exponenten wird üblicherweise 2 gewählt. Das Vorzeichen wird explizit durch ein Bit codiert. Eine Gleitkommazahl ist dann eine n-stellige Bitfolge, die Vorzeichen, Mantisse und Exponent enthält. Beispiel: 32 Bit Gleitkommazahl (1 Bit Vorzeichen, 8 Bit Exponent, 23 Bit Mantisse) Kapitel 5: Darstellung von Daten im Rechner Seite 37 Vorteile der Gleitkommadarstellung Verteilung von Festkommazahlen auf dem Zahlenstrahl: Verteilung von Gleitkommazahlen auf dem Zahlenstrahl: Bei der Festkommadarstellung ist der Abstand zur nächsten darstellbaren Zahl überall gleich. Bei der Gleitkommadarstellung wird die prozentuale Abweichung gering gehalten (große Zahlen werden etwas gröber approximiert als kleine Zahlen). Kapitel 5: Darstellung von Daten im Rechner Seite 38 Vergleich Festkomma-/Gleitkommadarstellung Größte darstellbare Zahl Genauigkeit Festkommadarstellung (32 Bit) 232-1 32 Bits - ca. 10 Dezimalstellen Gleitkommadarstellung (32 Bit, wie oben vorgestellt) ≈2127 23 Bits - ca. 7 Dezimalstellen Unter der Verwendung von Gleitkommazahlen ist ein erheblich größerer Zahlenbereich darstellbar als mit der Festkommadarstellung. Allerdings leidet darunter die Genauigkeit, die bei der Festkommadarstellung höher ist. Die Diskrepanz zwischen Genauigkeit und darstellbarem Zahlenbereich der Gleitkommadarstellung wird durch Verwendung einer anderen Basis als 2 vergrößert. Kapitel 5: Darstellung von Daten im Rechner Seite 39 Excess-Darstellung Die Exponenten werden häufig nicht im Zweier-Komplement, sondern in der Excess-Darstellung (auch Biased-Notation genannt) dargestellt. Beispiel: Beispiel:Excess-Darstellung Excess-Darstellung Betrachten Betrachtenwir wirdurch durch88Bits Bitsdargestellte dargestellteExponenten Exponentend, d,für fürwelche welchebei bei Verwendung Verwendungdes desZweier-Komplementes Zweier-Komplementes-128 -128≤≤dd≤≤127 127gilt. gilt. 8-1 Durch zujedem jedemdderhält erhältman maneinen einenExponenten Exponentend‘ d‘im im DurchAddition Additionvon von128=2 128=28-1zu Bereich Bereich00≤≤d‘ d‘≤≤255. 255. Durch Durchdiese dieseVerschiebung Verschiebungwird wirdder derVergleich Vergleichzweier zweierExponenten Exponentenvereinfacht vereinfacht (z.B. (z.B.für fürdie dieAnpassung Anpassungzweier zweierOperanden Operandenbei beider derAddition), Addition),gilt giltdd11≤≤dd22,,dann dann gilt giltdas dasauch auchfür fürdie diegewöhnlichen gewöhnlichenDualdarstellungen Dualdarstellungenvon vondd11und unddd22.. Allgemein erhält man die Excess-Darstellung d‘ eines Exponenten d bei g Bits durch: d‘=d+2g-1. Für g=8 spricht man von der Excess-127-Darstellung. Kapitel 5: Darstellung von Daten im Rechner Seite 40 IEEE 754 Das IEEE 754 Standard Floating Point Number Format ist eine häufig verwendete Gleitkommadarstellung für Binärzahlen. Ziel der Einführung war, dass identische Rechenwege auf unterschiedlichen Platformen auch zu identischen Ergebnissen kommen sollten Standard wurde nach öffentlicher Diskussion 1985 vom Institute of Electrical and Electronics Engineers (IEEE) als Standard definiert 1987 wurde mit IEEE 854 der Standard auf Dezimalzahlen erweitert. Interessante Verweise: http://www.h-schmidt.net/FloatApplet/IEEE754de.html http://grouper.ieee.org/groups/754/ IEEE 754 kennt zwei grundlegende Gleitkommazahlenformate: einfache Genauigkeit (32 Bit) doppelte Genauigkeit (64 Bit) Kapitel 5: Darstellung von Daten im Rechner Seite 41 IEEE 754: einfache Genaugkeit Einfache Genauigkeit (32 Bit) ist definiert wie folgt: Das erste Bit ist ein Vorzeichenbit: • 0 steht für eine positive Zahl, • 1 für eine negative Zahl. Die folgenden acht Bit nehmen den Exponenten auf • Er ist in der Excess-127-Darstellung gespeichert. • Von dem Exponenten muss der Wert 127 subtrahiert werden, um den tatsächlichen Exponenten zu ermitteln. • Die Basis des Exponenten ist 2. Die letzten 23 Bits nehmen die Mantisse auf: • sie ist normalisiert als 1,… (die erste 1 steht also vor dem Komma!) und • hat als hidden Bit die 1 vor dem Komma. 0 VZ 1 … Exponent E Kapitel 5: Darstellung von Daten im Rechner 8 9 … 31 Mantisse M Seite 42 IEEE 754: doppelte Genaugkeit Doppelte Genauigkeit (64 Bit) ist definiert wie folgt: Das erste Bit ist ein Vorzeichenbit: • 0 steht für eine positive Zahl, • 1 für eine negative Zahl. Die folgenden 11 Bit (statt 8) nehmen den Exponenten auf • Er ist in der Excess-1023-Darstellung gespeichert. • Die Basis des Exponenten ist 2. Die letzten 52 Bits (statt 23) nehmen die Mantisse auf: • sie ist normalisiert als 1,… (die erste 1 steht also vor dem Komma!) und • hat als hidden Bit die 1 vor dem Komma. 0 VZ 1 … Exponent E Kapitel 5: Darstellung von Daten im Rechner 11 12 … 63 Mantisse M Seite 43 IEEE 754 Eine 32-Bit Gleitkommazahl im IEEE 754-Format repräsentiert die Zahl N mit: N = (-1)VZ 1,M × 2E-127. Beispiel: Beispiel: Die DieZahl ZahlN=-0,15 N=-0,15wird wirddargestellt dargestelltals als 1 01111110 10000000000000000000000 - 126-127=-1 1,5 Für das Rechnen mit Zahlen im IEEE 754-Format gelten die gleichen Regeln, wie für die bisher bekannte Gleitkommadarstellung. Kapitel 5: Darstellung von Daten im Rechner Seite 44 Weitere Beispiele Gegeben: 1 1000 0001 1100 0000 0000 0000 0000 000 Gesucht: dezimale Darstellung! Gegeben: Dezimalzahl -0,625 Gesucht: Darstellung als 32-Bit IEEE 754 Gleitkommazahl Kapitel 5: Darstellung von Daten im Rechner Seite 45 Sonderfälle Die Null ist nicht im regulären IEEE 754-Format darstellbar: Ausnahmeregelung: Wenn E = 0 und M = 0 wird die Zahl Null dargestellt Denormalisierte Zahlen: Zwischen der kleinsten darstellbaren positiven Zahl und der größten darstellbaren negativen Zahl liegen im regulären IEEE 754-Format keine weiteren Zahlen Gerade um die Null herum sollte man möglichst genau rechnen können Falls E = 0 und M ≠ 0 ist die Zahl denormalisiert, d.h. mit ihr wird wie mit einer Festkommazahl gerechnet Die Zahl hat dann den Wert (-1)VZ ● 0,M ● 2-126 Die denormalisierten Zahlen partitionieren den Zahlenbereich um Null herum äquidistant (die Null wird auch zu einer denormalisierten Zahl) Kapitel 5: Darstellung von Daten im Rechner Seite 46 IEEE 754 - reservierte Zahlen Im IEEE 754-Format werden einige Fehler- und Sonderfälle durch bestimmte Zahlen dargestellt. Es gibt solche reservierte Zahlformate für die folgenden Fälle: E=0 E=255 M=0 Null NaN M/=0 Denormalisiert Unendlich Not a Number (NaN) wird verwendet, wenn das Ergebnis einer Operation keine gültige Zahl erzeugt (z.B. Division durch Null). Unendlichkeit: Wird verwendet als ± ∞, je nach Vorzeichen. Denormalisiert: Die Zahl ist nicht Null, aber zu klein, um sie normalisiert zu speichern, dann wird sie denormalisiert, also als 0.M dargestellt. Null: stellt die Zahl 0 dar. Kapitel 5: Darstellung von Daten im Rechner Seite 47 5.3 Multiplikation In Kapitel 3 und 5 wurden Addiernetze und -werke vorgestellt. Diese können im Allgemeinen auch zur Multiplikation und zur Division verwendet werden. Grundsätzlich wird die Multiplikation im Dualsystem in der gleichen Weise durchgeführt wie im Dezimalsystem nach der Schulrechenmethode: Der Multiplikand wird nacheinander mit jedem einzelnen Bit des Multiplikators multipliziert, dabei entsteht jeweils ein Teilprodukt. Beginnt man mit dem am weitesten rechts stehenden Bit, so wird ab der zweiten Stelle das Teilprodukt um jeweils eine Stelle nach links verschoben. Das Ergebnis erhält man durch Summation aller Teilprodukte. Kapitel 5: Darstellung von Daten im Rechner Seite 48 Multiplikation Beispiel Beispiel5.20: 5.20:Multiplikation Multiplikationim imDualsystem Dualsystem Wir Wirbetrachten betrachtendie dieAufgabe Aufgabe12 12⋅ ⋅9: 9: 1 2 Multiplikand 9 Multiplikator 1 8 9 1 1 0 0 Multiplikand 1 0 0 1 Multiplikator 1 1 0 0 0 0 0 0 Teilprodukte 1 0 8 Ergebnis 0 0 0 0 Teilprodukte 1 1 0 0 1 1 0 1 1 0 0 Ergebnis Kapitel 5: Darstellung von Daten im Rechner Seite 49 Multiplikation Die Multiplikation erfordert einen höheren physikalischen Aufwand als die Addition: Es ist ein doppelt so langes Ergebnisregister erforderlich. Die Hardware muss in der Lage sein, Shift-Operationen durchzuführen. Zudem ist die Schulmethode nicht effizient: Nullen im Multiplikator erfordern den gleichen Aufwand beim Multiplizieren wie die Einsen, tragen aber nichts zum Ergebnis bei. Teilprodukte müssen zwischengespeichert werden, um sie anschließend zu addieren. Kapitel 5: Darstellung von Daten im Rechner Seite 50 Multiplikation - Verbesserung der Methode Formal ist das Schulrechenverfahren wie folgt beschreibbar: Sei x der Multiplikant, y=(yn-1,…y0) der Multiplikator, dann ist In der Praxis ist es sinnvoll jeden Term zu addieren, sobald er generiert wurde, so dass die Multiplikation wie folgt ausgeführt wird: Idee: Sukzessive Addition von Zweierpotenzen des Multiplikators ist durch Addition und Schiebeoperationen realisierbar. Kapitel 5: Darstellung von Daten im Rechner Seite 51 Multiplikation - Schaltung Wir beschränken Eingaben auf halbe Wortlänge. Dann kommt man ohne ein doppelt so langes Register zur Aufnahme des Ergebnisses aus. Akku soll am Ende das Ergebnis enthalten. Rechtsshift des Multiplikators steuert Addierwerk. Linksshift des Multiplikanden sorgt für Potenzierung (und anschliessende Addition auf die richtigen Stellen des Akkus). Kapitel 5: Darstellung von Daten im Rechner Seite 52 Multiplikation - Funktionsweise der Schaltung Die Multiplikation mit der Schaltung läuft wie folgt ab: Der Akku-Inhalt wird gelöscht. Die rechten 4 Bits des X-Registers nehmen den Multiplikanden auf, Y den Multiplikator. Eine zusätzliche Logik (in der Abbildung nicht gezeigt), überprüft das Bit Null von Y. • Ist dieses Bit =1, dann wird der Inhalt von X zum Akku-Inhalt addiert. • Ist das Bit =0, dann bleibt der Akku-Inhalt unverändert. • Anschließend wird der Inhalt von Y um ein Bit nach rechts, der Inhalt von X um ein Bit nach links geschoben und wieder Bit 0 von Y überprüft. Stehen im Register Y nur noch Nullen, ist die Rechnung beendet, das Ergebnis der Multiplikation steht im Akku. Kapitel 5: Darstellung von Daten im Rechner Seite 53 Beispielablauf Multiplikation Akku löschen, Operanden laden: Hier X = 1101, Y = 1001 Akku X Kapitel 5: Darstellung von Daten im Rechner Y Seite 54 Beschleunigung der Schulmethode Die dargestellte Multiplikation nach der Schulmethode lässt sich beschleunigen. Verwendung eines Addiernetzes mit schneller Carry-Berechnung Zwischenspeicherung des bei der Addition auftretenden Übertrags und Verarbeitung desselben erst in späteren Schritten Malnehmen des Multiplikanden in jedem Schritt nicht nur mit einem Bit des Multiplikators, sondern mit k > 1 benachbarten Bits. Grundlage schneller Multiplizierer sind schnelle Addierer. Betrachten zunächst die Carry-Save-Multiplikation, weitere Spezialverfahren nächste Woche. Kapitel 5: Darstellung von Daten im Rechner Seite 55 Carry-Save-Multiplikation Wir verwenden als Addiernetz nun den Carry-Save-Adder und entwerfen damit ein Carry-Save-Multiplikationsnetz. Man kann die Multiplikation vierstelliger Dualzahlen in tabellarischer Form darstellen: Die Multiplikation lässt sich nun durch Addition der Zeilen implementieren. Bei vier Summanden reicht dazu ein zweistufiges CarrySave-Addiernetz aus. Kapitel 5: Darstellung von Daten im Rechner Seite 56 Multiplikation mit größerer Stellenzahl Wenn die Stellenzahl der Operanden sehr groß ist, kann man mit einer baumartigen Anordnung der CSA eine schnelle Reduktion der Anzahl der Summanden herbeiführen (sogenannter Wallace-Tree): Tiefe der Schaltung ist logarithmisch in der Stellenzahl. Kapitel 5: Darstellung von Daten im Rechner Seite 57 Rechenoperationen auf Gleitkommazahlen Die bisherigen Verfahren und Schaltungen lassen sich auch zur Multiplikation von Gleitkommazahlen verwenden, indem man die Mantissen und die Exponenten nacheinander in der Hardware verarbeitet: Zur Multiplikation sind die Mantissen zu multiplizieren und die Exponenten zu addieren. Bei der Division werden die Mantissen dividiert, die Exponenten subtrahiert. Bei der Addition und der Subtraktion muss man darauf achten, dass die Operanden den gleichen Exponenten haben, dafür wird üblicherweise der Operand mit dem niedrigsten Exponenten „denormalisiert“. Durch die feste Wortlänge und die festgelegte Anzahl von Bits für Mantisse und Exponent gelten für Gleitkommazahlen im Rechner nicht alle üblichen Rechengesetze. Kapitel 5: Darstellung von Daten im Rechner Seite 58 Rechenoperationen auf Gleitkommazahlen Beispiel: Beispiel:Assoziativgesetz Assoziativgesetz 3 5 5 Sei Seix=+0,1567 x=+0,1567⋅ ⋅10 103, ,y=+0,4322 y=+0,4322⋅ ⋅10 105, ,z=-0,4323 z=-0,4323⋅ ⋅10 105 So gilt für (x+y)+z: x+y = +0,1567 ⋅ 103 +0,4322 ⋅ 105 Für x+(y+z): y+z = +0,4322 ⋅ 105 -0,4323 ⋅ 105 = +0,0015 ⋅ 105 +0,4322 ⋅ 105 = -0,0001 ⋅ 105 = +0,4337 ⋅ 105 = -0,1000 ⋅ 102 (x+y)+z = +0,4337 ⋅ 105 -0,4323 ⋅ 105 x+(y+z) = +0,1567 ⋅ 103-0,1000 ⋅ 102 = +0,0014 ⋅ 105 = +0,1567 ⋅ 103-0,0100 ⋅ 103 = +0,1400 ⋅ 103 = +0,1467 ⋅ 103 Also Alsofolgt: folgt:(x+y)+z (x+y)+z≠≠x+(y+z). x+(y+z).Das DasAssoziativgesetz Assoziativgesetzgilt giltalso alsonicht! nicht! Kapitel 5: Darstellung von Daten im Rechner Seite 59 Rechenoperationen auf Gleitkommazahlen Für das Rechnen mit Gleitkommazahlen gelten die folgenden Regeln: Seien dann gilt: Kapitel 5: Darstellung von Daten im Rechner Seite 60 Rechenoperationen auf Gleitkommazahlen Sollen diese Operationen mit den bereits bekannten Addierwerken durchgeführt werden, muss die Behandlung von Exponenten und Mantissen im Allgemeinen softwaremäßig erfolgen. Für eine Addition sind das die folgenden Operationen: Vergleich der Exponenten Shift der Mantisse der Zahl mit dem kleineren Exponenten Ausführung der eigentlichen Addition Ggf. Normalisierung des Ergebnisses. Um dies über die Hardware zu steuern und damit die Ausführungszeit von Gleitkomma-Operationen in ähnliche Dimensionen wie FestkommaOperationen zu bringen, sind viele Rechenanlagen mit separaten GleitkommaRechenwerken (Floating-Point-Prozessoren) ausgestattet. Diese verfügen über hinreichend lange Register zur Aufnahme von Operanden bzw. Ergebnissen, über eine geeignete Verknüpfungslogik und über ein eigenes Steuerwerk. Kapitel 5: Darstellung von Daten im Rechner Seite 61 Overflow und Underflow Bei Gleitkomma-Operationen können sowohl Over- als auch Underflows auftreten: Beispiel: Beispiel:OverOver-und undUnderflow Underflow 0,622 ⋅ 102 Die Subtraktion 0,622 + 0,381 ⋅ 102 - 0,599 Die Addition ⋅ 102 ⋅ 102 1,003 ⋅ 102 0,023 ⋅ 102 führt zu einem Overflow, da die Mantisse führt zu einem Underflow, da eine Null des Ergebnisses eine signifikante Stelle unmittelbar rechts vom Komma auftritt. links vom Komma besitzt. Beides Beidesist istdurch durcheine eineNormalisierung Normalisierungzu zubeheben. beheben. Da der Zwang zur Normalisierung evtl. ein Abschneiden signifikanter Stellen erfordert, ist in der Gleitkomma-Arithmetik mit Rundungsfehlern zu rechnen. Kapitel 5: Darstellung von Daten im Rechner Seite 62 Ausblick Als nächstes (aus dem Skript von Spaniol, Popien, Schuba): weitere Varianten der beschleunigten Multiplikation Division Anschliessend: Darstellung alphanumerischer Zeichen (Oberschelp/Vossen, Kap 5.4) Am Donnerstag: Weiterführung des MMIX-Crash-Kurses… Kapitel 5: Darstellung von Daten im Rechner Seite 63