Elektronik für Plasma- und Laserlichtquellen - KIT

Werbung

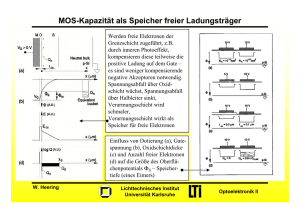

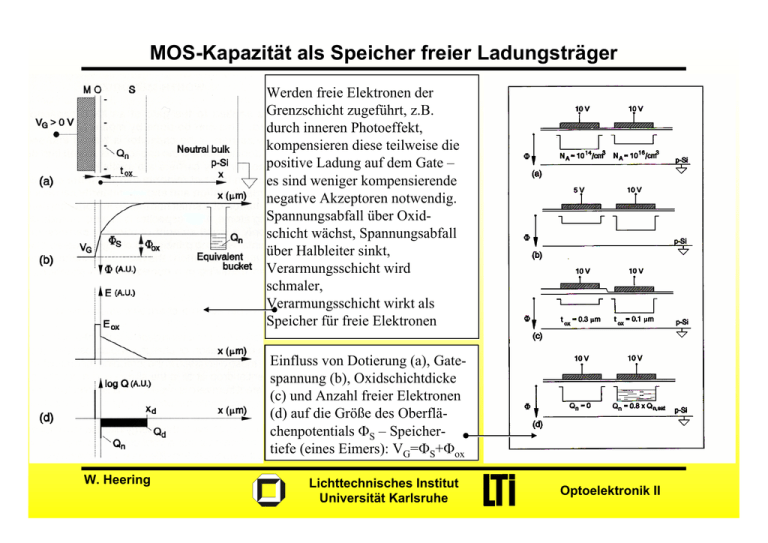

MOS-Kapazität als Speicher freier Ladungsträger Werden freie Elektronen der Grenzschicht zugeführt, z.B. durch inneren Photoeffekt, kompensieren diese teilweise die positive Ladung auf dem Gate – es sind weniger kompensierende negative Akzeptoren notwendig. Spannungsabfall über Oxidschicht wächst, Spannungsabfall über Halbleiter sinkt, Verarmungsschicht wird schmaler, Verarmungsschicht wirkt als Speicher für freie Elektronen Einfluss von Dotierung (a), Gatespannung (b), Oxidschichtdicke (c) und Anzahl freier Elektronen (d) auf die Größe des Oberflächenpotentials ΦS – Speichertiefe (eines Eimers): VG=ΦS+Φox W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Ladungstransport längs einer CCD (charge coupled device) Transport von Minoritätsträgern in einer CCD durch Folge digitaler Pulse – Mehrphasentakt – an den CCD-Gates Beachte: Während des Ladungstransports unter den 4 Elektroden bleiben Gate 1 und Gate 4 auf demselben Potential, damit keine Überlagerung mit anderen Ladungspaketen und keine Verluste auftreten. Transport bestimmt durch • thermische Diffusion von Ladungsträgern • selbst induzierte el. Felder aufgrund von Trägerdichtegradienten • aufgeprägte laterale Streufelder (fringing fields) erzeugt durch die Gate-Spannungsfolgen und abhängig von der Gate-Geometrie W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Transportzeit und Transporteffizienz a)Verlauf des Oberflächenpotentials ohne laterales Feld b)Verlauf des Oberflächenpotentials mit lateralem Feld für eng benachbarte, kurze Elektroden Ef,min minimales laterales Feld – nimmt ab mit der Dotierung und Elektrodenlänge Nur für eine hinreichend lange Transportzeit (800 ps) ist die Transporteffizienz – Anteil einer durch eine CCD-Zelle transportierten Ladung – groß (99,99%). Das laterale Feld verkürzt erheblich die Transportzeit und (bei gegebener Transportzeit) die Transporteffizienz. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Transportparameter • Relativ langsam ist die durch π2 D n 8 Q n (t) = 2 Q n (0) exp(− t) 2 π 4L beschriebene thermische Diffusion • Schneller Transport, allerdings nur der aller ersten Ladungen, durch selbstinduziertes Feld • Sehr schneller Transport des Hauptteils des Ladungspakets durch das aufgezwungene laterale elektrische Feld • Hohe Transporteffizienz durch hohe laterale Felder und Minimierung von als Haftstellen wirkenden Oberflächenzuständen Transportzeit für eine Transporteffizienz von 99,99% als Funktion der Elektrodenlänge L und mit Dotierung als Parameter W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Optimierung des lateralen elektrischen Feldes Potentialverläufe in p-Si in verschiedenen Abständen von dem SiO2-Si Interface Das minimale laterale el. Feld unter einer Elektrode wird in einer gewissen Tiefe (B) maximal! Dies (Waldner und Esser 1972) führte zur BCCD, buried channel CCD mit tiefer gelegenen Speicherorten. Vorteilhaft auch weniger Verluste durch OberflächenTrapping. BCCD im Vergleich zum SCCD: höhere Transporteffizienz, potentiell höhere Taktfrequenzen, geringeres Rauschen (weniger Ladungsaustausch mit Oberflächenzuständen) W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II BCCD – buried channel CCD a)und b): SCCD (surface CCD) – Potentialverlauf ohne freie Elektronen bzw. mit freien unter der Oberfläche gespeicherten Elektronen c) und d): BCCD – ohne bzw. mit freien Elektronen – oberflächliche n-Dotierung im pSubstrat so gewählt, dass ohne freie Elektronen die n-Schicht völlig verarmt ist an Elektronen; nicht kompensierte positive Ionen heben das Potentialmaximum ΦCh im Si-Bulk über die Gate-Spg. VG. Beim BCCD liegt das Potentialmaximum nicht an der Grenzfläche sondern tiefer im Bulk! Die Speicherung freier Elektronen im BCCD verkleinert ΦCh und bringt sie näher der Oberfläche; Ladungen nicht völlig gespeichert im „vergrabenen“ Kanal, sondern auch unter Oberfläche. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Speicherfähigkeit einer MOS-Kapazität - Sättigungsladung a) El. Ersatzschaltbild eines SCCD-Elements Maximal unter der Oberfläche speicherbare Ladung: Q n,sat = Cox (VG − VT ) VT Gate-Spannung, bei der die Minoritätsträgerdichte in der Inversionszone - erreichbar mit freien Ladungsträgern (hier Elektronen) unter der Oberfläche - gleich der Majoritätsdichte im Bulk wird b) El. Ersatzschaltbild eines BCCD-Elements. Maximale Ladung, die auf der Oxidkapazität Cox und der seriellen Kapazität CD1 der oberen Verarmungsschicht gespeichert werden kann: C C Q n,sat = ox D1 (VG − VT ) kleiner ca. um den Faktor 3 als beim SCCD! Cox + CD1 W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II CCD Eingangsstruktur Als analoger Speicher verschiedener Ladungen benötigt die CCD einen Eingang. Eine Diode am Eingang liefert der Folge von MOS-Kapazitäten, welche an Majoritäten (Löchern) stark verarmt sind, Minoritätsträger (Elektronen) in der gleichen Weise, wie dies am Source-Eingang eines MOS-FET geschieht – im Beispiel liefert VS = 5 V freie Elektronen in die Potentialsenke unter dem Gate mit VG = 10 V. Eine elektrische Spannung wird in ein Ladungspaket umgesetzt. Die maximal einkoppelbare Ladung ist wieder gegeben durch Q n,sat = Cox (VG − VT ) Ein 4-Phasen oder 3-Phasen (Standard) oder 2Phasen oder 1+1/2-Phasen Takt treibt die Ladung zum Ausgang. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Floating-diffusion Ausgang t1: Auszulesenes Ladungspaket sei unter Φ3 gespeichert und MOS-FET schaltet VDD durch zum Diodenausgang. Floating diffusion Ausgang wird dann rückgesetzt auf ≈VDD und am Sourcefolgerausgang erscheint nahezu dieselbe Spannung t2: Rücksetzender MOS-FET wird gesperrt, Diodenausgang floatet. Fallende Flanke von ΦR koppelt über die Gate-Kanalkapazität Cp in das n+-Gebiet eine kleine Elektronenladung und senkt damit ein wenig Vout t3: Φ3 wird abgesenkt und die auszulesene negative Ladung wird unter das Gate mit konstanter Gleichspannung VDC verschoben. Die nun auf der floatingdiffusion Kapazität zusätzlich gespeicherten Elektronen senken das Potential des n+-Gebietes weiter ab. Vout erhält einen Treppenverlauf. t4: Das nächste Ladungspaket wird unter das Gate Φ3 getaket. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Elektrische Beschreibung des floating-diffusion Ausgangs Gate-Kanal Kapazität Floatingdiffusion Kapazität Timing-Diagramm des Auslesens am floating-diffusion Ausgang ∆V * out Qn = CFD + C p * ∆Vout = GSF ∆Vout W. Heering Ersatzschaltbild des floatingdiffusion Ausgangs Parasitäre Gate-Kanal Kapazität Cp sollte möglichst klein sein. Gleiches wird von CFD gefordert, um den Spannungshub pro Elektron groß zu erhalten. Erreicht wird heute: CFD + Cp = 10 – 15 fF und damit 15 – 10 µV/Elektron vermindert um die Spannungsverstärkung GSF ≈ 0,9 Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Picture element - pixel Bildelement eines Bildsensors: a) n+- p Übergang – in Sperrrichtung gepolte Photodiode. b) MOS-Kapazität mit semitransparenter Elektrode – extern induzierter n-p Übergang Trennung der durch Strahlung erzeugten Elektron-Lochpaare durch das Feld des n-p Übergangs. Elektronen werden eingefangen unter der SiO2-Schicht, Löcher abgeführt in das p-Substrat. Die Integration der in der Expositionszeit erzeugten Photoladungen erfolgt auf der in Sperrichtung gepolten, elektrisch isolierten Kapazität des Übergangs. Durch die generierte Photoladung sinkt die Spannung über der Kapazität und verringert sich die Breite des Verarmungsgebiets. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II Auslesestrukturen für eine Photodiode a) MOS-FET mit Ausleseleitung (Video) Vorteil: Einfache Herstellung Nachteil: MOS-FET verbindet die kleine PixelKapazität mit der großen Kapazität der Videoleitung – Dies bedingt stärkeres Rücksetzrauschen. b) Analoges CCD-Schieberegister Nachteil: Aufwendigere Technologie Vorteil: Photoladung wird in die kleinere Kapazität der Ausgangsdiode transferiert. Rücksetzrauschen ist geringer! Obige Photodiode kann auch durch MOS-Kapazität ersetzt werden. W. Heering Lichttechnisches Institut Universität Karlsruhe Optoelektronik II