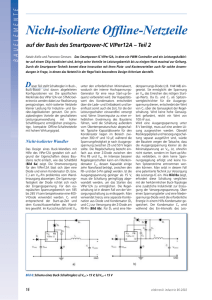

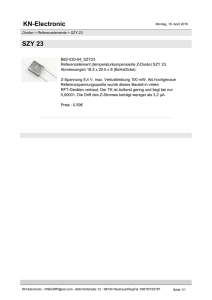

Resonanz-Tunneldioden und Heterobipolartransistoren in

Werbung