K1 PC Technik Schueler

Werbung

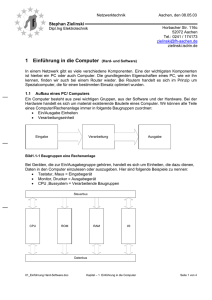

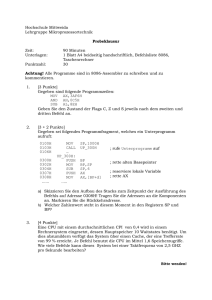

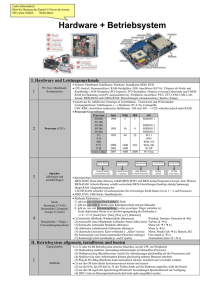

BITS (Bet r euung von Infor mat ions- und Telekommunikat ionsSyst emen) BITS (Betreuung von Informations- und TelekommunikationsSystemen) Kapitel 0 Ausgewählte Grundlagen Informationseinheiten Einheit Bit Zustände Bewertung 1 Bit 1 Bit 2 kleinste Informationseinheit 1 Nibble 4 Bit 16 hexadezimale Darstellung 1 Byte 8 Bit 256 Standardinformationseinheit 1 Word 16 Bit 65.536 häufig verwendet 1 Doubleword 32 Bit 4.294.967.296 häufig verwendet duales/binäres Zahlensystem 16er Stelle 8er Stelle 4er Stelle 2er Stelle 5. Bit 4. Bit 3. Bit 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 2 0 0 0 1 1 3 0 0 1 0 0 4 0 0 1 0 1 5 0 0 1 1 0 6 0 0 1 1 1 7 0 1 0 0 0 8 0 1 0 0 1 9 0 1 0 1 0 10 0 1 0 1 1 11 0 1 1 0 0 12 0 1 1 0 1 13 0 1 1 1 0 14 0 1 1 1 1 15 1 0 0 0 0 16 2. Bit 1er Stelle 1. Bit Zahlenwert Makro - Größenordnungen Bezeichnung Abk. Zahlwort Bedeutung Kilo K Tausend gr. chilioi: tausend Mega M Million gr. megas: große Zahl Giga G Milliarde gr. ho gigas: riesige Zahl Tera T Billion gr. to teras: ungeheuer groß Peta P Billiarde gr. petanünnein: alles umfassen Exa E Trillion gr. exa: über alles Zeta Z Trilliarde ? Yotta Y Quadrillion ? Micro - Größenordnungen Bezeichnung Abk. Zahlwort Bedeutung milli m tausendstel lat. millesimus: micro millionstel gr. mikros: nano n milliardstel gr. ho nanos: zwerghaft klein piko p billionstel ital. pico: sehr klein femto f billiardestel dän.-norw.: femten: 15 atto a trillionstel dän.-norw.: atten: 18 zepto z trilliardestel ? yocto y quadrillionstel ? der tausendste Teil klein, unbedeutend Yotta Zeta Exa Peta Tera Giga Mega Kilo milli micro nano piko femto atto zepto yocto Größenordnungen Zahlen = Quadrillion 1.000.000.000.000.000.000.000.000 = Trilliarde 1.000.000.000.000.000.000.000 = Trillion 1.000.000.000.000.000.000 = Billiarde 1.000.000.000.000.000 = Billion 1.000.000.000.000 = Milliarde 1.000.000.000 = Million 1.000.000 = Tausend 1.000 = tausendstel = millionstel = milliardstel = billionstel = billardstel = trillionstel = trilliardstel = quadrillionstel 0,001 0,000.001 0,000.000.001 0,000.000.000.001 0,000.000.000.000.001 0,000.000.000.000.000.001 0,000.000.000.000.000.000.001 0,000.000.000.000.000.000.000.001 Kapitel 1 Technische Grundlagen Schematisches Rechnermodell • Grundlegender Aufbau und Funktionsweise eines Computersystems • Erläuterung von Fachbegriffen Schematisches Rechnermodell Elementarkomponenten 1. 2. 3. 4. 5. CPU ROM RAM Ein-/Ausgabe-Geräte Bussystem (Daten-, Adress- und Kontrollbus) 6. Stromversorgung 7. Taktgeber System Block Diagramm Mainboard Layout Der Befehlszyklus (1) Die vom Computer erbrachten Ergebnisse beruhen auf einer sich wiederholenden Arbeitsweise, kurz Befehlszyklus genannt: 1. Hol-Phase: Der Prozessor holt sich aus dem RAM einen Befehl (z.B. add = addiere) und eventuell zugehörige Daten ( 3 und 4) in sein Rechenwerk. 2. Verarbeitungs-Phase: Die Daten werden gemäß dem Befehl verarbeitet (3+4=7). 3. Speicher-Phase: Das Ergebnis (7) wird in den RAM zurückgespeichert.Der Befehl (add) ist jetzt abgeschlossen und der Prozessor holt sich den nächsten Befehl aus dem RAM (siehe Hol-Phase). Würde der Prozessor das Ergebnis (7) nicht zurückspeichern, dann würde es durch den nächsten Befehl überschrieben werden und damit verloren gehen. Der Befehlszyklus (2) Dieser Vorgang wiederholt sich ständig und das Ergebnis sieht man auf den Ausgabegeräten (Monitor, Drucker ...). Standard Formfaktoren Abmessungen (B x T) Dualboards eATX 330 x 305 mm ATX 305 x 244 mm Mini-ATX 284 x 208 mm Micro-ATX 244 x 244 mm Flex-ATX 229 x 191 mm Mini-ITX (VIA) Micro-ITX gesockelt 170 x170 mm gelötet 170 x170 mm BTX (Intel) Balanced Technology Extended • Mainboard wird statt links, jetzt rechts eingebaut (warum auch immer?) • RAM-Riegel liegen parallel zu den Einsteckkarten, was die Luftzirkulation verbessern soll • das I/O Shield wurde unverständlicher Weise etwas kleiner ausgelegt • Fazit: die Änderungen sind nur geringfügig und rechtfertigen eigentlich keinen neuen Standard; hier stehen offensichtlich finanzielle Interessen im Vordergrund. BTX-Layout ATX- / BTX-Panelvergleich ATX / BTX Vergleich Ergänzungen • • • • • • • • • Clock (Taktgeber) Unterschied CPU/Controller Timer, RTC, CMOS Cache Unterschied SRAM/DRAM (Flash-) ROM BIOS Treiber Welche „-ware“? Clock (=Taktgeber) --Jede Komponente benötigt Arbeitstakt --Synchronisation der Komponenten --Legt Arbeitsgeschwindigkeit fest -Takt aus FSB andere Komponenten leiten Takt ab Unterschied P./Controller (1) Prozessor Controller hohe Leistungsfähigkeit universell übergeordnet komplexer Befehlssatz verarbeitet Daten geringere Leistungsfähigkeit spezialisiert untergeordnet simpler Befehlssatz transferiert Daten Der Controller entlastet die CPU von routinemäßigen Aufgaben! Unterschied P/Controller (2) Komplexität 1. Prozessor 2. Controller 3. Gatearray 4. Addierer 5. FlipFlop 6. Transistor Integrationsdichte Timer (=Zeitgeber) RTC (=Echtzeituhr) CMOS (1) =Complementary Metal Oxide Semiconductor = komplementärer Metalloxidhalbspeicher CMOS (2) Cache (allgemein) Unterschied SRAM / DRAM SRAM DRAM statisch dynamisch (permanente Stromversorgung) (periodischer Ladestrom) mehrere (ca. 4-6) Transistoren 1 Transistor und 1 Kondensator geringere Speicherdichte = teuer höhere Speicherdichte = billig ca. 3-10x schneller langsamer Prozessorcache Hauptspeicher, (Geräte-)Cache (IBM will SRAM des CPU-Caches durch DRAM ersetzten) (Flash-) ROM Doppeldeutigkeit „BIOS“ 1. Boot- bzw. Grundbetriebssystem 2. ROM-Baustein, in dem sich das BIOS befindet • Gerätetreiber (1) Software zum Ansteuern eines (Hardware-) Gerätes. Der Gerätetreiber steht zwischen Anwendung und Betriebssystem einerseits und der Hardware andererseits. Die Anweisungen der Programme werden vom Treiber in den Maschinencode der Hardware-Elektronik übersetzt. Gerätetreiber laufen nicht im geschützten User-Mode sondern im Kernel-Mode des Betriebsystems d.h. ein abgestützter Treiber stürzt den ganzen Rechner ab. Daher muß ein Treiber unbedingt stabil laufen, was mittels eines WHQL Zertifikats (=Windows Hardware Quality Labs) garantiert werden soll. • Alltagsbeispiel: Gebrauchsanweisung für ein Gerät (Videorecorder, Küchenmaschine, Handy...) Treibersuche (2) Benötigt man für ein Gerät einen Treiber, kann man sich zahlreicher Tools bedienen, die ein Gerät genau identifizieren. Ist das Gerät genauer spezifiziert kann im Internet der korrekte Treiber gesucht werden. – Sisoft Sandra 2004 www.sisoftware.net – Everest Home Edition www.lavalys.com – www.driverguidetoolkit.com Welche „-ware“? Applikationware Systemware Firmware Hardware Anwendungsprogramme Betriebssyteme Herstellerprogramme für deren Geräte, im ROM-Speicher eines jeden Gerätes gespeichert. alles, was man anfassen kann RAM Standards Latenzzeit - Bandbreite Latenzzeit = die Reaktionszeit vom Ram Bandbreite = gibt den Datendurchsatz an SDRAM 100MHz*64Bit = 800 Byte/s 133MHz*64Bit = 1064 Byte/s DDR-RAM 100MHz*128Bit = 1600 Byte/s 133MHz*128Bit = 2028 Byte/s RD-RAM RAM Tabelle Speichertyp Bezeichnung Taktfrequenz in MHz Transfers pro Takt Bandbreite MB/s SD-RAM PC100 100 1 800 SD-RAM PC133 133 1 1064 DDR-RAM PC1600/PC200 100 2 1600 DDR-RAM PC2100/PC266 133 2 2100 RD-RAM PC600 300 2 1200 RD-RAM PC600 300 2 2400 (2 Kanäle) RD-RAM PC700 355 2 1422 RD-RAM PC800 400 2 1600 RD-RAM PC800 400 2 3200 (2 Kanäle) Zukünftige Speichertechnologien DDR-2 • offener Standard • Einführung 1/2004 • basiert technisch auf DDR-1 1,8V, kürzere Lantenzzeiten, On-Die-Terminierung höherer Takt Bustakt Datentakt Bandbreite 266 MHz PC533 PC2-4300 333 MHz PC667 PC2-5300 DDR-3 • Einführung ca. 2005 • Speicherbustakt ca. 500MHz • GDDR-3 (DDR-2 für Grafikkarten) – Einführung Mitte 2003 – Speicherbus 1-1,6 GHz – Datenraten bis 51GByte/s möglich Dual-Channel-Technik Es müssen 2 Speicherbänke mit jeweils einem „registred“ Speicherbaustein bestückt sein, jede Bank hat einen eigenen 64 Bit Datenebus inklusive Speichercontroller ( 128 Bit Busbreite) z.B. 2 x PC2100 4,2 Gbyte/s schneller als Rambus mit 2 Kanälen (3,2 Gbyte/s) AMD: Nforce2 Chipsatz (von Nvidia) Intel: Granite Bay Chipsatz (Intel 7205) SIS: P4X600 NB RAM QBM (Quad Band Memory) QBM (Quad Band Memory) In einem Speicherbaustein werden 2 DDR Speicher integriert, die über 2 separate und 90° verschobene Taktsignale getaktet werden. Vorteile: schmaleres Businterface, geringere Pin-Anzahl, geringe Änderung am DDR-Platinenlayout Entwickler: Kentron Technology; VIA will ein entsprechendes Board (PT880) auf den Markt bringen Bisher noch nicht am Markt NB Ram Chipsatz Chipsatz (1) Chipsatz (2) - Die northbridge verbindet die schnellen Komponenten (CPU, CD/DVD und AGP) Die Southbridge verbindet die interne „langsame“ Peripherie (HD, CD/DVD, USB, PS/2, PCI,...) Früher wurden North und Southbridge über den PCI – Bus miteinander verbunden, heute durch propietäre Chip to Chip Lösungen: o VIA V.Link, 256 MB/s o SIS MuTIOL, 1GB/s (MultiThreaded-I/O-Link) o INTEL Hub-Link, 256MB/s AMD Hyper-Transport, 6,4GB/s Der Chipsatztreiber - Die Grundfunktion des Chipsatzes werden in der Regel vom BS richtig erkannt: o Automatisches einrichten von Controllern, Schnittstellen, Steckplätzen,... o Grundfunktionen von onboard Grafik, Sound Der Chipsatz wird benötigt um: o Dem BS mitzuteilen auf welche Art und Weise nicht unterstützte Geräte angesprochen und genutzt werden können o Integrierte Funktionen im BS für AGP/DIE/USB... zu umgehen, damit neue/verbesserte Funktionen realisiert werden können(höhere Performance und Stabilität) Der Chipsatztreiber enthält alle Treiber, um das zugehörige Board optimal zu nutzen AC'97 Standard AC97 (1) Audio Codec Prozessoren über Intel hatte 1997 die Idee, daß moderne genügend Leistungsreserven verfügen, um neben den normalen Aufgaben auch noch ein paar Analogdaten zu berechnen. Hieraus entstand die AC97 Spezifikation (=Audio Codec 1997; Codec= Coder/Decoder ) für Audio- und Modemdaten (AMR-Slot). AC97 implementiert Audio- und Modem-Funktionalität. Die AC97-Spezifikation ist eine 2 Chip-Architektur und besteht aus einer Analog-Codec- und einer Digital-ControllerKomponente, die durch ein AC-Link-Interface miteinander verbunden sind. AC97 kann selbst keine Audiodaten berechnen! AC97 (2) Audio Codec Der AC97-Codec-Chip (aktuell häufig ein Realtek ALC650) besteht aus: 1. mehreren AD- und DA-Wandlern: digitalisieren bzw. analogisieren Töne, 2. einem Kodierer/Dekodierer: stellt die Töne in einem bestimmten Format dar und 3. einer Steuerlogik: steuert Audiodatenströme zu ihrem Zielgerät. AC97 vereinheitlicht daher auch die Ansteuerung von Mikrophon-Eingang, LineIn, LineOut ... Der AC97-Link stellt die Verbindung zwischen AC97-Codec und AC97-Controller her, der sich in der Southbridge befindet. Der AC97-Controller ist nicht weiter spezifiziert. Je nachdem wie viele Codec-Features er unterstützen soll schwankt seine Komplexität. AC97 (Bild) Audio Codec AC97 (Blockschaltbild) Audio Codec onboard Sound (1) Bei der Sounderzeugung sind eine Reihe von Komponenten beteiligt: 1. ADW (Analog/Digital Wandler) wandelt die digitalen Audiodaten in analoge um (und umgekehrt) und gibt sie an Lautsprecher oder Verstärker weiter, formt also das Ausgangssignal und damit die Qualität der Audiowiedergabe. 2. AC97 (Audio Codec 97) bezeichnet eine standardisierte HW-Schnittstelle, die analoge/digitale Audiodatenströme codiert und steuert, aber nicht erzeugen oder berechnen kann! 3. CPU, Soundprozessor oder SoundKarte erzeugt und verarbeiten Audiodaten. Das Audioendergebnis wird von der schwächsten Einheit dieser Kette bestimmt! onboard Sound (Bild1) onboard Sound (2) Um Kosten niedrig zu halten wird auch beim onboard-Sound gespart. Im schlimmsten Fall werden billige (=schlechte) AD-Wandler verbaut. Diese Einheit wandelt den digitalen Ton in den analogen hörbaren Ton um. Hat man hier Verluste, dann nützt der beste SoundProzessor nichts! Befindet sich kein Sound-Prozessor im Chipsatz, dann muß die CPU den Sound berechnen. Dadurch gehen bis zu 20% CPU-Leistung und normalerweise auch Soundeffekte verloren! onboard Sound (3) Ist ein Sound-Prozessor vorhanden, dann stellt sich die Frage nach den unterstützten Features (EAXModi,...). Diese Lösung entlastet die CPU und unterstützt im Günstigsten Fall auch aufwendigere Soundeffekte. nVidia verbaut auf ihren NForce2-Chipsätzen eine leistungsfähige APU (=Audio Prozessing Unit), die einer hochwertigen Soundkarte gleichkommt. Mit dem Gütesiegel "Soundstorm" bestätigt nVidia ein hochwertiges Soundsystem einschließlich guter ADWandler, so daß der Sound einer hochwertigen Soundkarte gleichkommt. Audioerzeugung Es gibt 3 Arten der Soundgenerierung: 1) CPU im Chipsatz befindet sich kein Soundprozessor, d.h. CPU wird mit der Sounderzeugung stark belastet 2) interner Soundprozessor in der SB ist dem AC97 ein Soundprozessor nachgeschaltet der den Sound erzeugt, CPU wird vom Gröbsten entlastet 3) externer Soundprozessor (Soundkarte) die Soundgenerierung wird von dieser Einheit geleistet, d.h. CPU wird fast nicht belastet nForce APU Audio Processing Unit Wegen den durchgängig schwachen onboard Lösungen will sich nVidia mit seinen neuen nForce-Chipsätzen von der Konkurrenz abheben. Das eigene Gütesiegel "Soundstorm" weist auf eine gute OnboardSound-Leistung hin.Neben der AC97-Einheit und guten AD-Wandlern ist eine APU mit hoher Leistungsfähigkeit integriert, die MCPD und damit Dolby unterstützt. nForce APU Audio Processing Unit sich in der Neben diesem Codec befindet Southbridge die eigentliche SoundRecheneinheit, die je nach Hersteller über mehr oder weniger Features verfügt. Der Codec ist somit nur der Handlanger der Sound-Einheit. Onboard Soundlösungen sind schlichter als separate Sound-Karten. Der nForce-Chipsatz bietet mit der MCP-D (=Dolby) eine leistungsfähige onboardSoundeinheit. Fazit Generierung AC97+CPU AC97+APU Audigy CPU-Last Ergebnis 17-20% schlechteste Soundfunktion max. 7% entspricht hochwertiger Soundkarte 2-3% aktuelles Optimum EAX (Environmental Audio Extension) wird bislang nur vom Audigy-Chip unterstützt, alle anderen Lösungen sind softwarebasiert! EAX sieht 4 Lautsprecher und einen Subwoofer zur 3DRaumklangerzeugung vor. Außerdem werden auch Nachhall- und Echoeffekte unterstützt. Zusatz-Slots AMR, CNR, ACR AMR, CNR, ACR (1) Wie bei AC97 angesprochen verwendet Intel die CPULeistungsreserven zur Erzeugung von Audiodaten. Mittels dieser (Audio-) Daten lassen sich Softmodems und andere Geräte (AMR, CNR, ACR) realisieren. AMR-Slot (=Audio Modem Riser) oder integrierter Chip für (Audio-) und Modem-Funktionalität. CNR-Slot (=Communication and Network Riser) für Audio-, Modem-, LAN- und USB-Karten. Die Absicht war international verschiedene Internet-Zugänge (MultichannelAudio, analoge V.90-Modems, Heimnetzwerke über Telefonleitungen und 10/100-Ethernet-Netze) zu unterstützen. CNR hat AMR abgelöst. ACR-Slot (=Advanced Communication Riser) erweitert CNR um DSL-Funktionalität. AMR, CNR, ACR (2) Der Hintergedanke war, die Mainboardhersteller nur eine Sorte von Mainboards produzieren zu lassen und somit Kosten zu sparen. Je nach Kundenwunsch (Audio-,Modem-, LAN-...) sollte das Board mit einer passenden CNR Karte bestückt werden. CNR-Karten sind sehr selten und werden fast nur an OEM-Kunden geliefert. Privatkunden werden so gut wie nicht bedient. AMR, CNR, ACR (3) AMR, CNR, ACR (4) AZALIA High Definition Audio Standard High Definition Audio Standard (1) Intel ersetzt mit HDAS v1.0 den 10 Jahre alten AC97 Standard. – höhere Qualität bei Sprach- und Kommunikationsapplikationen (Dolby Logo) – flexible Bandbreite bis zu 192 kHz, 32bit, Multichannel Audio (Audio-CD: 44 kHz, 16 Bit!) (Samplingfrequenz: HDAS 192 kHz, AC97 48 kHz , Mensch 40 kHz, Richtungsbestimmung 80 kHz; Samplingtiefe: 16 Bit = 96dB, menschliches Ohr norm. 45dB, max 80dB! kein Lautsprecher wird dieses Signal übertragen können) – flexiblere Gerätekonfiguration Einführung Ende 2004, i915 (Grantsdale), i925X (Alderwood), u.a. Chipsätze. HDAS ist eine audielle Komplettlösung, die auch auf Microsofts UAA (=Universal Audio Architecture) abgestimmt ist und damit viel umfassender ist als AC97. High Definition Audio Standard (2) Leistungsmerkmale: – Genügend Bandbreite für DVD-Audio – Dolby Digital EX und 7.1 Surround-Sound – Hohe Bandbreite mit bis zu 192 kHz, 32-Bit MultichannelAudio – Spielraum für zukünftige hochqualitative Audio-Formate – Verbesserte Unterstützung von Multichannel-ArrayMikrofonen für eine hochqualitative Eingabe – Dynamisch zugewiesene Bandbreiten – Multistream-Fähigkeit – Dynamische Konfiguration von Steckverbindungen – vollständig automatische Erkennung angeschlossener Geräte HDAS: 7.1 Surround Sound HDAS: Multichannel-Eingabe Multichannel-Array-Mikrofone ermöglichen eine hochqualitative Eingabe bessere Spracherkennung und Voice over IP HDAS: Multistreaming Mehrere Audio-Streams können unabhängig voneinander an unterschiedliche Geräte gesendet werden. HDAS: Dynamische Konfiguration Dynamische Konfiguration von Steckverbindungen: Mehrere Audio-Streams können unabhängig voneinander an unterschiedliche Geräte gesendet werden. HDAS: automatische Geräte Erkennung Audio Plug&Play Diese "Audio Plug&Play" genannte Funktion ermöglicht es ein Audio-Gerät an jedem passenden Anschluß zu betreiben. Dies wird mittels folgender Vorgehensweise erreicht: Erkennung: ein angeschlossenes Gerät wird über die veränderten elektrischen Eigenschaften des benutzten Anschlusses gefunden. Bestimmung: mittels einer elektrischen Methode und den elektrischen Geräteeigenschaften wird das Gerät korrekt erkannt. Neu-Konfiguration: ermöglicht das Umkonfigurieren zwischen ADC und DAC und erlaubt die Funktionsmodifizierung für jeden Anschluß. Audio Begriffe Audio Begriffe • S/PDIF-Connector (Sony/Phillips Digital Interface): digitale Audio-Schnittstelle und damit verlustfrei; koaxiale oder optische Ausführung. • Wave: digitalisierter Sound, aktuell bei Computerspielen verwendet. • MIDI (=Music Instruments Digital Interface): künstlich erzeugter Sound (FM-Synthese). • Wavetable: verbesserte FM-Synthese (real aufgenommene Instrumente), die auch über Midi abgespielt wird. MIDI und Wavetable werden heute bei Computerspielen nicht mehr verwendet. Bootvorgang Überblick Bootvorgang • • • Nach dem einschalten: Takterzeugung , CPU springt ins Bios-Rom, Post wird ausführt Das Bios startet den Urlader und somit wird das Bootmedium gesucht Wenn eine HDD oder CD zum Booten gefunden wurde wird der MBR gelesen und evtuell ein Bootloader gestartet... Anzeige und Bedeutung Erklärung Bootangaben Bus No Nr. des PCI-Busses Die Anzahl der PCI-Busse wird vom PCI_BIOS_PRESENT zurückgegeben. Die Busnummer wird zur Selektion einer PCI-/AGP-Karte bei Funktionen wie READCONFIGURATION-WORD oder auch WRITE-CONFIGURATUION_BYTE benötigt. Device No. Gerätenummer (0-31) Kennzeichnet eine PCI-Device und wird bei den Funktionen FIND_PCI_DEVICE, READ_CONFIGURATION_BYTE vom BIOS zurückgegeben. Die Nummer hängt vom Steckplatz ab. Func. No. Funktionsnummer (0-7) Kennzeichnet die Anzahl der implementierten Funktionen (Multi Function Device) und wird bei den Funktionen FIND_PCIDEVICE, READ_CONFIGURATION_BYTE in den unteren drei Bits vom BIOS zurückgegeben. Vendor No. Herstellerkennung Device-ID Gerätekennung Device Class Geräteklasse (0 bis 4095) IRQ Interrupt Request Wird von der PCISIG vergeben und ist direkt im Configuration Space (00/01h) als 16Bit-Wert abgelegt. Diese 16-Bit-Kennung (02/03h im Configuration Space) wird vom Gerätehersteller angegeben und erscheint als Gerätebezeichnung in der Device-Liste. Jedes PCI-Gerät sollte einer Device Class zugeordnet sein. Sie dient zur Identifizierung de Geräte mit Hilfe der BIOS-Funktion FIND_PCI_CLASS_CODE. Kennzeichnet in diesem Zusammenhang die Interrupt-Nummer der betreffenden PCIDevice. PCI-Devices können sich einen IRQ-Kanal teilen (Shared Interrupt). Der POST Power-On-Self-Test Der Post arbeitet in 2 Schritten: 1.) Test und Einstellung der zentralen Hardware Cpu, Bios, Cmos, Ram bis 64kb, Diverse Controller, 2.) Test und Einstellung der erweiterten Hardware GraKa, Ram über 64kb, serielle/parallele Schnittstellen, Floppy und Hdd controller ... Nach dem erfolgreichen abschließen des post´s gibbet nen piepston. Wenn der Post erfolgreich abgeschlossen ist dann startet der Loader. PIEP, over ! Loader (Urlader) Der Loader ist dafür verantwortlich das Bootmedium nach dem im MBR vorhandenen Bootstreploader zu durchsuchen. Floppy Bios -Post -(enter bios) CD -Loader HDD Bootstraploader, Starter und Kernel • Sollte klar sein ! Das BIOS • Ist das OS vor dem OS • Stellt ua plug&pray zur Verfügung CMOS, der BIOS-Speicher • Die einstellungen die im bios getätigt wurden werden im cmos gespeichert. • Beim einschalten des rechners wird das cmos initialisiert (die daten werden geladen) Setup-Menü Hersteller Es gibt 3 große BIOS-Hersteller 1. 2. 3. 4. AMI (=American Megatrends Incorporated) AWARD Phoenix (=Siemens), daneben gibt es noch "MR" und andere kleinere. CMOS-Setup-Menüpunkte (1) • Is klar ! CMOS-Setup-Menüpunkte (2) 4. Integrated Periphals – Einstellungen zu Onboard-Schnittstellen • • • • • • • • • • Primäre/sekundäre E-IDE-Schnittstelle FDC-Schnittstelle Serielle Schnittstelle PS/2 Schnittstelle Infrarot-Schnittstelle (IrDA=Infrared Data Association) Parallele Schnittstelle USB Firewire DVI-Schnittstelle ... DVI (Digital Visual Interface) • • • • DVI (=Digital Visual Interface) bezeichnet die Spezifikation einer Schnittstelle zur Übertragung von digitalen (hohe Bildqualität) und analogen Bilddaten. Standardmäßig bei TFT (=Thin Film Transistor); ist bei CRT (=Cathode Ray Tube) auch möglich ( besseres Bild), aber intern würde der Monitor einen D/A-Wandler benötigen, was den Preis erhöhen würde und sich daher bislang nicht durchgesetzt hat. DVI-I (=DVI-Integrated) unterstützt sowohl digitale als auch analoge Übertragung. In der Zukunft soll auch Sound über diese Schnittstelle übertragen werden. CMOS-Setup-Menüpunkte • Power Management (3) – Einstellung von APM (=Advanced Power Management) und ACPI (=Advanced Configuration and Power Interface) • PC Health Status – Angaben zu CPU- und System Temperatur, Spannungen ... • Andere Menüpunkte – Frequency/Voltage, Password, PnP/PCIConfigurations, Speicheroptionen ... BIOS Update / Flashing • Gründe für ein Flashing – Inkompatibilitäten mit HW-Erweiterungen (modernere CPU/RAM) • Nachträglich vom Hersteller behobene Fehlfunktionen APM (Advanced Power Management) APM APM ist ein "einfacher" Stromsparmechanismus, der praktisch nur durch das BIOS gesteuert wird. Für verschiedene Geräte (Monitor, Festplatten, ...) lassen sich Inaktivitäts-Zeitspannen festlegen, nach deren Ablauf diese Geräte in den Stand-byModus geschaltet werden. Durch ein Aufweckereignis (Maus, Tastatur, ...) wird der Ruhezustand aufgehoben. Der "alte" Powermanagement-Standard existiert nach wie vor neben ACPI und funktioniert auch unabhängig vom Betriebssystem, weil er (s.o.) durch das BIOS erledigt wird! ACPI (Advanced Configuration and Power Management Interface) ACPI Allgemein • Acpi bezeichnet allgemein die idee, daß sich elektronische greäte gegenseitig aktivieren/deaktivieren können. • Acpi ist weiter entwickelt als apm ACPI für PC • Hauptziele von acpi sind eine • Verbesserte Standardisierung der HW Konfiguration • Effektivere Energiesparfunktionen • Mehr Komfort und einsatzmöglichweiten ACPI Grundanforderungen • Pflichtausstattung sind ein Power- und ein Sleep Taster oder ein Taster mit einer Doppelfunkion • Eine über die Echtzeituhr gesteuerter Einschaltmechanismus ACPI Voraussetzungen ACPI ist recht kompliziert und muß von allen beteiligten Komponenten unterstützt werden! Dazu gehören: - Mainboard - Bios - Geräte (Steckkarten mit wdm treiber) - Betriebssystem (win 98/Me/XP, linux ab 2.4) ACPI Advanced Configuration Regelt umfassend die art und weise wie gräte Leistungsmerkmale • Suspend to Disk: es wird ein image vom aktuellen ram auf die hdd geschriben • Suspend to RAM: es wird ein image vom aktuellen ram stand in den ram geladen (rechner braucht dauerhaft strom) • Wake On LAN: pc via netzwerkkarte booten • Modem Ring On: das selbe wie wakeup on lan bloß mit modem ... Wake up On LAN ACPI-Funktionsweise • Damit ACPI diese Funktionen umsetzen kann, müssen einige Softwaremodule in das Betriebssystem integriert werden, da das BS den besten Überblick über das Gesamtsystem kennt. Nach Bedarf werden nicht benötigte Komponenten in energiesparende Modi versetzt. Insgesamt kennt ACPI • 4 globale Systemzustände • 6 Sleep-Modi • 4 Device-Modi • 4 Prozessor-Modi ACPI-Bestandteile • hardwareseitig (Mainboard) – ACPI-Registersatz – ACPI-BIOS – ACPI-Tabelle • Betriebssystem – OSPM (Operating System Direct Power Management) – ACPI-Treiber/AML-Interpreter ACPI-Systemkomponenten Globale Systemzustände G0 Working Der Rechner arbeitet normal. G1 Sleeping Der Rechner ist im Sleep-Modus und verbraucht wenig Energie. Ist in S0-S5 unterteilt. G2 Soft Off Mechanical Off G3 Rechner abgeschaltet, 5-Volt-Stand-by führt noch Spannung. Der Rechner ist komplett abgeschaltet (vom Netz getrennt). Sleep-Modi S1 Das System schläft, ist aber mit geringer Latenz wieder aufzuwecken. Kein System-Kontext geht verloren (weder CPU noch Chipsatz müssen reinitialisiert werden). S2 Wie S1, die CPU und ihr Cache sind abgeschaltet, das Betriebssystem ist für das Restaurieren verantwortlich. S3 (Suspend to RAM) Wie S1, die CPU, alle Caches und der Chipsatz sind abgeschaltet. Die Board-Hardware sorgt dafür, daß alle Speicherinhalte erhalten bleiben, und das Betriebssystem restauriert die restlichen Systemzustände. S4 (Suspend to Disk) Das System verbraucht kaum noch Energie, alle Board-Komponenten sind abgeschaltet. Das Betriebssystem ist für die Restaurierung des Systemzustands verantwortlich. S5 Soft off wie G2 Device Modi D0 D1D2 Full on D3 Off Das Gerät ist betriebsbereit. Das Gerät ist im Sleep-Modus. Der Unterschied zwischen D1 und D2 liegt lediglich in dem niedrigeren Energieverbrauch und der höheren Einschalt-Latenz bei D2. Welche Maßnahmen welchem Zustand zugeordnet werden, ist geräteabhängig. Das Gerät ist per Software, nicht aber mechanisch abgeschaltet. Das Betriebssystem reinitialisiert es bei Bedarf. Prozessor-Modi C0 Der Prozessor führt Befehle aus. C1 Der Prozessor befindet sich im Halt-Modus und kümmert sich weiterhin um die Cache-Integrität. C2 Speziell für MP-Systeme. Eine CPU befindet sich im Halt-Modus, alle anderen arbeiten weiter. C3 Der Prozessor ist quasi abgeschaltet. Er kümmert sich nicht mehr um die Cache-Integrität. Das Betriebssystem muß alle CPU-Register und die Caches restaurieren wenn ein Interrupt oder ein Busmaster-Zugriff auf den Hauptspeicher erfolgt. Sleep-Modi Bemerkung S0 S1 Working "unvollständiges" Stand-by" System arbeitet normal CPU steht, Cache-, Register- und RAM-Inhalte werden gehalten (RAM im Self-Refresh, RTC läuft) d.h. der System-Kontext geht nicht verloren! dadurch müssen weder CPU noch Chipsatz reinitialisiert werden sondern können sofort "weiterarbeiten". Festplatten und Monitor aus, Netzteil an! hoher Stromverbrauch bis 40W!, Weckzeit: wenige Takt-Zyklen! IntelMobilprozessoren schalten so schnell zwischen S0 und S1 um, daß bereits zwischen 2 Tastendrücken während der Eingabe in ein Textverarbeitungsprogramm umgeschaltet wird! Wird ACPI nicht 100% unterstützt, dann schalten PC's statt in S3 in S1. Die Weckzeit liegt dann allerdings bei wenigen Sekunden (5-10Sek.) S2 Wie S1, aber CPU und ihr Cache sind abgeschaltet, das Betriebssystem ist für das Restaurieren verantwortlich. Suspend to S3 RAM STR, Wie S1, diesmal aber "richtiges Stand-by", die CPU, alle Caches und der Chipsatz sind abgeschaltet. Das Netzteil in Soft-Off (5V Stand-by) versorgt den RAM mit Strom (bei Stromausfall gehen Daten verloren!); beim Aufwachen restauriert das Betriebssystem die restlichen Systemzustände. Stromverbrauch 10-30W! Weckzeit: 5-10Sek. Suspend to S4 Disk STD, wie S3 mit dem Unterschied , daß der RAM abgeschaltet ist und sein Inhalt vorher als Image-Datei auf der Festplatte gesichert wurde (kein Datenverlust durch Stromausfall), die Soft-On Überwachungsfunktionen des Mainboards sind aktiv. Wird der PC vom Strom getrennt, dann wird normal gebootet, findet er dabei das Image wird wie bei S3 hochgefahren. Stromverbrauch 5-10W! Weckzeit: ca. 20Sek. S5 Soft Off wie G2, Betriebssystem fährt herunter und schaltet Netzteil in Soft-OffZustand ACPI Anmerkungen • wird der PC über mehrere Sitzungen im "Standby" gehalten, dann fragmentiert der HS (Performanceverlust); mittels eines normalen Neustarts ist behoben. • Der "Ruhezustand" (hibernate, entspricht S4) von Windows (vor XP) ist nicht! an ACPI gebunden. Es handelt sich um eine unabhängige Umsetzung, so daß diese Funktion* auch auf Standard-PC's bzw. im APM-Modus funktioniert. • Bei XP entspricht der "Ruhezustand" S4 STD. * unterschiedliche Angaben in den Qellen ACPI-Systemzustände 2 Lithium-Ionen-Akkus Lithium-Ionen-Akkus • Sind sehr empfindlich. • Akku immer voll laden lassen und komplett leeren lassen • Kühl lagern ! (erhält die lebensdauer) Überblick Akku-Technologien Akku-Technologie Li-Ion / Polymer Zellen-Spannung (V) 3,6 - 3,7 1,2 1,2 2,0 1,4 Kapazität (mAh) kleiner 1000 1000 2000 größer 1000 k. A. Spezifische Energie (Wh/kg) 90-110 40-60 60-80 30-50 200-350 Energiedichte (Wh/l) 250-350 80-200 200-300 60-100 bis 500 Entladeschluss (V) 2,5 0 0,8 1,7 k. A. Ladeschluss (V) 4,1-4,2 nicht definiert nicht definiert 2,4 k. A. Ladezyklen/Lebensdauer 500-800 500-800 300-500 200-300 k. A. Verlauf der Entladespannung bei Belastung nahezu waagerecht gering, 10 Prozent stark fallend k. A. gering, kleiner 10 Prozent k. A. Selbstentladung (pro Monat) NiCd NiMH mittel, 20 Prozent gering fallend hoch, 30 Prozent fallend Pb Zn-Luft Entladerate/Belastbarkeit (x-fache der Nennkapazität) 3 20 10 10 hoch Schnellladung (Min) 120 10 30 k. A. k. A. Material der Minus-elektrode LiC6 Cd MH Pb Zn Material der Plus-elektrode LiCoO2 NiOOH NiOOH PbO2 C (O2) Empfohlener Ladezustand bei langer Lagerung geladen (voll) entladen geladen geladen entladen (deaktiviert) Mechanische Belastbarkeit sehr gering sehr hoch mittel hoch k. A. Preis sehr teuer günstig teuer sehr günstig k. A. Bussysteme FSB (=Front Side Bus) FSB (=Front Side Bus) • Verbindet cpu und Northbridge (damals auch cache und Hauptspeicher) • Der fsb erhält seinen takt direkt vom Taktgeber. • Alle anderen Geräte leiten ihren takt mittels eines (normalerweise) festen Multiplikators von diesem ab. • Der FSB Datenbus ist 64 bit breit. FSB Datendurchsatz (Nur Intel Systeme) Physischer Takt in MHZ (Bus-Grundtakt) 133 Datentakt (4 x physischer Takt) 166 667 200 800 533 FSB Taktverteilung 1/4 Exkurs Konfigurationsressourcen Jedes Divice benötigt zwingend IRQ und Port als Konfigurationsressourcen um in das System integriert werden zu können. IRQ (Interrupt Request) Durch einen Interrupt meldet ein Gerät dem InterruptController und dieser cpu, daß es einen Datentransfer durchführen will. Über Ports wird der gewünschte Datenaustausch durchgeführt. (wie im netzwerk) entweder über i/o mapped i/o memory oder memory mapped i/o. Generell steht „Port“ für jede Art von logischer Schnittstelle. Einem Gerät kann ein DMA-Kanal (Direct-Memory-Access) zugewiesen werden, der Datentransfers wesentlich schneller und ohne Belastung der CPU durchführen kann. Siehe Hefter ! Detail: i/o mapped i/o i/o mapped i/o (wird von AT’s preferiert) 16 Adressleitungen des Adressbusses werden für die Adressierung von Ports "missbraucht" (d.h. Speicherstellen, die sich in den Geräten selbst befinden), dadurch bleibt der Hauptspeicher unberührt; Unterschied Speicherstelle 000F2H und Port 00F2H. Der Kontrollbus legt mit seinen Steuersignalen fest was angesprochen wird. i/o-Einheit Port-Adresse Com1 3F8H Com2 2F8H HD-Controller 1F0H FD-Controller 3F0H LPT's 3BCH Tastatur 60H … … Durch die 16 Adressleitungen wird ein 64KB Adressraum aufgespannt, der bei weitem nicht vollständig genutzt wird! Detail: memory mapped I/O Das Gerät legt einen oder mehrere Hauptspeicherbereich fest, die als Zwischenspeicher dienen. Sind Daten z.B. von der CPU zum Gerät übertragen, dann schreibt die CPU diese Daten in diese HS-Bereiche. Das Gerät kann sich dann bei gegebener Zeit die Daten selbst aus dem HS hohlen. Vergleich der Port-Modi i/o mapped i/o memory mapped i/o geringe Datenmengen umfangreiche Datenmengen unbelasteter Hauptspeicher belasteter Hauptspeicher direkte (synchrone) Kommunikation indirekte Kommunikation belastetes Bussystem entlastetes Bussystem Detail: DMA-Transfer DMA wird mit Hilfe von Datenleitungen realisiert, die von Steckkarten direkt zum RAM führen. Es existiert nur eine DMALeitung auf dem Motherboard! Die Indexierung dient lediglich zur Koordinierung der Zugriffe auf diese. DMA Nr. 0-3 8 Bit DMA Nr. 4-7 16 Bit Initiiert der Prozessor einen DMA-Datentransfer so wird der Prozessor vom DMA-Controller für die Dauer des Datentransfers vom Bus getrennt. Der DMAController verbindet bei einem RAM-I/O-Transfer die beiden Einheiten über den Datenbus direkt miteinander. Dadurch führt der DMA-Controller den Datentransfer mit wesentlich höherer Geschwindigkeit aus als es der Prozessor könnte! Während des Transfers kann die CPU nicht auf den HS zugreifen! DMA = Direct-Memory-Access Vorteile = hohe Geschwindikeit, Busmastering Mit Busmastering wird die Fähigkeit eines Gerätes ausgedrückt, für eine bestimmet Zeit die Kontrolle über den Bus zu übernehmen (das Gerät wird Busmaster) und eigenständig Datentransfers durchführen zu können. Es benötigt dazu weder CPU noch einen anderen Controller. PIC Programmable Interrupt Controller • Der Pic verwaltet bis zu 16 HW-IRQ´s (maskierbare irq´s) • Die einzelnen irq´s unterliegen einer (nummern-) Priorität siehe Bild/Tabelle • Dabei haben niedrige Nummern eine hohe und hohe Nummern eine niedrige Priorität • Treffen gleichzeitig mehrere irq´s ein, dann maskiert (ausblenden) die niedrigste Nummer automatisch alle höheren, bis dieser Irq vollständig abgearbeitet ist • Eine noch niedrige Nummer kann den grade ablaufenden irq ebenfalls unterbrechen! Traditionelle PIC-Kaskade Die Umleitung des INT-Signals vom Ausgang des Slaves (Nr.2) auf den IRQ2Eingang des Masters (Nr.1) führt zu einer Verschiebung der Prioritäten bei der Bedienung der Interrupt-Anforderungen: Da der Eingang 2 des Masters eine höhere Priorität als die Eingänge 3 bis 7 besitzt, "drängeln" sich alle InterruptAnforderungen, die über den Slave laufen, nach vorne! Insgesamt könnten 64! INT's über kaskadierte PIC's verwaltet werden. PIC Programmable Interrupt Controller CPU local APIC Device (PIC) Southbridge = Advanced PIC (in der CPU) Unterbrechungsanfrage An dieser Stelle befindet sich ein Programm (Geräte Treiber, IRQ Holder, Bios Routine), das für die Steuerung dieser irq Leitung zuständig ist. Nach der Abarbeitung des irq´s kehrt die cpu wieder zu ihrer unterbrochenen Arbeit zurück. IRQ-Management PIC Programable Interrupt Controller • Der PIC verwaltet bis zu 16 HW-IRQ's (maskiebare IRQ's). • Die einzelen IRQ's unterliegen einer (Nummern)Priorität siehe Bild/Tabelle. • Dabei haben niedrige Nummern eine hohe und hohe Nummern eine niedrige Priorität. • Treffen gleichzeitig mehrere IRQ's ein, dann maskiert (blendet aus) die niedrigste Nummer automatisch alle höheren, bis dieser IRQ vollständig abgearbeitet ist. • Eine noch niedrigere Nummer kann den gerade ablaufenden IRQ ebenfalls unterbrechen! Traditionelle PIC-Kaskade Die Umleitung des INT-Signals vom Ausgang des Slaves (Nr.2) auf den IRQ2Eingang des Masters (Nr.1) führt zu einer Verschiebung der Prioritäten bei der Bedienung der Interrupt-Anforderungen: Da der Eingang 2 des Masters eine höhere Priorität als die Eingänge 3 bis 7 besitzt, "drängeln" sich alle InterruptAnforderungen, die über den Slave laufen, nach vorne! Insgesamt könnten 64! INT's über kaskadierte PIC's verwaltet werden. IRQ-Belegung Master Slave Verwendung / Steckplatz IRQ0 Timer NEIN IRQ1 Tastatur NEIN IRQ2 Slave-PIC NEIN IRQ8 IRQ10 Echtzeituhr NEIN Aufruf des Interrupt-Handlers von IRQ2 IRQ9 erscheint als IRQ2!; JA reserviert JA IRQ11 reserviert JA IRQ12 reserviert JA IRQ13 Coprozessor NEIN IRQ14 HD-Controller JA IRQ15 reserviert JA IRQ3 COM2 JA IRQ4 COM1 JA IRQ5 LPT2 JA IRQ6 Diskettencontroller JA IRQ7 LPT1 JA IRQ9 PIC Programmable Interrupt Controller APIC in CPU;Interrupt Request ICC Unterbrechungsanfrage Auf dem Mainboard und in den Steckplätzen befinden sich Interrupt-Leitungen. Will ein Gerät bspw. einen Datenaustausch durchführen löst es seinen Interrupt aus. HW-IRQ's werden ihrer Priorität entsprechend (je niedriger um so höher) abgearbeitet. Wird ein IRQ angefordert, übernimmt eine spezielle Routine (ISR=Interrupt-Service-Routine) die Steuerung des Systems, d.h. alle CPU-Inhalte werden im Stapelspeicher gespeichert. Dann wird in der IRQ-Vektor-Tabelle die korrespondierende Adresse ermittelt und angesprungen. An dieser Adresse befindet sich ein Programm (Geräte-Treiber, IRQ-Holder, BIOSRoutine), das für die Steuerung dieser IRQ-Leitung zuständig ist. Nach der Abarbeitung des IRQ's kehrt die CPU wieder zu ihrer unterbrochenen Arbeit zurück. Interrupt-Konflikt Da normalerweise jedes Gerät einen Interrupt benötigt, die Zahl der zur Verfügung stehenden Interrupts aber knapp ist, kam es früher vor, daß bei der Konfiguration 2 Geräten eine InterruptLeitung zugeteilt wurde. Das hatte aber mit Sicherheit einen Absturz des Systems zur Folge und mußte unbedingt verhindert werden! Heute wird ein solcher Fall durch die automatische Konfiguration verhindert. Sollte es aber trotzdem zu unlösbaren Konflikten kommen, dann wird eine Karte (Gerät) einfach abgeschaltet. Interrupt-Sharing Durch moderne Komponenten (ab ca. 1999/200) wie Acpi und BS ist es möglich einen Interrupt mehreren Geräten zuzuweisen, ohne das es zu Konflikten kommt. Mit einen APIC können statt 16 nun 24 Interrups zu Verfügung gestellt werden. I/O APIC (1) Advanced Programmable Interrupt Controller Der I/O APIC ist ein neu entwickelter INT-Controller für Mehrprozessor-Systeme. Er kann theoretisch beliebig viele INT's verwalten (zur Zeit 24, plus 8* INT's). Dies erleichtert die früher oft kritische Konfiguration umfangreich ausgestatteter PC-Systeme. Der APIC-Modus kann nur mit einem Mehrprozessor-BS genutzt werden (Win 2000, XP, Linux, Unix ...)! Für Singleprozessor-BS (Win Me/98 und davor) kann er auch im PIC-Modus betrieben werden. * von den 8 neu hinzugekommenen Interrupts können allerdings nicht unbedingt alle verwendet werden! I/O APIC (2) Advanced Programmable Interrupt Controller Der I/O APIC ist in MP-Systemen für die Koordinierung/Aufgabenverteilung der CPU's unabdingbar. Auch ältere Mainboard verfügen bereits über einen I/O APIC. Eventuell muß der APIC-Modus erst noch im BIOS "enabled" werden! I/O APIC (Bild) Advanced Programmable Interrupt Controller I/O APIC-Blockbild Problemlösung • überflüssige Geräte abschalten – – – – – serieller COM-Port (IRQ 3, 4) 2 INT's PS/2 Maus (IRQ 12) 1INT falls nicht benötigt USB-Ports abschalten wenn USB-Drucker parallel-Port abschalten (IRQ 7) 1INT bei separater Soundkarte nicht nur "Onboard Sound" abschalten sondern auch "Game Port Adress" und "Midi Port Adress" (Probleme bei Soundkarte: 2 INT's, INT 5 für DOS und hoher INT für PCI, da PCI traditionell hohe INT's belegt!) • Anordnung der Komponenten – INT Request Tabelle – try and error IRQ-Holder (1) Ab Win95 B kann man im Gerätemanager den Eintrag: "IRQ-Holder for PCI-Steering" (="IRQ-Holder für PCI-Steuerung") finden. Dieser Eintrag ist immer in Verbindung mit anderen Geräten auf einem Interrupt zu finden! Dabei handelt es sich nicht um einen Ressourcen-Konflikt, sondern es zeigt an, daß das BS die von den PCI-Geräten genutzten Interrupt-Leitungen steuern kann, so daß Probleme mit Ressourcen-Konflikten vermieden werden. IRQ-Holder (2) Der IRQ-Holder zeigt an, daß • sich mehrere PCI-Geräte einen Interrupt teilen können, Voraussetzung dafür ist, daß die betreffenden Gerätetreiber Interrupt-Sharing unterstützen. • der betreffende Interrupt für PCI reserviert ist. • bei neueren Systemen (ab 1999) die InterruptVergabe mittels BS/ACPI für die Plug&Play PCI-Karten vorgenommen wird. PCI(-X) (=Periphal Component Interconnect) Aufbau Das PCI-System Besteht aus drei Teilen: 1. Host-Brige mit Cache-DRAM-Controller stellt die Verbindung zwischen CPU und PCI-Bus her, Dabei werden CPU Zyklen in PCI-Zyklen umgesetzt und Umgekehrt; ist von der CPU entkoppelt 2. Expansion-Bus-Interface Diese Komponente stellt die Verbindung zu einem Zweiten Bussystem her, z.B. USB, FireWire, PS/2, ... 3. Data-Path-Unit Stellt die Leitungen und Slots dar, and die die Geräte angeschlossen sind Funktionsweise • unabhängiges Bus-System, – d. h. es kann an beliebige CPU's angeschlossen werden, wobei nur die PCI-Host-Bridge angepasst werden muß. • Kommunikation über Initiator und Target – INITIATOR übernimmt Kontrolle über die Bus-Steuerleitungen (Busmaster) und KONTAKTIERT, TRANSFERIERT (immer nur ein einziger aber beliebig langer Burst-Transfer! Der nächste Einzeltransfer kann erst bei der nächsten Arbitrierung durchgeführt werden!) UND TERMINIERT die Verbindung zum TARGET. Im Hintergrund läuft eine (Hidden-)Arbitrierung die über die zeitliche Zuteilung des Busses entscheidet. PCI unterstützt Bus-Mastering für mehrere Geräte zur gleichen Zeit, aber nie 2 Buszuteilungen gleichzeitig! Beginnt der Transfer nicht innerhalb der ersten 16 Zyklen, dann wird dem PCI-Gerät der Busmaster von der Arbitrierung entzogen. • Daten- und Adressbus werden gemultiplext – Dies spart teure Leiterbahnen • PCI-Bridge kann Einzeltransfers zu schnellen und effizienten BurstTransfers zusammenfassen. Leistungsmerkmale • Verwaltung von max. 10 Geräten – als Geräte zählen: die HOST-Bridge, das Expansion-Bus-Interface, PCI-Gerät, PCISlot, eine PCI-to-PCI-Bridge, eine PCI-to-XYZ-Bridge • Plug & Play-Unterstützung – das PCI-BIOS (im ROM-BIOS), konfiguriert automatisch alle erkannten Plug&Play-Devices, bei einem unlösbaren Ressourcenkonflikt wird einfach eine Karte abgeschaltet (sehr selten); die PCI-Int's #A bis #D werden normalerweise den traditionellen Int's 9 bis 12 zugeordnet. • Interrupt-Sharing – durch die Busmasterfähigkeit (jede Karte kann den PCI-Bus selbst verwalten) der Plug&PlayKarten können 2 Karten einem Interrupt zugeordnet werden. • PCI Concurrency (=Zusammenwirken) – – Unter PCI-Concurrency versteht man, daß CPU und PCI-Bus parallel auf den Hauptspeicher oder den L2-Cache zugreifen können. Der Chipsatz sorgt dafür, daß die Zugriffe sauber aufeinander abgestimmt erfolgen. Einige Chipsätze erlauben es, die PCI-Concurrency abzuschalten, da nicht jede Karte diesen Modus unterstützt. CPU und PCI-Master arbeiten dann nicht verschachtelt, statt dessen muß die CPU dann bei einem Master-Transfer über den PCI-Bus immer warten, bis dieser abgeschlossen ist. PCI-X • PCI-X wurde entwickelt um einem gesteigerten Leistungsbedürfnis nachzukommen, den das herkömmlich PCIBussystem nicht mehr erfüllen konnte. • PCI-X ist abwärtskompatibel zu PCI, parallel und nicht skalierbar • PCI-X 2.0 unterstützt folgende Modi: 1 x 133MHz 0,99GB/s, 2 x 133MHz 1,99GB/s, 4 x 133MHz 3,97GB/s PCI Standards PCI-Versionen im Überblick PCI-Version PCI 1.0/2.0 PCI 1.1/2.1/2.2 PCI 2.3 PCI-X1.0 PCI-X-2.0 PCI-X-3.0 max. Busbreite (Bit) 32 64 64 64 64 64 max. Taktrate (MHz) 33 66 66 133 533 1066 max. Bandbreite (GByte/s) 0,127 0,508 0,508 0,99 3,97 7,95 Slots pro Bridge 4 2 2 1 1 1 Spannung (Volt) 5 5/3,3 3,3 3,3 3,3/1,5 3,3/1,5 Einführungsjahr 1993 1994/99 2002 1999 2003 2003 Ergänzungen • PCI 2.1 = Ab dieser Revision kann der Bus auch mit 100MHz betrieben werden. • PCI 2.2 = Hot Plugging, ACPI • Arbeiten 33- und 66MHz-Karten im Mischbetrieb, dann läuft der ganze Bus permanent nur mit 33MHz. • Um das Slot-Anzahl-Problem zu lösen gibt es PCI-to-PCI-Bridges, die mehrere PCI-Busse parallel oder hintereinander verbinden können. PCI-Express (=Periphal Component Interconnect) PCI-Express (1) Codename:3GIO (=3. Generation I/O, nach ISA und PCI); Arapahoe) geplante Markteinführung 2004, soll mittelfristig PCI/PCI-X und AGP ablösen. • PCI-Express basiert auf einer seriellen Punkt-zu-Punkt-Verbindung, die als Link bezeichnet wird. • Ein Link besteht aus 1,4,8,16,32 Lanes. • Eine Lane besteht aus zwei unidirektionalen differentiell betriebenen Leitungspaaren. Damit kann ein Leitungspaar Daten senden und das andere zeitgleich Daten empfangen. PCI-Express Lane (1) PCI-Express Lane (2) PCI-Express Slot PCI-Express (2) • durch diesen Aufbau werden nur wenige Leitungen (Pins) benötigt und gleichzeitig fallen die (Slot)-Abmessungen geringer aus • die variable Anzahl der Lanes ermöglicht die Anpassung an reale Leistungsbedürfnisse. • Eine Lane erreicht bei 2,5GHz Grundfrequenz 2Gbit/s/250MB/s Nutzdaten in jede Richtung. (bis 10GHz sind geplant) • bei voller Ausbaustufe erreicht PCI-Express maximal eine Bandbreite von 19,1 GB/s PCI-Express (3) PCI-Express stellt einen neuen Funktionsbaustein (Switch) zur Verfügung. Dieser verwaltet mehrere PCIe-Endgeräte über eine intelligente Flusskontrolle. Während PCI-Geräte alle am gemeinsamen Bus hängen und um die Buszuteilung konkurierren, werden bei PCIe die PCIe-Geräte über den Switch verwaltet. Daraus ergibt sich eine Entzerrung des Datenverkehrs. Der Switch unterstützt isochronen Datenfluß sowohl direkt von einem Gerät zum anderen ohne Umweg über den HOST, als auch vom Host zum Endgerät. Um Softwarekompatibilität zu gewährleisten besitzt jeder Ein-/Ausgang des Switch eine interne virtuelle PCI-to-PCIBridge (diese können bei nicht benötigter PCI-Kompatibilität entfallen!). PCI-Express Switch PCI Express Mainboardlayout PCI-Express Vorteile • • • • 100% Softwarekompatibel zu PCI, niedrige Kosten wegen weniger Leiterbahnen, ist als abwärtskompatible Variante zu PCI verfügbar, Skalierung, je nach benötigter Bandbreite können bis 32 Lanes betrieben werden, • mehrere Datentransfers können innerhalb des PC-Systems (wegen uni-direktionaler Leitungen) parallel ablaufen, • flexible Architektur, eignet sich damit als universeller Interconnect für Peripheriegeräte (Dockingstation zu externen Geräten) und Verbindungsmedien (z.B. Firewire, USB, SCSI, Chip-to-Chip, Board-to-Board, leistungsfähige Steckkarten (z.B. 10Gbit-LAN). PCI-Express Nachteile • hohe Latenzzeit – daher ungeeignet für Prozessorkommunikation, Arbeitsspeicher oder Clusterzusammenschluß für diesen Bereich eignet sich Hypertransport von AMD • 20% Nutzteilverlust durch 8Byte/10ByteKodierung PCI-Express Ausblick PCI-Express wird schon 2004 in den Markt eingeführt. Ein allgemeiner Umstieg von PCI auf PCI-X als neuen Standard entfällt. Experten schätzen die Lebensdauer von PCIExpress bei Markteinführung auf 10 Jahre. AGP (=Accelerated Graphics Port) AGP • ursprünglich dazu gedacht Texturen von der Grafikkarte in den "billigen" Ram auszulagern, wird aber ab 8MB kaum gemacht. • AGP (3. Quartal 1997) basiert auf dem PCI 2.1 Standard, stellt aber einen eigenständigen von PCI unabhängigen Bus dar. • heute dient AGP zur schnellen Anbindung der GraKa an den Ram (höhere Bandbreite als PCI-Bus) • Hauptvorteil von AGP: Entlastung des PCI-Busses • erst bei 3D-Anwendungen (Spiele, CAD...) wird vom 2D-Modus in den 3D-Modus und in die höheren Transfermodi 2x, 4x, 8x geschaltet! • 3D-Grafik benötigt 3 mal soviel Speicher wie 2D-Grafik: – angezeigtes Bild Front Buffer – aufzubauendes Bild Back Buffer – Tiefeninformation für jedes Pixel Z-Buffer • AGP 8x: Schwachpunkt Signalqualität; Geschwindigkeitsvorteil wird bei weitem nicht genutzt AGP-Pro / AGP-Standards • AGP-Pro ist um 40 zusätzliche Kontaktleisten erweitert (nur zur Stromversorgung! Eine "Pro"-Karte kann damit bis 110W statt der normalen 25W (früher) oder 40W (heute) verbrauchen). • AGP-Pro wird vorzugsweise im professionellen Bereich eingesetzt. NAGP-Standards orm Bandbeite 1x Technik 32 Bit, 66 MHz, 266 MB/s; 2x 533 MB/s, da beidflankig 4x > 1 GB/s, 8x > 2GB/s bei 2x, 4x, 8x werden die Strobe-Leitungen höher getaktet, der Grundtakt von 66,67MHz bleibt immer gleich AGP-Slots USB (=Universal Serial Bus) USB (1) (Universal Serial Bus) USB Takt absolut bulk isochron 1.1 Low Speed 1,5 Mb/s 16 KB/s % 1.1 Full Speed 12 Mb/s 1,1MB/s 1 MB/s 2.0 High Speed 480 Mb/s 56 MB/s 24 MB/s • USB-HOST verwaltet den USB-Bus und organisiert den Datenaustausch, CPU wird fast nicht belastet • Der Datenaustausch muß zwingend über USB-Host laufen • Polling: USB-CPU erfragt in regelmäßigen Abständen den Gerätestatus • Bus-Topologie: abgestufte Sternstruktur, pro Ebene sind 7 Geräte möglich: d.h. an einem Hub können max. 7 neue Geräte andocken • die Verbindung der Geräte wird über Hub (=Verteiler) oder Kabeldurchschleifung hergestellt USB (2) • Insgesamt können 127 Geräte angeschlossen werden; das 128. Gerät ist die USB-CPU, die einen Interrupt belegt • Hot Plugging: an- und abstöpseln während des laufenden Betriebes (keine manuelle Konfiguration nötig) • integrierte Stromversorgung (nur für schwachlastige Geräte z.B. Maus, Tastatur; Drucker, Scanner ... benötigen Netzanschluß) • USB 2.0 ist vollständig abwärtskompatibel • bulk-Transfer: verlustfreie Übertragung mit Ack-Signal (Handshake), • isochron-Transfer: konstanter Datenstrom ohne Fehlerkorrektur (USB-Modem, USB-Lautsprecher) USB (3) • Beide Modi sind vollständig paketorientiert, das erlaubt den quasi parallelen Betrieb. • Jedes Gerät darf maximal 50% der Bandbreite nutzen. Bei "Full Speed" also nur 6Mb/s. Hiervon muß noch einmal der Overhead für das USB-Protokoll abgezogen werden, so daß 4,8Mb/s als reine Nutzbandbreite übrig bleibt! • USB-Lautsprecher funktionieren auch ohne Soundkarte; Die Umwandlung der digitalen Daten (auch Midi-Daten) geschieht in den Lautsprechern. die Rolle der Soundkarte wird durch das Betriebssystem ersetzt, der Prozessor wird nur geringfügig mehr belastet als mit Soundkarte USB Baum LK BITS 3