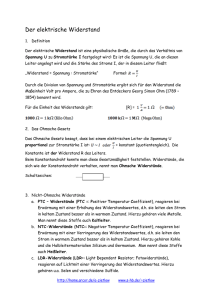

Temperaturstabile Dünnfilmwiderstände aus Ti/TiN

Werbung