11. Vorlesung Dr.-Ing. Wolfgang Heenes

Werbung

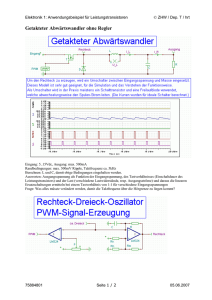

Grundlagen der Rechnertechnologie Sommersemester 2010 – 11. Vorlesung Dr.-Ing. Wolfgang Heenes 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 1 Inhalt 1. Einführung in die Signalverarbeitung 2. Abtasttheorem 3. Analog-Digital-Wandler 4. Verfahren der AD-Wandlung 5. Abtast-Halte-Schaltung 6. AD-Wandler mit dem Parallelverfahren 7. Digital-Analog-Wandler 8. R-2R Wandler 9. Zusammenfassung und Ausblick 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 2 Einführung in die Signalverarbeitung I Um physikalische Größen, wie beispielsweise I I I I I I I Druck, Drehmoment, Längenänderung, Temperatur, meßtechnisch erfassen zu können, werden Sensoren eingesetzt. Sensoren wandeln physikalische Meßgrößen in elektrische Größen um und stellen das elektrische Signal häufig in Form einer Spannung oder eines elektrischen Widerstands zur Verfügung. Die Auswertung und Verarbeitung lassen sich aus Gründen der Genauigkeit, der Störsicherheit, Langzeitstabilität und auch der geringeren Kosten wegen am besten mit digitalen Meß- und Datenverarbeitungssystemen realisieren. Die Nachteile der digitalen Signalverarbeitung sind die Abtastung und Quantisierung der Signalwerte und die Verzögerung. Echzeitfähige Systeme setzen in der Regel spezielle Hardware/Software voraus. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 3 Einführung in die Signalverarbeitung I Die analogen Sensorsignale werden zunächst in eine digitale Darstellung umgesetzt. Die Abbildung zeigt das Blockschaltbild eines solchen Systems. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 4 Einführung in die Signalverarbeitung I Das vom Sensor zur Verfügung gestellte Signal wird mit einem Analog-Digital-Wandler1 (ADU) in eine Folge von Nullen und Einsen gewandelt. I Die Signalverarbeitung erfolgt z. B. mit FPGAs oder speziellen Signalprozessoren. I Die Operationen der Signalverarbeitung sind z. B. Filteroperationen, bei der ein Signal in der Bandbreite begrenzt wird. Der Digital-Analog-Wandler (DAU) generiert Signale für Aktoren. 1 Im deutschen Sprachgebrauch auch Umsetzer genannt. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 5 Einführung in die Signalverarbeitung I Der Analog-Digital-Wandler hat zwei Aufgaben. Die Abbildung kann als eine Spannung über der Zeit interpretiert werden. Um ein digitales Signal zu erhalten, wird die Spannung zu bestimmten Zeitpunkten aufgenommen. Dieser Vorgang wird Abtastung genannt. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 6 Einführung in die Signalverarbeitung I Der zweite Vorgang bei einer Wandlung ist die Quantisierung. Darunter versteht man, wie die kontinuierliche Amplitude in einen digitalen Code abgebildet wird. Die Abbildung veranschaulicht diesen Vorgang. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 7 Abtasttheorem I Bei der Vorstellung des Ozilloskops wurde der Begriff Aliasing eingeführt. Aliasing tritt auf, wenn z. B. ein Digitaloszilloskop die Signale nicht schnell genug abtastet, um eine präzise Signalaufzeichnung zu ermöglichen. Die Abbildung zeigt ein Signal, das eine niedrigere Frequenz als das eigentliche Eingangssignal aufweist. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 8 Abtasttheorem I Um ein Signal präzise darzustellen und Aliasing zu vermeiden, muß das Signal mit einer Frequenz abgetastet werden, die mehr als doppelt so hoch wie die höchste Frequenz des Signals ist. Die höchste Frequenz des Signals wird durch eine Tiefpaßfilterung vor der Abtastung bestimmt. fmax ≤ 1 · fAbt 2 I Diese Beziehung wird als Abtasttheorem bezeichnet und wurde von Nyquist/Shannon/Raabe begründet. I Ein Signal mit Frequenzkomponenten von 5 MHz muß zum Beispiel mit mindestens 10 Millionen Abtastungen pro Sekunde abgetastet werden. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 9 Beispiele I Das menschliche Ohr hört Frequenzen bis 20 kHZ → Samplerate2 einer CD ist 44.1 kHz. I Telefonleitungen übertragen Frequenzen bis zu 4 kHz → Telefongesellschaft tastet mit 8 kHz ab. 2 Abtastfrequenz 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 10 Zeitbereich/Frequenzbereich I In der Abbildung ist ein sinusförmiges Signal mit einer Frequenz von 10 kHz dargestellt. Die Darstellung bezeichnet man in der Signaltheorie als Zeitbereich. Das Signal weist nur eine Frequenzkomponente auf. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 11 Zeitbereich/Frequenzbereich I Mittels der sogenannten Fast-Fourier-Transformation (FFT) kann das Signal in seine Frequenzkomponenten zerlegt werden. Die Abbildung zeigt den Frequenzbereich des sinusförmigen Signals. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 12 Zeitbereich/Frequenzbereich I Die x-Achse ist in 2.50 kHz pro Teilung skaliert. Ausgehend vom linken Rand, der einer Frequenz von Null entspricht, stellen die vier Teilungen eine Frequenz von 10 kHz dar (4 · 2.50 kHz = 10 kHz). Die y-Achse ist in 10 dB pro Teilung skaliert. I Die digitale Signalverarbeitung führt viele Algorithmen im Frequenzbereich aus. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 13 Analog-Digital-Wandler I Die Funktionseinheit, die analoge Spannungen oder Ströme in digitale Daten umsetzt, wird Analog-Digital-Wandler genannt. Die Abbildung zeigt die Funktionsblöcke eines AD-Wandlers. Nach der Tiefpaßfilterung sorgt die Sample & Hold-Schaltung dafür, daß während der Umsetzzeit eine konstante Eingangsspannung am AD-Wandler anliegt. Die Hersteller von Analog-Digital-Wandlern benutzen in den Datenblättern eine Reihe von Begriffen und Kenngrößen, von denen nachfolgend einige Wichtige näher erläutert werden. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 14 Auflösung I Ein Analog-Digital-Wandler, der den gesamten Bereich seines analogen Eingangsspannungsbereichs in eine Anzahl 2n verschiedener analoger Spannungswerte unterteilt, besitzt eine Auflösung von n Bit. I Ein Wandler mit einer Auflösung von n Bit vergleicht die analoge Spannung an seinem Eingang mit einer Anzahl 2n von internen Teilreferenzspannungen und bildet an Hand dieses Vergleichs das n-Bit Datenwort an seinem Ausgang. I Die kleinstmögliche Änderung des analogen Spannungswertes am Eingang des Wandlers, die eine Änderung des Datenwortes am Ausgang zur Folge hat, entspricht bei einer Auflösung von n Bit dem 1/2n -ten Teil des Eingangsspannungsbereiches. I Dieser Teil wird Quant Q genannt und entspricht dem Wert der Teilreferenzspannung UQ = UREF /2n . 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 15 Auflösung I Ein 10-Bit-AD-Wandler mit unipolarem Eingangsspannungsbereich weist die minimale Teilreferenzspannung UQ = UREF /210 auf, die 0.09765% seines Eingangsspannungsbereichs entspricht. I Bei bipolaren AD-Wandlern setzt sich der Eingangspannungsbereich aus dem positiven und dem negativen Anteil zusammen. I Bei einem 10-Bit AD-Wandler mit bipolaren Eingangsspannungsbereich, bei dem das Datenbit mit der höchsten Wertigkeit (MSB)3 das Vorzeichen darstellt und die Polarität der Eingangsspannung bestimmt, beträgt demnach die minimale Teilreferenzspannung UQ = 2 · UREF /210 , die 0.1953% des gesamten Eingangsspannungsbereichs entspricht. I Übliche Werte für die Auflösung von AD-Wandlern sind heutzutage 6, 8, 10, 12, 14, 16, 18, 20 und 24 Bit. 3 Most Significant Bit 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 16 Aufgabe 12.1 I Ein 8 Bit AD-Wandler hat eine Referenzspannung UREF = 5 Volt. Wie lautet der binäre Ausgangscode für eine Eingangsspannung von 1.2 Volt? Wie groß ist die Spannung, die vom LSB repräsentiert wird? Berechnen Sie die Werte für unipolaren und bipolaren Eingangsspannungsbereich. Mit 8 Bit lassen sich 256 Zustände kodieren. Für den unipolaren Wandler ergibt sich für die Spannung, die vom LSB repräsentiert wird: 5V ≈ 19.5 mV 256 Für den bipolaren Wandler ergibt sich: 2 · 5V ≈ 39.1 mV 256 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 17 Aufgabe 12.1 I Bei einer Eingangsspannung von 1.2 Volt ergibt sich für den unipolaren Wandler: 1.2 V ≈ 61 19.5 mV Für den binären Ausgangscode ergibt sich damit (die binäre Darstellung von 61) 00111101. Bei einer Eingangsspannung von 1.2 Volt ergibt sich für den bipolaren Wandler: 1.2 V ≈ 30 39.1 mV Für den binären Ausgangscode ergibt sich damit (die binäre Darstellung von 30) 00011110. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 18 Codierung I Die Darstellung des binären Ausgangswertes erfolgt bei unipolaren AD-Wandlern, die nur einen positiven Wertebereich der analogen Eingangsspannung umsetzen, üblicherweise im Dualcode. I Bipolare AD-Wandler, die sowohl einen positiven als auch einen negativen Wertebereich der Eingangsspannung erfassen, geben das Ergebnis am Ausgang entweder in Zweier-Komplement-Darstellung oder im Dualcode mit Offset, also einer Verschiebung an. I AD-Wandler mit sehr kurzen Umsetzzeiten stellen das Ergebnis der Umsetzung auch im einschrittigen Gray-Code zur Verfügung. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 19 Eingangsspannungsbereich I Der Eingangsspannungsbereich (engl.: span bzw. full scale input range, abgekürzt FSR) eines AD-Wandlers ist die Differenz zwischen dem zulässigen Maximal- und dem zulässigen Minimalwert der analogen Eingangsspannung. I Bei einem unipolaren Wandler entspricht der Bereich dabei dem zulässigen Maximalwert der Eingangsspannung. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 20 Umsetzzeit I Die Umsetzzeit (engl.: conversion time) ist die Zeitdauer, die vom Beginn der Umsetzung bis zur Bereitstellung des Datenwortes am Ausgang des Umsetzers vergeht. I Häufig wird in den Datenblättern auch die Umsetzrate (engl.: conversion rate) angegeben, die dem Kehrwert der Summe der Umsetzzeit und zusätzlicher Verzögerungszeiten entspricht. I Bei sehr schnellen Wandlern benutzt man Verfahren, bei denen bereits mit einer neuen Umsetzung begonnen werden kann, bevor die vorhergehende Umsetzung beendet ist. I In der Reihe der Bearbeitung (engl.: pipelining) finden gleichzeitig mehr als eine Umsetzung statt. I Obwohl dadurch die Umsetzzeit jeder einzelnen Umsetzung nicht verkürzt wird, läßt sich jedoch die Umsetzrate vergrößern. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 21 Quantisierung - Quantisierungsfehler I Teilt man den kontinuierlichen Wertebereich der Amplitude des analogen Eingangssignals UE in eine endliche Anzahl m gleicher Teilbereiche (Quanten), so entspricht dem Wert der Amplitude des Signals zu einem Abtastzeitpunkt eine bestimmte Anzahl von Quanten. I Je größer die Auflösung eines AD-Wandlers, um so größer die Anzahl der Quanten und um so genauer läßt sich die Amplitude des Signals quantisieren. I Da die Amplitude des analogen Signals unendlich viele Werte annehmen kann, ergibt sich auf Grund der endlichen Anzahl m der Quanten, in die der Wert des analogen Signals eingeteilt wird, ein unvermeidbarer Fehler, der Quantisierungsfehler FQ (engl.: quantization error) genannt wird. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 22 Quantisierung - Quantisierungsfehler I Ändert der Wandler den Wert des Datenwortes an seinem Ausgang jeweils bei den analogen Eingangswerten, die einer ganzen Anzahl von Quanten entsprechen, so kann der maximale Quantisierungsfehler den Wert eines Quants aufweisen. I Je größer die Auflösung eines AD-Wandlers ist, um so kleiner ist der Wert des Quantes Q und der Wert des maximalen Quantisierungsfehlers FQmax . I Ein AD-Wandler mit einer Auflösung von n Bit und der internen Referenzspannung UREF besitzt einen maximalen Quantisierungsfehler FQmax : FQmax = ± 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 23 Q UREF = ± n+1 2 2 Verfahren der AD-Wandlung I Bei den Verfahren der AD-Wandlung unterscheidet man das Parallel-, das Kaskaden-, das Serien- und das Zählverfahren. I Ein n-Bit-AD-Wandler, der das Parallelverfahren verwendet, bestimmt den digitalen Ausgangswert durch den Vergleich der analogen Eingangsspannung mit einer Anzahl 2n − 1 von Teilreferenzspannungen. I Wandler mit dem Parallelverfahren erfordern einen großen schaltungstechnischen Aufwand und weisen eine äußerst kurze Umsetzzeit auf. I Um den schaltungstechnischen Aufwand des Parallelverfahrens zu reduzieren, läßt sich das Kaskadenverfahren verwenden. Dieses besteht dem Prinzip nach aus zwei nacheinanderfolgenden Parallelverfahren, mit denen die Datenbits der höherwertigen und der niederwertigen Dualstellen des Datenwortes getrennt ermittelt werden. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 24 Verfahren der AD-Wandlung I Ein n-Bit AD-Wandler, der das Serienverfahren verwendet, benötigt lediglich eine Anzahl n von Teilreferenzspannungen. I Dieser Umsetzer ermittelt jede Stelle des Datenwortes seriell nacheinander, so daß für eine Umsetzung insgesamt n Umsetzschritte erforderlich sind. I Der geringere schaltungstechnische Aufwand des Serienverfahrens muß mit einer größeren Umsetzzeit im Vergleich zum Parallelverfahren erkauft werden. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 25 Verfahren der AD-Wandlung I Wandler, die das Zählverfahren verwenden, zählen dem Prinzip nach, wie oft der Quant Q aufaddiert werden muß, damit er den Wert der analogen Eingangsspannung aufweist. I AD-Wandler mit einer Auflösung von n Bit, die dieses Zählverfahren verwenden, benötigen demnach bei dem maximalen Wert der Eingangsspannung eine maximale Anzahl von 2n an Additionen des Quantes Q und weisen daher eine sehr große Umsetzzeit auf. I Andere Wandler verwenden Zählverfahren, bei dem die Zeitdauer gemessen wird, die die Integration einer internen Referenzspannung UREF erfordert, bis der Integrationswert der Referenzspannung dem Wert der Eingangsspannung entspricht. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 26 Aufgabe 12.2 I Ein Digitalmultimeter soll zehn Dezimalstellen anzeigen. Welche Auflösung (Anzahl der Bits) muß der AD-Wandler besitzen? I Die Dezimalstellen zeigen z. B. den Wert 9999999999. Die Anzahl der Bits ergeben sich aus log2 (9999999999). ln 9999999999 ≈ 34 ln 2 Der Wandler benötigt also 34 Bit. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 27 Aufgabe 12.3 I Ein unkomprimiertes Stereo-Audiosignal in CD-Qualität sei mit 44.1 kHz abgetastet und mit 16 Bit quantisiert. Wieviele Bytes fallen pro Sekunde an? I Es ergibt sich eine Datenrate von: 2· 16 Bit Byte 44100 · = 176400 s 8 Bit /Byte s 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 28 Abtast-Halte-Schaltung I Die Zeit, die ein AD-Wandler für die Umsetzung des analogen Spannungswertes an seinem Eingang in das zugehörige Datenwort am Ausgang benötigt, wird Umsetzzeit genannt. I Um eine fehlerfreie Umsetzung zu gewährleisten, darf die umzusetzende analoge Spannung am Eingang des Wandlers während der Zeitdauer der Umsetzung ihren Wert nicht verändern. I In Fällen, in denen sich das analoge Signal während der Umsetzzeit ändern kann, muß dem Umsetzer eine Abtast-Halte-Schaltung, wie in der folgenden Abbildung zu sehen, vorgeschaltet werden. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 29 Aufgabe 12.4/12.5 I Welche Funktion führen die in Abbildung ... dargestellten Operationsverstärkerschaltungen aus? Wie nennt man diese Schaltungen? I Die Abtast-Halte-Schaltung, die wie die Bezeichnung besagt die Zustände Abtasten und Halten des analogen Eingangssignals ermöglichen, besteht aus dem Schalter S, dem Kondensator C und zwei gegengekoppelten Operationsverstärkern, die als Impedanzwandler und Spannungsfolger dienen. I Der Schalter S wird durch das Signal CC (conversion complete) gesteuert. I Das Signal SC (start conversion) bewirkt den Start einer Analog-Digital-Umsetzung 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 30 AD-Wandler mit dem Parallelverfahren I Grundlage eines Wandlers nach dem Parallelverfahren ist der Komparator. Die Abbildung zeigt einen AD-Wandler nach dem Parallelverfahren. Der Operationsverstärker wird im „single supply mode” benutzt. Die Spannung UV bzw. V + soll +5 Volt betragen. GND bzw. V − wird an die Masse angeschlossen. UV 1kΩ Ein + - 1kΩ + - 1kΩ + - 1kΩ + - Aus 1 Aus 2 Aus 3 Aus 4 1kΩ GND 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 31 AD-Wandler mit dem Parallelverfahren Aufgabe 12.6 I Der Operationsverstärker vergleicht die Eingangsspannung UEin mit diesen Referenzspannungen. Ist die Spannung am jeweiligen Eingang größer als die Referenzspannung, so liegt am Ausgang des Operationsverstärker in etwa die Versorgungsspannung. Ist die Spannung kleiner als die Referenzspannung, so erscheint 0 Volt. I Welche Referenzspannungen liegen an den vier Eingängen der Operationsverstärker? Es handelt sich um einen Spannungsteiler aus fünf gleichen Widerständen. Für die Spannungen an den Operationsverstärker-Eingängen (von unten nach oben) ergibt sich: U4 1 Volt U3 2 Volt U2 3 Volt U1 4 Volt 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 32 Aufgabe 12.7 I Welchen Verlauf sollte die Eingangsspannung haben, damit die Funktionsfähigkeit der Schaltung nachgewiesen wird? I Für solche Spannungsverläufe benutzen Sie in PSPICE die Spannungsquelle VPULSE. Alternativ können Sie auch die DC Sweep Analyse verwenden. Die Periodendauer PER soll 1 s betragen. Die Referenzspannung beträgt 5 Volt. Die Versorgungsspannung der Operationsverstärker ist oben angegeben. Die Ausgänge der Operationsverstärker werden über einen 1 M Ω Widerstand nach Masse geführt I Benutzen Sie als Operationsverstärker den OPAMP aus der Bibliothek analog.slb. Bei Benutzung des LM324 wird das Limit der möglichen Knoten erreicht. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 33 Digital-Analog-Wandler I Aktoren zeigen physikalisch die umgekehrte Funktionsweise der Sensoren, da sie anhand einer vorgegebenen elektrischen Größe eine physikalische Analogiegröße, wie Druck, Drehmoment, Längenänderung, Temperatur, an ihren Ausgängen zur Verfügung stellen. I Um Aktoren von digitalen Meß- und Datenverarbeitungssystemen ansteuern zu können, müssen daher zunächst die digitalen Ausgabedaten in elektrische Analogiegrößen wie Spannung oder Widerstand umgesetzt werden. I Anhand dieser elektrischen Größen erzeugen die Aktoren die entsprechenden physikalischen Größen. I Die Funktionseinheit, die digitale Daten in analoge Spannungen umsetzt, wird Digital-Analog-Wandler genannt. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 34 Auflösung I Ein Digital-Analog-Wandler, der eine Anzahl von m = 2n verschiedenen analogen Spannungswerten an seinem Ausgang zur Verfügung stellt, besitzt eine Auflösung von n Bit bzw. von dem 1/2n -ten Teil seines Ausgangsspannungsbereiches. I Dieser Bruchteil entspricht dabei dem Quant und stellt die kleinstmögliche Änderung der analogen Ausgangsspannung des Umsetzers dar, die durch einen Wechsel des Datenbits mit der geringsten Wertigkeit (LSB) hervorgerufen wird. I Bei Umsetzern mit bipolarem Eingangsspannungsbereich setzt sich dieser aus dem positiven und negativen Anteil zusammen. I Ein unipolarer 10-Bit DA-Wandler weist demnach die minimale Teilreferenzspannung UQ = UREF /210 auf, die 0.0976% des Ausgangsspannungsbereichs entspricht. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 35 Auflösung I Bei einem bipolaren 10-Bit DA-Wandler, bei dem das Bit der höchsten Wertigkeit (MSB) das Vorzeichen darstellt und die Polarität der Ausgangsspannung bestimmt, beträgt dagegen die minimale Teilreferenzspannung UQ = 2 · UREF /210 , die 0.1953% des Ausgangsspannungsbereichs entspricht. I DA-Wandler weisen heutzutage übliche Werte für die Auflösung von 6, 8, 10, 12, 14, 16, 18, 20 und 24 Bit auf. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 36 Aufgabe 12.8 I I Ein unipolarer 12-Bit DA-Wandler hat eine Referenzspannung UREF = 5.12 V . Wie groß ist die Ausgangsspannung für den binären Eingangscode (101010101010)? Wie groß ist die Spannung ULSB ? Welche Größe stellt das MSB dar? Aus der Referenzspannung UREF = 5.12V und dem Wissen, daß es sich um einen unipolaren 12-Bit DA-Wandler handelt, ergibt sich: 5.12 V = 1.25 mV 212 Der binäre Eingangscode entspricht der Dezimalzahl 2730. Die Ausgangsspannung ist also: ULSB = 2730 · 1.25 mV = 3.4125 V Das MSB besitzt den folgenden Wert: 2048 · 1.25 mV = 2.56 V 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 37 Ausgangsspannungsbereich I Der Ausgangsspannungsbereich (engl.: full scale output range, abgekürzt FSR) eines DA-Wandlers ist der Differenzbetrag zwischen dem maximalen und minimalen Wert der analogen Ausgangsspannung. I Bei einem unipolaren Wandler entspricht dieser Bereich dem Wert der maximalen Ausgangsspannung UFSR = UAmax = (1 − 2−n ) · UREF , da der Wert der minimalen Ausgangsspannung 0 V beträgt. I Bei einem bipolaren Wandler entspricht der Bereich der Differenz des Maximal- und des Minimalwertes der Ausgangsspannung UFSR = UAmax − UAmin = (1 − 2−n+1 ) · UREF − (−UREF ) = (2 − 2−n+1 ) · UREF . 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 38 Ausgangsspannungsbereich I Die kleine Differenz des Maximalwertes vom positiven Wert der Referenzspannung UREF wird meistens vernachlässigt, so daß unipolare Wandler einen Ausgangsspannungsbereich von UFSR = UREF und bipolare Wandler einen Spannungsbereich UFSR = 2 · UREF aufweisen, der häufig auch mit UFSR = ±UREF angegeben wird. Übliche Werte des Ausgangsspannungsbereichs unipolarer Umsetzer sind 5 V bzw. 10 V, während die meisten bipolaren Umsetzer einen Ausgangsspannungsbereich von ± 5 V bzw. ± 10 V aufweisen. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 39 Codierung I Als Codierung für das Datenwort am Eingang von DA-Wandlern werden der Dualcode, die Zweier-Komplement- und die Offset-Darstellung verwendet. I Bei Umsetzern mit unipolarem Ausgangsspannungsbereich werden fast ausschließlich Datenwörter, die im Dualcode codiert sind, benutzt. Die analoge Ausgangsspannung UA des Wandlers nimmt daher beim Datenwort, welches in allen Stellen das Binärzeichen 0 aufweist, den Wert 0 V an. I Der maximale Wert der analogen Ausgangsspannung UAmax = (1 − 2−n ) · UREF steht am Ausgang des Umsetzers für den Fall zur Verfügung, daß das Datenwort am Eingang in allen Stellen das Binärzeichen 1 aufweist. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 40 Codierung I Bei Umsetzern mit bipolarem Ausgangsspannungsbereich wird entweder die Zweier-Komplement- oder die Offset-Darstellung verwendet. I Bei der Offset-Darstellung nimmt die analoge Ausgangsspannung den negativsten Wert UAmin = −UREF an, wenn am Eingang das Datenwort, welches in allen Stellen das Binärzeichen 0 aufweist, anliegt. I Bei dieser Darstellung stellt sich der maximale Wert der Ausgangsspannung UAmax = (1 − 2−n+1 ) · UREF dagegen für den Fall ein, daß das Datenwort am Eingang in allen Stellen das Binärzeichen 1 aufweist. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 41 Einschwingzeit I Die Einschwingzeit (engl.: setting time) eines DA-Wandlers ist die Zeit, die der Wandler vom Beginn einer Änderung der Kombination des Datenwortes an seinem Eingang bis zum Einschwingen des zugehörigen Wertes der Ausgangsspannung innerhalb einer gegebenen Toleranz benötigt. I Der Toleranzbereich, den die Ausgangsspannung innerhalb der Einschwingzeit erreichen muß, wird in Bit (beispielsweise ± 1 LSB) oder in Prozent des Aussteuerbereichs angegeben. Die Hersteller geben in ihren Datenblättern häufig die Einschwingzeit beim Wechsel aller Bits des Datenwortes an. I Das entspricht einer Änderung der Spannung am Ausgang vom minimalen auf den maximalen Wert oder umgekehrt I In den Datenblättern findet man die Angabe der Anstiegszeit (engl.: slew rate), die die Begrenzung des zeitlichen Anstiegs der Ausgangsspannung, die meist in V/µs angegeben wird, kennzeichnet. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 42 Genauigkeit I Unter der Genauigkeit (engl.: accuracy) eines DA-Wandlers versteht man die Differenz zwischen dem analogen Spannungswert an seinem Ausgang, der sich an Hand des am Eingang anliegenden Datenwortes eigentlich einstellen müßte, und dem Wert der analogen Ausgangsspannung UA , der sich an seinem Ausgang tatsächlich einstellt. I Ursachen für eine Differenz zwischen diesen beiden Werten sind Offset-, Verstärkungs- und Linearitätsfehler. Die Genauigkeit der Umsetzer wird meistens in Bit (beispielsweise ± 1 LSB) angegeben. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 43 Glitches I In DA-Wandlern werden Transistoren als elektronische Schalter verwendet. Da diese elektronischen Schalter unterschiedliche Ein- und Ausschaltzeiten aufweisen, treten bei einigen der verwendeten Verfahren der Umsetzung kurzzeitige Einbrüche oder auch Spitzen der analogen Ausgangsspannung, allgemein Glitch genannt, beim Wechsel des Datenwortes auf, wie die Abbildung zeigt. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 44 R-2R Wandler I Eine gebräuchliche Schaltung zur DA-Wandlung ist in der folgenden Abbildung zu sehen. Der Name R-2R Wandler ist aus den benutzten Widerstandswerten abgeleitet. Typische Werte für R liegen im Bereich von 1 k Ω bis 10 k Ω. 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 45 Zusammenfassung und Ausblick I AD/DA Wandler Nächste Vorlesung behandelt I Logikfamilien 29. Juni 2010 | Technische Universität Darmstadt | Dr.-Ing. Wolfgang Heenes | 46