digitalelektronik

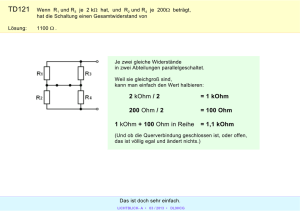

Werbung