10.Übung - EMV

Werbung

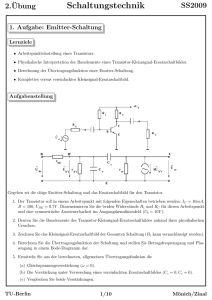

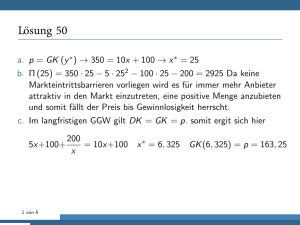

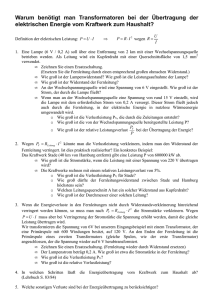

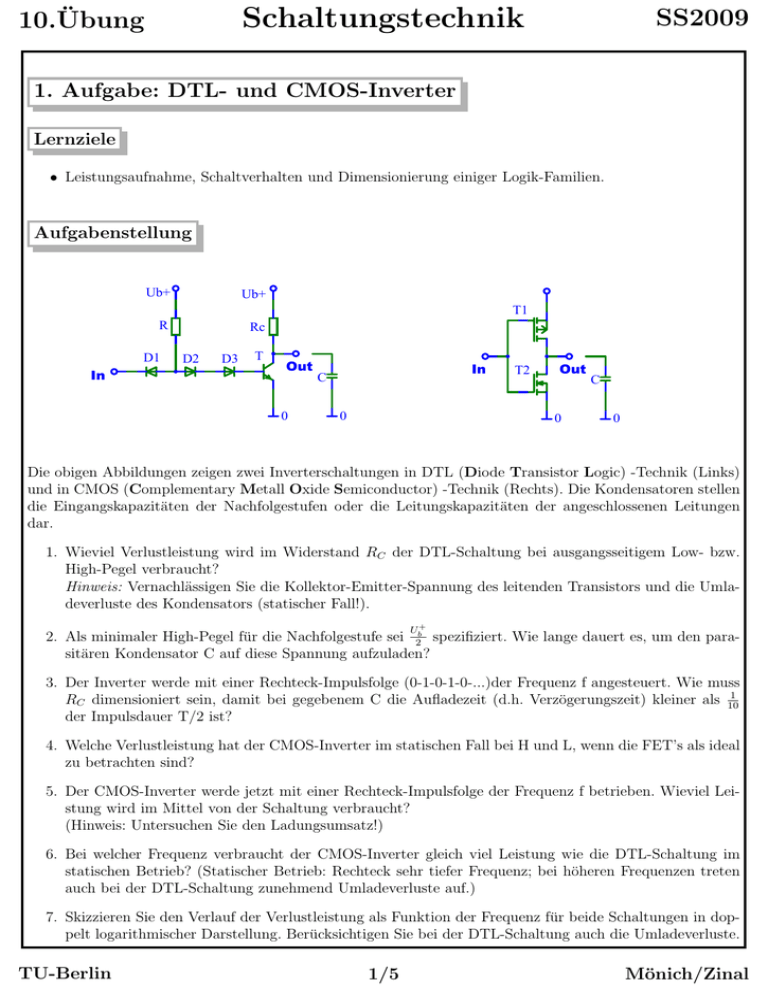

Schaltungstechnik 10.Übung SS2009 1. Aufgabe: DTL- und CMOS-Inverter Lernziele • Leistungsaufnahme, Schaltverhalten und Dimensionierung einiger Logik-Familien. Aufgabenstellung Ub+ Ub+ T1 R D1 In Rc D2 D3 T Out 0 In C 0 T2 Out 0 C 0 Die obigen Abbildungen zeigen zwei Inverterschaltungen in DTL (Diode Transistor Logic) -Technik (Links) und in CMOS (Complementary Metall Oxide Semiconductor) -Technik (Rechts). Die Kondensatoren stellen die Eingangskapazitäten der Nachfolgestufen oder die Leitungskapazitäten der angeschlossenen Leitungen dar. 1. Wieviel Verlustleistung wird im Widerstand RC der DTL-Schaltung bei ausgangsseitigem Low- bzw. High-Pegel verbraucht? Hinweis: Vernachlässigen Sie die Kollektor-Emitter-Spannung des leitenden Transistors und die Umladeverluste des Kondensators (statischer Fall!). U+ 2. Als minimaler High-Pegel für die Nachfolgestufe sei 2b spezifiziert. Wie lange dauert es, um den parasitären Kondensator C auf diese Spannung aufzuladen? 3. Der Inverter werde mit einer Rechteck-Impulsfolge (0-1-0-1-0-...)der Frequenz f angesteuert. Wie muss 1 RC dimensioniert sein, damit bei gegebenem C die Aufladezeit (d.h. Verzögerungszeit) kleiner als 10 der Impulsdauer T/2 ist? 4. Welche Verlustleistung hat der CMOS-Inverter im statischen Fall bei H und L, wenn die FET’s als ideal zu betrachten sind? 5. Der CMOS-Inverter werde jetzt mit einer Rechteck-Impulsfolge der Frequenz f betrieben. Wieviel Leistung wird im Mittel von der Schaltung verbraucht? (Hinweis: Untersuchen Sie den Ladungsumsatz!) 6. Bei welcher Frequenz verbraucht der CMOS-Inverter gleich viel Leistung wie die DTL-Schaltung im statischen Betrieb? (Statischer Betrieb: Rechteck sehr tiefer Frequenz; bei höheren Frequenzen treten auch bei der DTL-Schaltung zunehmend Umladeverluste auf.) 7. Skizzieren Sie den Verlauf der Verlustleistung als Funktion der Frequenz für beide Schaltungen in doppelt logarithmischer Darstellung. Berücksichtigen Sie bei der DTL-Schaltung auch die Umladeverluste. TU-Berlin 1/5 Mönich/Zinal Schaltungstechnik 10.Übung SS2009 Lösung 1. Verlustleistung der DTL-Schaltung: PV |H = 0 PV |L = (1) Ub 2 RC (2) 2. Berechnung der Schaltzeit: Ub = uc(t) + uRC(t) = uc(t) + RC ic(t) = uc(t) + RC C =⇒ d uc(t) dt Ub d uc(t) 1 + uc(t) = dt RC C RC C (3) (4) Lösung der homogenen Differentialgleichung: d uc(t) 1 + uc(t) = 0 dt RC C −R uc,h(t) = kh e t CC d uc(t) Ub mit: ic(t = 0) = C = d t t=0 RC mit: kh = −Ub (5) (6) Lösung der inhomogenen Differentialgleichung: uc,p = kp Durch einsetzen in (4): kp = Ub (7) Damit ergibt sich die Gesamtlösung: −R uc(t) = uc,h(t) + uc,p = Ub (1 − e t(uc ) = −RC C ln(1 − t( t CC ) (8) uc ) Ub (9) Ub ) = RC C ln(2) 2 (10) 3. Dimensionierung von RC : Die Impulsdauer beträgt die Hälfte der Periode tp = t( Ub 1 )< tp 2 10 TU-Berlin =⇒ RC C ln(2) < 1 20 f =⇒ 2/5 1 . 2f RC < 1 20 ln(2) f C (11) Mönich/Zinal Schaltungstechnik 10.Übung SS2009 4. Statische Verlustleistung der CMOS-Schaltung: Da die FETs als ideal betrachtet werden, kann der Kanal-Widerstand des leitenden Transistor als (0) und der des sperrenden Transistor als (∞) betrachtet werden. PV |H = 0 (12) PV |L = 0 (13) 5. Dynamische Verlustleistung der CMOS-Schaltung (Umschaltverluste): Während einer Periode wird der Quelle eine Ladungsmenge Q = Ub C entnommen. Dies entspricht einem mittleren Strom I¯ = UTb C = Ub C f . U2 C Damit ist die mittlere Leistung durch P̄ = Ub I¯ = bT und die Energie pro Periode durch WT = Ub2 C gegeben. U2 C Bemerkung: Die während des H-Zustandes im Kondensator gespeicherte Energie beträgt b2 , also nur die Hälfte der von der Quelle entnommenen Energie. Der Rest geht beim Aufladen verloren. 6. Vergleich: Bei tiefen Frequenzen überwiegen bei der DTL-Schaltung die in 1 berechneten statischen Verluste. Die Umschaltverluste kommen erst bei höheren Frequenzen zum tragen, sie lassen sich wie bei der CMOSSchaltung berechnen. 2 Die mittlere Leistung beträgt P̄DT L,stat. = 2URb C . P̄DT L,stat. = P̄CM OS,dyn. =⇒ Ub 2 = Ub2 C f 2 RC =⇒ f= 1 2 RC C (14) 7. Vergleich: Die gesamte Verlustleistung der DTL-Schaltung ist gegeben durch: P̄DT L = P̄DT L,stat. + P̄DT L,dyn. Ub 2 = + Ub2 C f 2 RC (15) 1 10 0 10 -1 10 -2 Verlustleistung 10 -3 10 -4 10 -5 10 -6 10 -7 10 DTL CMOS -8 10 -9 10 0 10 1 10 2 10 3 10 4 5 10 10 6 10 7 10 8 10 9 10 10 10 Frequenz TU-Berlin 3/5 Mönich/Zinal Schaltungstechnik 10.Übung SS2009 2. Aufgabe: ECL-Inverter Aufgabenstellung 0 Rc 0 0 Rc T3 T1 T2 Ur In 0 RE Ub- 0 R Ub- Out 0 Die obige Abbildung zeigt einen Inverter in ECL (Emitter Coupled Logik) -Technik. Vernachlässigen Sie alle Bsisströme. Als High-Zustand am Ausgang wollen wir annehmen, dass Transistor T2 leitet und T1 sperrt. In dieser Aufgabe soll untersucht werden, unter welchen Bedingungen eine Sättigung der beteiligten Transistoren vermieden wird. Dies ist erforderlich, um kürzeste Schaltzeiten zu erreichen, wie dies z.B. bei SchreibLese-Speichern gefordert ist. Um dies zu erreichen, darf in keinem Betriebszustand das Kollektorpotenzial eines Transistors unter sein Basispotenzial absinken, d.h. die Basis-Kollektor-Diode muss immer in Sperrrichtung betrieben werden, um Sättigung zu vermeiden. 1. Wie groß ist die Ausgangsspannung im High-Zustand? 2. Welche Bedingung muss das Potenzial am Kollektor von T1 zur Vermeidung der Sättigung erfüllen, wenn an der Basis High-Potenzial anliegt (Resultat von 1)? 3. Wie groß ist dann die Low-Spannung am Ausgang und wie muss die Referenzspannung Ur gewählt werden, so dass die Umschaltschwelle in der Mitte zwischen H- und L-Pegel liegt? 4. Ist es zulässig, das Massepotenzial zum Erzeugen eines eingangsseitigen HI-Pegels zu benutzen? TU-Berlin 4/5 Mönich/Zinal 10.Übung Schaltungstechnik SS2009 Lösung 1. Ua,H = −0.7V 2. Das H-Potential beträgt nach dem obigen Ergebnis −0.7V . Dies bedeutet daß das Kollektorpotential von T1, bei eingangsseitigem H-Zustand, größer als −0.7V sein muß um Sättigung zu vermeiden. 3. Mit einer T1-Kollektorspannung von −0.7V (obiger Grenzwert der Sättigung) ergibt sich: UaL = UC,T 1 + UBE,T 3 = −0.7V − 0.7V = −1.4V Ur = UaH + UaL = −1.05V 2 (16) (17) 4. Nein, weil dann T1 zwangsläufig in die Sättigung gerät. TU-Berlin 5/5 Mönich/Zinal