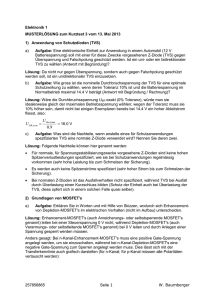

Elektronik II, Foliensatz 4 Felde ekttransistoren

Werbung

Elektronik II, Foliensatz 4

Feldeekttransistoren

G. Kemnitz

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

1/87

Inalt des Foliensatzes

1.1

1.2

1.3

1.4

1.5

1.6

2.1

2.2

2.3

2.4

Feldeekttransistoren

MOSFET

Sperrschicht-Fet

Leistungsschalter

Kleinsignalmodell

Schaltverhalten

Aufgaben

Grundschaltungen

Source-Schaltung

Drainschaltung

Gateschaltung

Aufgaben

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

2/87

1. Feldeekttransistoren

G. Kemnitz

Feldeekttransistoren

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

3/87

1. Feldeekttransistoren

MOSFET

Über der Halbleiteroberäche bendet sich, isoliert durch

eine dünne Oxidschicht, die Steuerelektrode, das Gate

Die Gate-Kanal-Spannung steuert die Zustandsdichte der

beweglichen Ladungsträger (Elektronen oder Löcher) und

damit den Leitwert im Kanal.

Gate

Leiter, Polysilizium

Isolator, Siliziumoxid

Kanal mit einer steuerbaren

Dichte beweglicher Elektronen

gesperrter pn-Übergang

Halbleiter mit beweglichen

Löchern

G. Kemnitz

·

UGK

p

n ∼ UGK

n ∼ GK

Uth

UGK

Bulk

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

4/87

1. Feldeekttransistoren

Aufbau und Anschlüsse

n-Mosfet

S

UDS

p-Mosfet

D

UGS G

n

B

D

UGS G

ID

n

n-Kanal

UDS

S

p

p

B

ID

p

p-Kanal

n

Source: Quelle der beweglichen Ladungsträger

Drain: Abuss der beweglichen Ladungsträger

SB- und DB-Übergang immer in Sperrrichtung

Vorzeichen UDS so, dass Ladungen zum Drain ieÿen

NMOS: UDS ≥ 0, ID ≥ 0

PMOS: UDS ≤ 0, ID ≤ 0

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

5/87

1. Feldeekttransistoren

Sperrschicht-FET (Jfet und MesFet)

normaler Jfet

S

G

B

n+

n−

p+

p+

D

B

n+

p+

Mesfet

S

G Al

n+

n−

D

n+

p

p

gesteuerte Sperrschichtbreite

Steuerung der Kanalbreite über die Breite einer Sperrschicht:

JFet (junction-fet) eines gesperrten pn-Übergangs

MesFet (metal-semiconductor-fet) eines Schottky-Übergangs

immer selbstleitend

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

6/87

1. Feldeekttransistoren

Kennlinien und Symbole

n-Mosfet

selbstsperrend

G

D

ID

B

Uth UGS

S

n-Mosfet

selbstleitend

G

D

ID

B

S

p-Mosfet

selbstsperrend

G. Kemnitz

D

ID

G

ID

ID

UDS

ID

ID

Uth

UGS

ID

Uth UGS

UDS

ID

UDS

S

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

7/87

1. Feldeekttransistoren

p-Mosfet

selbstleitend

D

ID

ID

Uth UGS

G

UDS

S

n-Jfet

D

ID

ID

G

S

p-Jfet

G. Kemnitz

D

ID

Uth

ID

UGS

UGS Uth

ID

UDS

ID

UDS

G

S

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

8/87

1. Feldeekttransistoren

G. Kemnitz

1. MOSFET

MOSFET

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

9/87

1. Feldeekttransistoren

1. MOSFET

Feldeekt (NMOS-Transistor)

Gate-Isolator-Halbleiter ⇒ Plattenkondensator

negative Gateladung führt zu einer Ansammlung positiver

beweglicher Ladung unter dem Gate

Source-Kanal- und Drain-Kanal-Übergang gesperrt

G

S

UG < 0

G. Kemnitz

n+

p-Substrat

0

ρ

D

n+

Akkumulationsschicht

x

ρ Ladungsdichte

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

10/87

1. Feldeekttransistoren

1. MOSFET

Positive Gatespannung kleiner der Einschaltspannung Uth

wegdriften der Löcher;

Anreicherung ortsfester Ladungen im Kanal

Kanal bleibt gesperrt

0

G

S

0 < UG < Uth

G. Kemnitz

n+

p-Substrat

ρ

D

n+

Verarmungsschicht

x

Aufladung mit ortsfesten Ionen

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

11/87

1. Feldeekttransistoren

1. MOSFET

Positive Gatespannung gröÿer der Einschaltspannung

Source-Kanal-Übergang wechselt in den Durchlassbereich

der Kanal füllt sich mit beweglichen Elektronen

bewegliche Ladung im Kanal ∼ UG − Uth

0

G

UG ≥ Uth

G. Kemnitz

S

D

n+

n+

Verarmungsschicht

Inversionsschicht

p-Substrat

·

Institut für Informatik, Technische Universität Clausthal

ρ

x

9. Juli 2013

12/87

1. Feldeekttransistoren

1. MOSFET

Einschaltspannung

Die Einschaltspannung eines MOS-Transistors :

Uth = Uth.0 + γ ·

p

p

Uinv − UBS − Uinv

(1)

(UBS Bulk-Source-Spannung).

Parameter für einen Beispiel-CMOS-Prozess:

Param.

Uth.0

γ

Uinv

Spice

Bezeichnung

VT0

Null-Schwellspannung

GAMMA Substratsteuerfaktor

PHI

Inversionsspannung

n-Kanal

p-Kanal

0,73

0,73

0,76

-0,75

0,56∗

0,73

V

√

V

V

Beim PMOS-Transistoren sind γ und UBS negiert in Gl. 1

einzusetzen. Im Spice-Modell berücksichtigt.

∗

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

13/87

1. Feldeekttransistoren

1. MOSFET

Stromgleichungen aktiver Bereich

UDS

RD

UGS

B

S

p+

n+

UV

G

Gate

ID

D

Kanal

p-Substrat

n+

U (y)

beweglichen Ladung im Kanal:

Ql (y) = Cl · (UGK (y) − Uth ) = Cl · (UGS − Uth − U (y))

y

Ql (y)

Cl

U (y)

G. Kemnitz

·

Weg vom Source zum Drain

beweglichen Ladung für Wegstück dy

Gate-Kanal-Kapazität für Wegstück dy

Gate-Kanal-Spannung an der Stelle y

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

14/87

1. Feldeekttransistoren

1. MOSFET

Der Drainstrom ist ein Driftstrom:

ID = Ql (y) · µ · Ey

µ Beweglichkeit

Ey Feldstärke in Kanalrichtung

µ · Ey Geschwindigkeit der Ladungsträger

Die Feldstärke in Stromussrichtung ist gleich der

Spannungsänderung entlang des Kanals:

Ey =

d U (y)

dy

Alle Gl. zusammen ergeben eine DGL:

G. Kemnitz

ID = Cl · µ · (UGS − Uth − U (y)) ·

·

Institut für Informatik, Technische Universität Clausthal

d U (y)

dy

9. Juli 2013

15/87

1. Feldeekttransistoren

G. Kemnitz

1. MOSFET

UDS

RD

UGS

B

S

p+

n+

UV

G

Gate

ID

D

Kanal

n+

U (y)

p-Substrat

U (y)

UDS

0

0

l

ID = Cl · µ · (UGS − Uth − U (y)) ·

·

Institut für Informatik, Technische Universität Clausthal

y

d U (y)

dy

9. Juli 2013

16/87

1. Feldeekttransistoren

1. MOSFET

ID = Cl · µ · (UGS − Uth − U (y)) ·

d U (y)

dy

Die Integration beider Gleichungsseiten über die gesamte

Kanallänge:

ID ·

Z

0

L

dy = Cl · µ ·

ID · L = Cl · µ ·

ID

Z

0

Z

L

(UGS − Uth − U (y)) ·

d U (y)

· dy

dy

ϕ(L)

ϕ(0)

(UGS − Uth − U (y)) · dU (y)

mit ϕ (0) = 0 und ϕ (l) = UDS

2 UDS

Cl · µ

=

· (UGS − Uth ) · UDS −

L

2

mit relativem Steilheitskoezient:

G. Kemnitz

K0 =

·

Cl · µ

W

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

17/87

1. Feldeekttransistoren

1. MOSFET

2 UDS

W

ID = K ·

· (UGS − Uth ) · UDS −

L

2

0

Parameter für einen Beispiel-CMOS-Prozess:

Param.

Spice

Bezeichnung

n-Kanal

p-Kanal

K0

Kp

relativer Steilheitskoezient

69

23,6∗

µA/V2

Bei PMOS-Transistoren ist der Steilheitskoezient in der Gleichung

darüber negativ, damit ein negativer Strom herauskommt. Das

Vorzeichen steckt aber oenbar schon im Modell des

PMOS-Transistors:

∗

G. Kemnitz

ID.PMOS = −K 0 ·

·

W

· (...)

L

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

18/87

1. Feldeekttransistoren

1. MOSFET

Einschnürbereich

UGS > Uth

B

S

p+

n+

UV

G

Gate

ID

D

n+

p-Substrat

U (y)

RD

UGD < Uth

Abschnürpunkt

U (y)

UDS

Spannung über dem

Abschnürpunkt

Spannung über dem eingeschalteten Kanalstück

UGS − Uth

0

0

l

y

Das Kanalende ist ausgeschaltet

Die restliche Spannung UDS − UGS + Uth fällt über dem

eingeschnürten Kanalstück ab.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

19/87

1. Feldeekttransistoren

1. MOSFET

Die Länge des Einschnürbereichs regelt sich so ein, dass die

ankommenden Ladungsträger zum Drain abieÿen können.

Der ankommende Strom ID hängt nicht von der Spannung

über dem Einschnürpunkt ab.

konstanter ID , gleiche Gröÿe wie beim Übergang in den

Einschnürbereich UDS = UGS − Uth :

G. Kemnitz

ID

ID

·

U2

W

· (UGS − Uth ) · UDS − DS

L

2

für UDS = UGS − Uth

W

2

= K0 ·

· (UGS − Uth )

2·L

= K0 ·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

20/87

1. Feldeekttransistoren

1. MOSFET

Kanallängenmodulation und Early-Eekt

Steigende Drain-Source-Spannung: Ausdehnung Einschnürrpunkt.

Kanalverkürzung. Beobachtbares Verhalten:

−UA = − λ1

UDS

UA

Param.

Spice

Bezeichnung

λ

LAMBDA

Kanallängen-Modulationsparameter

·

EB

UDS

Korrekturterm nach Strahlensatz: 1 +

G. Kemnitz

AB

ID

AB aktiver Bereich

EB Einschnürrbereich

Institut für Informatik, Technische Universität Clausthal

= (1 + λ · UDS )

n-Kanal

p-Kanal

0,033 V−1

0,055 V−1

9. Juli 2013

21/87

1. Feldeekttransistoren

1. MOSFET

Stromgleichung mit Early-Eekt

0

0 W

ID = K · ·(1 + λ · UDS )· (UGS − Uth ) · UDS −

L

(UGS −Uth )2

Sperrbereich

2

UDS

2

Einschnürrbereich

2

Bahnwiderstände:

aktiver Bereich

B

S

G

D

RG

n+ RS

RD n+

p+

p

RB

Param.

Spice

Bezeichnung

BC547B

BUV47

RG

RS

RD

RG

RS

RD

Gate-Bahnwiderstand

Source-Bahnwiderstand

Drain-Bahnwiderstand

0,02

25

5,6

0,022

0,022

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

Ω

Ω

Ω

9. Juli 2013

22/87

1. Feldeekttransistoren

1. MOSFET

Ein Fertigungsprozess gibt statt der Einzelwiderstände

Schichtwiderstände vor.

Schichtwiderstand Rsh : Widerstand einer quadratischen

leitfähigen Schicht. Produkt aus Dicke und spezischem

Widerstand.

Widerstand eines Schichtelements Länge L Breite W :

R = Rsh ·

L

W

Param.

Spice

Bezeichnung

NMOS

PMOS

Rsh

RSH

Drain-Source-Diusionsschichtwiderstand

25

45

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

Ω

9. Juli 2013

23/87

1. Feldeekttransistoren

1. MOSFET

Sperrströme der Bulkdioden

RD

ID.D

G

RG

RB

ID ID.S

RS

UGS

D

B

S

Parameter für die Sperrströme der Bulk-Dioden:

Param.

Spice

Bezeichnung

BSD215

IRF140

IS

IS

125

1,3

n

N

Sättigungssperrstrom

Bulk-Dioden

Emmisionskoezient der

Bulk-Dioden

-

-

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

pA

9. Juli 2013

24/87

1. Feldeekttransistoren

1. MOSFET

MOSFET in LT-Spice

.model nmos1 nmos(Kp=69e-6 VT0=0.73 lambda=0.003 ...)1

.model pmos1 pmos(Kp=23e-6 VT0=0.75 lambda=0.055 ...)

Param.

Spice

Bezeichnung

n-Kanal

p-Kanal

K0

Kp

69

-23,6

Uth.0

γ

Uinv

λ

VT0

gamma

PHI

lambda

relativer Steilheitskoezient

Null-Schwellspannung

Substratsteuerfaktor

Inversionsspannung

Kanallängen-Modulationsparameter

µA/V2

0,73

-0,75

V

√

0,73

0,56

V

0,76

0,73

V

0,033 V−1 0,055 V−1

Erzeugt ein neues Modell, bei dem die explizit zugewiesen

Parameterwerte die Standardwerte der Basismodelle, hier nmos und

pmos überschreiben.

1

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

25/87

1. Feldeekttransistoren

1. MOSFET

Festlegung der Geometrie

Geometrieunabhängiges Modell denieren:

.modell nmos1 nmos(Kp=25µA/V² VT0=0.73 lambda=0.003 ...)

MOS-Transistor nmos4 auswählen

Modell und Geometrieparameter eintragen.

S

1,5 µm

1µm

1,5 µm

G

D

G. Kemnitz

3 µm

n-Wanne

p+ -Gebiet

n+ -Gebiet

Polysilizium-Streifen

Metallleiterbahn

Durchkontaktierung

·

Eingabemaske

für die Kennlinienberechnung erforderlich

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

26/87

1. Feldeekttransistoren

1. MOSFET

Schaltung und Simmulationsergebnis

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

27/87

1. Feldeekttransistoren

Kapazitäten

B

p+

1. MOSFET

NMOS-Transistor

S G D

n+

n+

PMOS-Transistor

G S

B

D

p+

p

p+

n+

n

Kapazität vom Gate zum Kanal bzw. Bulk:

CG = ε0 · εSiO2 ·

L·W

dox

(ε0 = 8, 85 pF

m Dielektrizitätskonstante Vakuum;

εSiO2 = 3,9 relative Dielektrizitätskonstante von SiO2 ; L Länge; W Breite des Gates.)

Kapazität der Source- und Draingebiete zum Substrat:

0

CBS/BD = A · CS0 + u · CR

(A Fläche; u Umfang des Drain- bzw. Source-Gebiets).

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

28/87

1. Feldeekttransistoren

1. MOSFET

Param.

Spice

Bezeichnung

NMOS

PMOS

dox

CS0

TOX

CJ

25

360

25

340

µF/m2

0

CR

CJSW

Oxiddicke

SperrschichtKapazitätsbelag

RandKapazitätsbelag

250

200

pF/m

S

1,5 µm

1µm

1,5 µm

G

D

W in µm

CG

CBS

G. Kemnitz

·

nm

W · µm2

Gatefläche:

Fläche Source- / Draingebiet: A = 1,5 · W µm2

Umfang Source- / Draingebiet: u = 2 · W + 3 µm

pF

1 µm · W

· 3,9 ·

= W · 1,55 fF

m

25 nm

µF

pF

= CBD = W · 1,5 µm2 · 360 2 + (2 · W + 3 µm) · 250

m

m

= W · 1,04 fF + 0,75 fF

=

8, 85

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

29/87

1. Feldeekttransistoren

1. MOSFET

Kapazitäten im Simulationsmodell

CSB

CGD

AC-Simulation der kapazitiven Ströme und Umrechnung in

Kapazitäten:

|I (f )|

C... =

...

1V · 2π · f

Die Gate-Kapazität wird oensichtlich zur Hälfte zu CGS

und zur Hälfte zu CGD zugeordnet.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

30/87

1. Feldeekttransistoren

1. MOSFET

Modell mit Kapazitäten

RD

ID.D

Kapazitäten

CGS =

CBS =

CBD =

G

CGD

CBD

CGS

ID CBS

RB

RG

ε ·ε 2 ·L·W

CGD = 0 SiO

2·dox

AS · CS0 + uS · CR0

AD · CS0 + uD · CR0

D

B

ID.S

RS

S

Stromgleichung mit Early-Eekt

0

W

ID = K 0 · ·(1 + λ · UDS )· (UGS − Uth ) · UDS −

L

(UGS −Uth )2

Sperrbereich

2

UDS

2

2

aktiver Bereich

Einschnürrbereich

Bahnwiderstände und die Sperrströme der pn-Übergänge

sollen im Weiteren bei integrierten Transistoren

vernachlässigt werden.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

31/87

1. Feldeekttransistoren

1. MOSFET

Durchbruchspannung

Durchschlag des Gateoxids bei Mosfets ab etwa 10 bis 20 V;

zerstörend; Wegen hohen Eingangswiderstand genügt bereits

die Ladung beim Berühren.

Bei Einzel-MOSFETs ohne Schutzschaltung Anschlüsse

verbunden; Verbindung erst nach Einbau entfernen.

Drain-Source-Durchbruch: 10 bis 40 V wegen hoher

Feldstärke gleich Spannung durch Kanallänge:

ID

UDS

Spice-Parameter2 ?

2

Wird so vom Simulationsmodell nicht unterstützt.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

32/87

1. Feldeekttransistoren

1. MOSFET

Parasitärer Tyristor und Latch-up

n-Kanal-Mosfet

B

S

p+

n+

p-Kanal-Mosfet

B

S

Rn

n+

Rp

p+

n

Die Schichtfolge npnp bildet eine Thyristor

Wenn einer der parasitären Bipolartransistoren einen kurzen

Basisstrom bekommt, liefert er dem anderen Basisstrom.

Zünden. Selbsthaltend.

Ausschaltbar nur durch Stromunterbrechung.

Wirkt wie ein Kurzschluss zwischen Versorgungsspannung

und Masse. Thermische Zerstörung des Bauteils.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

33/87

1. Feldeekttransistoren

1. MOSFET

Potentielle Quellen für Zündströme: Eingangs- und

Ausgangspotentiale < 0 oder > UV über

Eingangsschutzdioden oder die Bulkdioden am Ausgang.

Bei Gefahr von unzulässigen Eingangsspannungen

Reihenwiderstand ≈100 Ω zur Begrenzung des Stroms durch

die Schutzdioden.

G. Kemnitz

UV

ue

UV

0

t

ue

Quellen für

Zündströme

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

34/87

1. Feldeekttransistoren

G. Kemnitz

2. Sperrschicht-Fet

Sperrschicht-Fet

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

35/87

1. Feldeekttransistoren

2. Sperrschicht-Fet

Sperrschicht-Fets

ID.D

D

G

G

D

ID.S ID

S

S

Weglassen des isolierten Gates

Umbenennen Bulk in Gate

Ersatz Kn0 · W

L durch 2 · β

0

ID = 2·β ·(1 + λ · UDS )· (UGS − UTh ) · UDS −

(UGS −UTh )2

Sperrbereich

2

UDS

2

2

aktiver Bereich

Einschnürrbereich

Einfaches, aber nicht sehr genaues Modell.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

36/87

1. Feldeekttransistoren

2. Sperrschicht-Fet

Simulation Kennline NJFET

Param.

β

λ

Uth

G. Kemnitz

·

Spice

beta

lambda

VT0

Bezeichnung

Steilheitskoezient

Kanallängenmodulation

Null-Schwellspannung

Institut für Informatik, Technische Universität Clausthal

2N3819

1,3m

2,25m

-3

A/V2

1/V

V

9. Juli 2013

37/87

1. Feldeekttransistoren

G. Kemnitz

3. Leistungsschalter

Leistungsschalter

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

38/87

1. Feldeekttransistoren

3. Leistungsschalter

MOSFET für hohe Spannungen

B

S

G

D

ID

D

UDrift

Poly-Si

p+

n−

n+

n+

G

p

gesteuerter Kanal

D’

RG

Driftstrecke

G’

UD′ S′

S’

RS

hohe Steilheit, kurze Kanallänge, geringe

S

Drain-Source-Spannung

Erhöhung der zulässigen UGSmax durch zusätzliches niedrig

dotiertes Driftgebiet zwischen Kanal und Drain, über dem

ein Groÿteil der Drain-Source-Spannung abfällt

Durchbruchspannung ∼ Länge des Driftgebiets

Im aktiven Bereich wirkt die Driftstrecke wie ein

selbstleitender Fet

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

39/87

1. Feldeekttransistoren

3. Leistungsschalter

MOSFET für hohe Ströme und Spannungen

G

n+

p

S, B

n+ + n+

p

p

p

G

n+ + n+

p

p

p

n−

n+

D

gesteuerter Kanal

Driftstrecke

Bei Einzel-Mosfets paltzsparende vertikale Anordnung

Der Kanal ist unter dem Gate.

Die Driftstrecke geht nach unten.

Als 3D-Struktur Kanalbreiten bis zu 1 m

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

40/87

1. Feldeekttransistoren

3. Leistungsschalter

IGBT

G

E

p+

SiO2

n+

Ersatzschaltung

C

Symbol

C

n−

G

+

n

p+

G

parasitärer

Transistor

C

E

E

Kombination aus MOSFET und Bipolatransistor

Bipolartransistor mit breiter Basis für hohe

Spannungsfestigkeit

Basisstrom wird vom MOS-Transistor geliefert. Wenn

eingeschaltet, von unten Injektion von Ladungsträgern in die

n− Driftregion der Basis.

·

G. Kemnitz

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

41/87

1. Feldeekttransistoren

3. Leistungsschalter

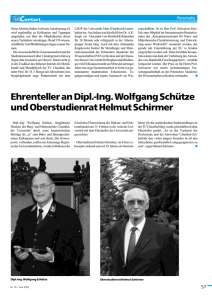

IGBT-Modul für 1,2 kA und 3,3 kV

Latch-Up-Gefahr:

Bipolar- + zusätzlicher

parasitären Transistor =

Flächentyristor. Beim

Zünden entsteht ein nicht

mehr über das Gate ausschaltbarer Strom.

Anwendung als Schalter:

Sperrspannung bis 6500 kV

Durchlassstrom bis 3500 A

Schaltfrequenz bis 200 kHz

Schaltbare Verbraucherleistung bis 100 MW

Verlustleistung im IGBT:

Durchlassspannung typ. 2,3 V

Ausschaltverzögerung durch die für Bipolartransistoren typ.

Stromschleife.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

42/87

1. Feldeekttransistoren

G. Kemnitz

4. Kleinsignalmodell

Kleinsignalmodell

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

43/87

1. Feldeekttransistoren

4. Kleinsignalmodell

Lineare Ersatzschaltung

Ersatzschaltung

Normalbetrieb

G

lineare

Ersatzschaltung

D

ID

f (UGS , UBS )

UGS

UBS

G

uGS

S · UGS

S

B

D

iD

rDS

SB · UBS

B

uBS

S

Abschnürbereich:

G. Kemnitz

2

ID

=

K0 ·

Uth

·

W

(UGS − Uth )

· (1 + λ · UDS ) ·

L

2

p

p

= Uth.0 − γ ·

Uinv − UBS − Uinv

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

44/87

1. Feldeekttransistoren

4. Kleinsignalmodell

2

Uth

Steilheit

S

W

(UGS − Uth )

· (1 + λ · UDS ) ·

L

2

p

p

Uinv − UBS − Uinv

= Uth.0 − γ ·

= Kn0 ·

ID

=

≈

d ID W

· (1 + λ · UDS.A ) · (UGS.A − Uth.A )

= K0 ·

{z

} |

{z

}

d UGS A

L |

K · (UGS.A − Uth.A ) ≈

Ausgangswiderstand:

1

rDS

p

≈1

√

2·ID.A·...

2 · K · ID.A mit K = K 0 ·

W

(2)

L

2

d ID (UGS.A − Uth.A )

0 W

=

=

K

·

·

λ

·

≈ λ · ID.A

n

d UDS A

L

2

Substratsteilheit:

G. Kemnitz

SB

·

=

d ID d Uth S·γ

√

=S·

=

d UBS A

d UBS A

2 · Uinv − UBS.A

Institut für Informatik, Technische Universität Clausthal

(3)

9. Juli 2013

45/87

1. Feldeekttransistoren

4. Kleinsignalmodell

Für NMOS-Transistor W = 3, Kn0 = 69

−S =

µA

V2 ,

...

d I(VD)

d VG

UG.A

S

=

rDS

=

G. Kemnitz

·

S · 0, 73

µA

√

· (UGS.A − 0, 73 V) ; SB =

= S · 0, 28

V2

2 · 0, 67 + 1

2

293 kΩ · V2

=

2

2

µA

207 V2 · 0, 033 V−1 · (UGS.A − 0, 73 V)

(UGS.A − 0, 73 V)

207

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

46/87

1. Feldeekttransistoren

4. Kleinsignalmodell

Einbeziehung der Kapazitäten

Ersatzschaltung mit C’s

D

iD

CGD

CBD

CGS

CBS

G

S

UGD

B

lineare Ersatzschaltung mit Kapazitäten

D

iD

CBD

CGD

G

CGS

S · UGS

UGD

rDS

S

SB · UBS

B

CBS

UBS

Die Kapazitäten bewirken, dass für hohe Frequenzen die

Verstärkung mit der Frequenz abnimmt.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

47/87

1. Feldeekttransistoren

4. Kleinsignalmodell

Rg

Rg

Ug

G

ID

D

S

Ug

Gate

CGS

CGD

Drain

ID

U GS

Source

S · U GS

Für Source, Drain und Substrat wechselspannungsmäÿig auf

Masse und einem Generatorwiderstand Rg :

entfallen alle Kapazitäten, die Massepunkte verbinden

die von der Substratspannung gesteuerte Quelle.

ID =

Ug · S

Ug · S

=

1 + jωRg · (CGS + CGD )

1 + j ·ff0

Übergangsfrequenz der Steilheit:

G. Kemnitz

f0 =

·

1

2π · Rg · (CGS + CGD )

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

48/87

1. Feldeekttransistoren

G. Kemnitz

5. Schaltverhalten

Schaltverhalten

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

49/87

1. Feldeekttransistoren

5. Schaltverhalten

Beispiel Inverterkette

CGS4

CGD3/4

CGS2

ID4

CGD1/2

UV

CGS6

ID2

CGD5/6

ID6

x

CGS3

ID3

CBD3/4

CGS1

ID1

z1

x

M1

M2

UV

CBD1/2

CGS5

ID5

y

CBD5/6

z2

M3

M4

y

M5

UV

M6

UV

Transistorsteilheiten und Kapazitäten berechnen sich aus

den Abmessungen der Source-, Gate- und Draingebiete.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

50/87

1. Feldeekttransistoren

5. Schaltverhalten

Simulation des Schaltverhaltens

M1, M3, M5

M2, M4, M6

L

µm

W

µm

1

1

1,5

3

AD

µm2

2,25

4,5

AS

µm2

PD

µm

PS

µm

2,25

4,5

6

9

6

9

M1 – M4 Einzeltansistoren, M5 und M6 Parallelschaltung 2 Transistoren

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

51/87

1. Feldeekttransistoren

5. Schaltverhalten

td1

td2

Peaks zu Beginn der Schaltvorgänge werden oensichtlich

von CGD verursacht.

td2 ≈ 2 · td1 , weil V(Z2) die doppelte Last wie V(Z1) hat.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

52/87

1. Feldeekttransistoren

5. Schaltverhalten

Folgerung 1

Logische Funktionen werden durch Reihen- und Parallelschaltung

von Transistoren realisiert. Die Verzögerung ist umgekehrt

proportional zur Steilheit und proportional zur kapazitiven Last.

Die Kapazitiven Lasten nehmen proportional zu Breite*Breite

und die Steilheit mit Breite durch Länge zu. Einfach zu

modellieren und zu entwerfen.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

53/87

1. Feldeekttransistoren

G. Kemnitz

6. Aufgaben

Aufgaben

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

54/87

1. Feldeekttransistoren

6. Aufgaben

Kontrollfragen

1

2

3

4

5

6

7

Warum sind Sperrschicht-FETs selbstleitend?

Hat die Schwellspannung Uth eines selbstsperrenden

PMOS-Transistors einen positiven oder einen negativen

Wert.

Was beschreibt der Kanallängen-Modulationsparameter λ?

Was ist ein Latch-up in einer CMOS-Schaltung? Woraus

setzt sich der Flächentyristor zusammen und was passiert,

wenn der Flächentyristor zündet?

Was ist ein IGBT, was sind seine wesentlichen Eigenschaften

und was ist seine Hauptanwendung?

Was bewirkt die Driftstrecke zwischen Kanal und Drain von

MOSFETs für hohe Spannungen?

Wie ist die Steilheit im Kleinsignalmodell eines

MOS-Transistors deniert und was ist die Substratsteilheit?

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

55/87

1. Feldeekttransistoren

1

2

Berechnen Sie für einen NMOS-Transistor mit

Kp = 70 µA/V2 der Nullschwellspannung UTh = 0, 8 V ... die

Steilheit und den Ausgangswiderstand im Arbeitspunkt

UGS.A = 3 V.

Berechnen Sie für einen NMOSFET mit den geometrischen

Abnessungen in der nachfolgenden Abbildung und den

geometrieunabhängigen Paramtern in der nachfolgenden

Tabelle die Kapazitäten ...:

Param.

Spice

Bezeichnung

NMOS

PMOS

Oxiddicke

25

25

nm

Sperrschicht360

340

µF/m2

Kapazitätsbelag

0

CR

CJSW

Rand250

200

pF/m

Kapazitätsbelag

Schätzen Sie für die nachfolgende JFET-Source-Schaltung

die

Übertragungsfunktion. ... zu Schwer? den

·

dox

CS0

3

6. Aufgaben

G. Kemnitz

TOX

CJ

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

56/87

2. Grundschaltungen

G. Kemnitz

Grundschaltungen

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

57/87

2. Grundschaltungen

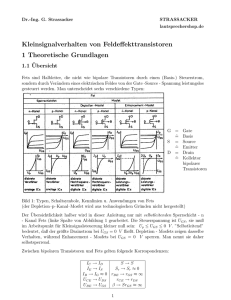

Grundschaltungen

Source-Schaltungen mit unterschiedlicher Gegenkopplung

ohne

Strom

Spannung

UV

UV

UV

RD

RD

RD

Ue

Ua

Ue

Drain-Schaltung

UV

Ua

RS

R1

R2

Ua

Ue

Gate-Schaltung

UV

RD

Ue

G. Kemnitz

RS U a Ue

·

Ua

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

58/87

2. Grundschaltungen

Genau wie bei Bipolartransistoren lassen sich für jede dieser

Grundschaltungen:

die Parameter der Transferfunktion

die Übertragungsfunktion im Frequenzbereich

die Übergangsfrequenz

das Rauschen, der Klirrfaktor, ...

bestimmen. Die resultierenden Besonderheiten sind ähnlich zu

denen der vergleichbaren Transistorschaltung:

Source-Schaltung: normale Verstärker,

Strom-/Spannungsgegenkopplung zur Linearisierung

Drainschaltung: Impedanzkonverter

Gate-Schaltung: Verstärker für hohe Frequenzen

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

59/87

2. Grundschaltungen

G. Kemnitz

1. Source-Schaltung

Source-Schaltung

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

60/87

2. Grundschaltungen

1. Source-Schaltung

Übertragungskennlinie

UV

RD

Ue

Ua

Verstärker nutzen den Abschnürbereich3 :

ID

Ua

K

2

· (Ue − Uth )

2

K · RD

2

≈ UV −

· (Ue − Uth )

2

≈

Gilt für Ue ≥ Uth und Ua ≥ Ue − Uth .

Ue < Uth : Sperrbereich

Ua < Ue − Uth : aktiver Bereich.

3

Nachfolgender Überschlag ist ohne Kanallängenmodulation.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

61/87

2. Grundschaltungen

1. Source-Schaltung

Simulation

Transistor:

W = 10 µm

L = 1 µm

RD

Ua

Sperr- Einschnürbereich

bereich

Arbeitspunkt

aktiver Bereich

Ue

Die Kennlinie ist nichtlinear. Für Kleinsignalverstärker wird der

Arbeitspunkt in der Mitte des Einschnürrbereichs gewählt.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

62/87

2. Grundschaltungen

1. Source-Schaltung

RD

U a Grundwelle

Klirrfaktor

Oberwellen

f

Eine näherungsweise quadratische Kennlinie:

Ua ≈ UV −

K · RD

2

· (Ue − Uth )

2

Hauptsächlich Oberwellen der doppelten Frequenz?

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

63/87

2. Grundschaltungen

Harmonic

Number

1

2

3

4

5

6

7

8

9

10

Total

1. Source-Schaltung

Frequency Fourier Normalized

[Hz]

Component Component

1.000e+03 4.615e-01 1.000e+00

2.000e+03 1.279e-02 2.772e-02

3.000e+03 9.857e-03 2.136e-02

4.000e+03 8.984e-04 1.947e-03

5.000e+03 4.568e-04 9.899e-04

6.000e+03 6.210e-04 1.346e-03

7.000e+03 2.262e-04 4.901e-04

8.000e+03 5.054e-04 1.095e-03

9.000e+03 8.046e-04 1.743e-03

1.000e+04 4.306e-04 9.330e-04

Harmonic Distortion: 3.516327%

Phase

[degree]

-179.72°

91.64°

17.28°

-111.24°

104.30°

160.23°

147.54°

168.58°

93.23°

165.59°

Höherer Frequenzen vernachlässigte Kanallängenmodulation?

G. Kemnitz

2

·

ID

=

K · (1 + λ · UDS ) ·

Ua

=

UV −

(UGS − Uth )

2

K · RD

2

· (Ue − Uth ) · (1 + λ · UDS )

2

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

64/87

2. Grundschaltungen

1. Source-Schaltung

Oberwellen und Bandbegrenzung

Nutzsignal aus benachbarten Frequenzen, im Beispiel 95kHz,

100kHz und 105kHz:

Was bewirken hier Nichtlinearitäten, z.B. Quadrierung?

G. Kemnitz

t

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

65/87

2. Grundschaltungen

1. Source-Schaltung

U e (Amplitudenspektrum Eingangssignals)

Signal

f

U a (Amplitudenspektrum des verzerrten Ausangssignals)

Differenzen

Summen

f

ua enthält alle Summen- und Dierenzfrequenzen von 95kHz,

100kHz und 105kHz: 5kHz, 10kHz, 190kHz, 195kHz, ...

Unterdrückbar durch Bandbegrenzung.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

66/87

2. Grundschaltungen

1. Source-Schaltung

Kleinsignalersatzschaltung

Rg

ug

S0 · uGS

uGS

rDS

RD ua

RL

Eingangswiderstand: ∞

Ausgangswiderstand:

ra = rDS k RD

Verstärkung:

mit der

S=

4

Steilheit4

d ID

=

d UGS

d

vU = −S · ra

K

2

2

· (UGS − Uth )

d UGS

= K · (UGS.A − Uth )

Term für Kanallängenmodulation vernachlässigt.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

67/87

2. Grundschaltungen

Transistor:

W = 10 µm

L = 1 µm

RD

1. Source-Schaltung

Ua

Sperr- Einschnürbereich

bereich

Arbeitspunkt

aktiver Bereich

Ue

Simulation mit .tf (V(a) Ve:

Eingangswiderstand: ∞ (berechnet wird 1020 Ω)

Ausgangswiderstand: 9,6 kΩ (rDS fast vernachlässigbar groÿ)

Verstärkung: vU = −4,7. Probe vU = K · (UGS.A − Uth ) · ra ;

10 · 69 µA

· (1,5 V − 0,67 V) · 9,6 kΩ = −5,1. Abweichung

V2

vermutlich, weil Überschlag ohne Kanallängenmodulation.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

68/87

2. Grundschaltungen

1. Source-Schaltung

Übergangsfrequenz

Ergänzen von CGS und CGD in der

Kleinsignalersatzschaltung.

Rg

RL′

CGD

U GS

Ug

CGS

S0 · U GS

rDS

RD

RL

Ua

Umrechnung von CGD in Kapazitäten zum Emitter:

Rg

Ug

U GS

(* exakt 1 − vU ;

G. Kemnitz

·

∗∗

|vU · CGD )|

+CGS

exakt

∗

1−vU

vU ;

S0 · U GS

∗∗

CGD

RL′

Ua

d.h. Näherung für −vU 1)

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

69/87

2. Grundschaltungen

1. Source-Schaltung

Rg

Ug

U GS

|vU · CGD )|

+CGS

∗

S0 · U GS

∗∗

CGD

RL′

Ua

Gate-Source-Spannungsteiler:

U GS

1

=

Ug

1 + jω ·

f

mit fSS1 =

fSS1

1

2π · RG · (CGS + (1 − vU ) · CGD )

Ausgangsspannung in Abhängigkeit vom Drainstrom:

Ua

RL0

=−

ID

1 + jω ·

f

fSS2

mit fSS2 =

1

2π ·

RL0

· CGD

Übertragungsfunktion:

G. Kemnitz

Ua

= −

Ug

1 + jω ·

·

S0 · RL0

f

fSS1 · 1 + jω ·

Institut für Informatik, Technische Universität Clausthal

f

fSS2

9. Juli 2013

70/87

2. Grundschaltungen

1. Source-Schaltung

Sourceschaltung mit Stromgegenkopplung

Ua

RD

Arbeitspunkte

mit RS

RS

ohne RS

1,8 V

Ue

Minderung der Verstärkung

Minderung des Aussteuerungsbereiches

Erhöhung der Linearität; Verringerung Klirrfaktor, hier bei

100 mV Eingangsamplitude von 2,8% auf 2,3% (nicht viel)

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

71/87

2. Grundschaltungen

1. Source-Schaltung

Transferfunktion mit und ohne Stromgegenkopplung

Rg

ug

uGS

mit RS

ohne RS

Ue.A

1,8 V

1,6 V

re

∞

∞

S0 · uGS

rDS

RD ua

10 k

RL

RS

1k

9,7 kΩ

9,6 kΩ

vU

-3,06

-4,73

Kontrollrechnungen: Die Steilheit beträgt hier etwa

S0 ≈ 690 µA

V2 · (1,6 V − 0,75 V) = 587 µS. Verstärkung ohne

Gegenkopplung vU ≈ −S0 · ra = −5,6. Wo kommt die Abweichung her?

Bei Gegenkopplung Substratsteilheit berücksichtigen ...

ra

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

72/87

2. Grundschaltungen

1. Source-Schaltung

Übergangsfrequenz

In der Ersatzschaltung CGS ergänzen und CGD durch

äquivalente Kapazitäten zum Source nachbilden:

Rg

Ug

U GS

(1 − vU ) · CGD

+CGS

Cers

RS

S0 · U GS

≈ CGD

RL′

Ua

U e · S0 · R S

Über dem Source-Widerstand RS stellt die Stromquelle eine

zu U GS proportionale Spannung ein. Mit Cers zu einer

skalierten Kapazität zusammenfassbar.

G. Kemnitz

Cers

1+RS ·S0

·

U GS · (1 + RS · S0 )

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

73/87

2. Grundschaltungen

1. Source-Schaltung

Rg

U GS

Ug

(1 − vU ) · CGD

+CGS

Cers

Rg

Ug

Cers

1+RS ·S0

RS

S0 · U GS

≈ CGD

Ua

U GS · S0 · RS

⇓ funktionsgleich mit

U GS · (1 + RS · S0 )

RL′

S0 · U GS

≈ CGD

RL′

Ua

Die gate-seitige Knickfrequenz erhöht sich um den

Skalierungsfaktor:

fSIK1 = fSS1 · (1 + RS · S0 ) =

1 + RS · S0

2π · RG · (CGS + (1 − vU ) · CGD )

Die drain-seitige Knickfrequenz bleibt unverändert:

fSIK2 = fSS2

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

74/87

2. Grundschaltungen

G. Kemnitz

2. Drainschaltung

Drainschaltung

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

75/87

2. Grundschaltungen

2. Drainschaltung

Übertragungsfunktion

Für Uth < Ue < UV + Uth Einschnürrbereich. Variante 1:

Verbindung des Substrats mit Source (UBS = 0):

G. Kemnitz

Ue = Ua + UGS = Ua +

r

2 · ID

+ Uth

K

Ua

Arbeitspunkt

Ue

·

vU = 0,92, ra = 3,8 kΩ

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

76/87

2. Grundschaltungen

2. Drainschaltung

Variante 2: Verbindung Substrat mit Masse (UBS = −Ua ):

Ue = Ua + UGS = Ua +

r

p

p

2 · ID

+ Uth.0 + γ ·

Uinv + Ua − Uinv

K

Ua

Übertragungsfunktion bei

Verbindung von Substrat

und Source

RS

Arbeitspunkt

Ue

Kleinsignalparameter mit .tf V(a) Ve: vU = 0,75,

ra = 3,5 kΩ

Substratsteuerfaktor senkt die Verstärkung

Ausgangswiderstand RS

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

77/87

2. Grundschaltungen

2. Drainschaltung

Kleinsignalverhalten

Rg Gate

ug

Source

ue

S0 · (ue − ua )

rDS

RS

ua

RL

Der Stromanteil −S0 · ua der Quelle wirkt

Eingangsspannungsänderungen entgegen. Regelung.

Schwingungsgefahr bei zu hoher Steilheit?

Ausgangswiderstand ra geringer als RS k rDS .

Für groÿe Steilheiten strebt vU gegen eins.

Substrat mit Source verbunden: vU = 0,92, ra = 3,8 kΩ

Substrat mit Masse verbunden: vU = 0,75, ra = 3,5 kΩ

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

78/87

2. Grundschaltungen

2. Drainschaltung

Übergangsfrequenz

Am Eingang liegt die Gate-Drain-Kapazität. Die

Gate-Source-Kapazität liegt zwischen Ein- und Ausgang und

ist wegen ua ≈ ue vernachlässigbar:

Rg Gate

Ug

ue

Source

CGD

S0 · (U e − U a )

rDS

RS

Ua

RL

Übergangsfrequenz der Spannungsverstärkung:

fV0 ≈

1

2π · Rg · CGD

Für eine hohe Grenzfrequenz mehrere Drainschaltungen

verketten. Erst eine mit sehr kleiner Transistorbreite

(kleinem CGD und S0 ), dann mit zunehmend gröÿerer ...

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

79/87

2. Grundschaltungen

G. Kemnitz

3. Gateschaltung

Gateschaltung

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

80/87

2. Grundschaltungen

3. Gateschaltung

Übertragungsfunktion

Ua

Arbeitspunkt

Einschnürrbereich

Ue

Steigende Eingangsspannung mindert UGS , damit auch ID ,

den Spannungsabfall über RD und erhöht Ua .

Bei sehr hoher Steilheit bleibt UGS nahezu konstant.

Verstärkung vU = RRDS . Wäre hier 10. Die Verstärung im

Arbeitspunkt ist aber nur vier.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

81/87

2. Grundschaltungen

3. Gateschaltung

Kleinsignalverhalten

Ersatz des Transistors durch eine im Arbeitspunkt linearisierte

spannungsgesteuerte Stromquelle und rDS .

Rg

ie

Source

ue = −uGS

Gate

ug

rDS

ia

Drain

S0 · uGS

RD

ua

RL

Eingangswiderstand:

Verstärkung:

RD + rDS

d ue re =

≈

d ie ie =0

1 − S · rDS

d ua vU =

≈ S · RD

d ue ia =0

Ausgangswiderstand:

re =

G. Kemnitz

·

d ua

≈ RD

d ia

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

82/87

2. Grundschaltungen

3. Gateschaltung

Übergangsfrequenz

Die Gate-Source- und die Drain-Source-Kapazität liegen zwischen

Ein- bzw. Ausgang und Masse. rDS lässt sich durch re nachbilden,

der zur Abschätzung der Zeitkonstante parallel zu Rg wirkt.

Rg

ug

S0 · uGS

Source

ue

CGS

Gate

re

Drain

CDS

RD

ua

RL

Für CGS ≈ CDS und RD Rg k re hat die Drainseite die gröÿere

Zeitkonstante:

CGS · Rg k re CDS · RD

und bestimmt die untere Grenzfrequenz:

G. Kemnitz

fGS0 ≈

·

1

2π · CDS · RD

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

83/87

2. Grundschaltungen

G. Kemnitz

4. Aufgaben

Aufgaben

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

84/87

2. Grundschaltungen

4. Aufgaben

Aufgaben

Begründen Sie anhand der Übertragungskennlinie einer

Source-Schaltung, warum nur der Kennlinienbereich, in dem

der Transistor im Einschnürrbereich arbeitet, von

Verstärkern genutzt wird.

(Beim Übergang in den Sperrbereich und in den aktiven

Bereich nimmt die Verstärkung drastisch ab.)

Bestimmen Sie für eine xxx-Schaltung den

Eingangswiderstand, Ausgangswiderstand oder die

Verstärkung.

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

85/87

2. Grundschaltungen

4. Aufgaben

Kaskadierte Drainschaltung

In der nachfolgenden Schaltung (2x Drainschaltung) seien

die Kanallängen der Transistoren jeweils 1µm. Der

Steilheitsparameter je µm Transistorbreite sei 70 V2µA

und

·µm

fF

die Gate-Source-Kapazität je µm Transistorbreite 1 µm .

Wie ist die Transistorbreite von T2 zu wählen, damit die

Gesamtschaltung einen Ausgangswiderstand von 100 Ω hat?

Welche Eingangskapazität resultiert daraus für T2.

Wie ist die Transistorbreite von T1 zu wählen, damit beide

RC-Glieder in der Ersatzschaltung dieselbe

Übergangsfrequenz haben? (Für die Lösung fehlen Formeln

in den Folien!)

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

86/87

2. Grundschaltungen

4. Aufgaben

Granzfrequenz Gateschaltung

Wie ändert sich die Steilheit mit dem Drainstrom.

In der nachfolgenden Schaltung nimmt der

Steilheitsparameter und die Drain-Source-Kapazität

proportional mit der Transistorbreite zu. Wie ändert sich das

Verstärkungs-Bandbreiteprodukt mit der Transistorbreite?

G. Kemnitz

·

Institut für Informatik, Technische Universität Clausthal

9. Juli 2013

87/87