Ausarbeitung des Fragenkatalogs zur Vorlesung Elektronik und

Werbung

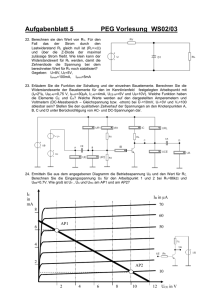

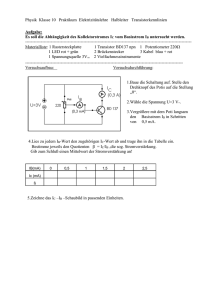

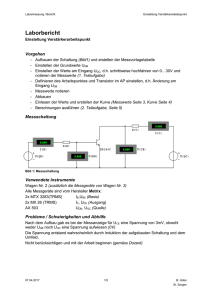

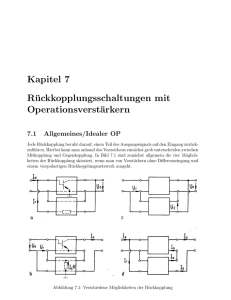

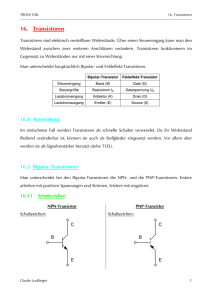

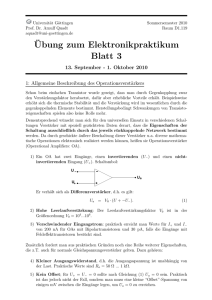

Ausarbeitung des Fragenkatalogs zur Vorlesung Elektronik und computerunterstützte Messtechnik zuletzt bearbeitet von Martitsch Andreas am 23.09.2008 Anmerkung: Für Fragen, Anregungen, Ergänzungen (vor allem neue bzw. bessere Grafiken von Schaltplänen, Kennlinien, Signalverläufen,...etc im jpeg-Format), Kritik bin ich unter meiner E-Mail-Adresse: [email protected] erreichbar. 2 Inhaltsverzeichnis 1 Dioden 5 2 Bipolartransistoren 7 3 Feldeffekttransistoren 19 4 Operationsverstärker 23 5 OPV - Anwendungen 27 6 Kippschaltungen 29 7 Grundlagen der Digitaltechnik 35 8 Schaltwerke (Sequentielle Logik) 47 9 DA- und AD-Umsetzer 55 10 11 bis 14 63 3 Inhaltsverzeichnis 4 1 Dioden 1. Skizzieren Sie die Diodenkenlinie für die Durchlassrichtung, sowohl für eine Germanium- als auch eine Siliziumdiode, in linearer Darstellung, Wie Bestimmen Sie die Durchlassspannung UD aus der Kennlinie? UD kann durch Schneiden der Tangente an die Kennlinie mit der UD -Achse bestimmt werden Abbildung 1.1: Diodenkennlinie einer Ge-Diode in Durchlassrichtung Abbildung 1.2: Diodenkennlinie einer Si-Diode in Durchlassrichtung 5 1 Dioden 2. Welche Temperaturabhängigkeit zeigen Dioden ? C Mit steigender Temperatur nimmt der Sperrstrom stark zu ( dI = 7% / dT US =const ◦ C). D Mit zunehmender Temperatur wird die Schwellspannung etwas herabgesetzt ( dU dT ID =const = -1,7 mV ) K 3. Diskutieren Sie das Temperaturverhalten von Halbleiterdioden mit Hilfe der I-U-Kennlinien? Abbildung 1.3: Diodenkennlinie in Durchlassrichtung für verschiedene Temperaturen Abbildung 1.4: Diodenkennlinie in Sperrrichtung für verschiedene Temperaturen 6 2 Bipolartransistoren 1. Skizzieren Sie eine typische Eingangskennlinie eines npn-Transistors, und geben Sie an, wie der differentielle Eingangswiderstand rBE für einen Arbeitspunkt A bestimmt wird. Der Anstieg der IB -UBE -Kennlinie in einem bestimmten Kennlinienpunkt ergibt den differentiellen oder dynamischen Eingangswiderstand rBE in diesem Kennlinienpunkt. BE BE = ∂U = UIBT rBE = ∆U ∆IB ∂IB UCE =const. Abbildung 2.1: Eingangsngskennlinienfeld eines Bipolartransistors 2. Skizzieren Sie eine typisches Ausgangskennlinienfeld eines npn-Transistors. Wie wird der differentielle Ausgangswiderstand rCE fur einen Arbeitspunkt A bestimmt. Ausgangskennlinie beschreibt den Zusammenhang zwischen IC und UCE für verschiedene Werte von UBE bzw. IB . Der Anstieg der IC -UCE -Kennlinie in einem bestimmten Punkt ergibt den differentiellen (dynamischen) Ausgangswiderstand in diesem Arbeitspunkt. CE CE rCE = ∆U = ∂U ∆IB ∂IB IB =const 7 2 Bipolartransistoren Abbildung 2.2: Ausgangsngskennlinienfeld eines Bipolartransistors 3. Was versteht man unter Vierpolparametern (h-Parametern)? Welchem 4-Pol-Parameter entspricht der Kennwert β? Die 4-Pol-Parameter geben die Steigungen (partiellen Ableitungen) der Transistorenkennlinien im Arbeitspunkt des 4-Quadranten-Kennlinienfeldes an. ∂UBE ∂IB A = h11e = rBE ∂IC ∂IB A = h21e = β = rBE ∗S ∂UBE ∂UCE A ∂IC ∂UCE A = h12e = D 1 = h22e = rCE 4. Erklären Sie die Arbeitsweise eines npn-Transistors(Kennlinienfeld). Wie kommt es zu einer Strom- bzw. Spannungsverstärkung? Der npn-Transistor besteht aus einer relativ dünnen p-leitenden Zone zwischen 2 n-leitenden Zonen. Im Verstärkerbetrieb befindet sich der pn-Übergang EmitterBasis in Durchlassrichtung, Basis-Kollektor in Sperrrichtung. Durch Anlegen einer positiven UBE . 0 werden Elektronenlöcher in das Basisgebiet hineingebracht (Ladungsträgerinjektion) und diffundieren auch in den Basis-Kollektor-Bereich, wodurch dieser leitend wird. Bei einer UBE / 0 werden die Elektronenlöcher aus der Raumladungszone abtransportiert. UBE beeinflusst somit die Rate mit der die Elektronen in das Basisgebiet injiziert werden und damit den Strom der am Sperrschichtrand ankommt ⇒ Durch eine Änderung der Steuerspannung UBE im Eingangskreis kann der IC im Ausgangskreis gesteuert werden (spannungsgesteuerte Stromquelle) ⇒ ein kleiner Löcherstrom steuert einen großen Elektronenstrom (→ dadurch Stromverstärkung) ⇒ dadurch ändert sich der Spannungsabfall am 8 Kollektorwiderstand RC & somit die Spannung am Lastwiderstand (Spannungsverstärkung) Abbildung 2.3: Rückwirkungsungskennlinienfeld eines Bipolartransistors Abbildung 2.4: Stromsteuerungskennlinienfeld eines Bipolartransistors 5. Geben Sie den Zusammenhang zwischen Eingangswiderstand und Basisstrom für die Emittergrundschaltung an. rBE = UT IB , mit UT . . . Temperaturspannung 6. Wie groß ist die Spannungsverstärkung für den Transistor als Verstärker in der Kollektorgrundschaltung? Die Ausgangsspannung der Kollektorschaltung ist immer etwas kleiner als die Eingangsspannung. Die Verstärkung ist näherungsweise 1. 9 2 Bipolartransistoren VU = dua due = S∗Re 1+S∗Re ≈ 1, S ∗ Re ≫ 1 7. Gegeben ist ein Transistorverstärker (npn) mit einem Basisspanungsteiler füer die Arbeitspunkteinstellung und einer Spannungsverstärkung A =150. Welches Kollektorruhepotential stellt sich nach einer Tempera◦ turerhöhung von 20 C ein? Die Basisemitterspannung nimmt um 2mv/K bei Temperaturerhöhung ab. dUB = 2mV , dϑ K ∂VC,A = V U ∂ϑ ∆IC = S ∗ dUdϑBE ∗ ∆ϑ ∗ 2mV → ∆VC,A = -6V K 8. Gegebenist ein Transistorverstärker in Emittergrundschaltung mit folgender Arbeitspunkteinstellung: Kollektorgleichspannung UCE = 4V, Kollektorgleichspannung IC = 2mA, Betriebsspannung UB = 15V. Wie groß kann die maximale, aber unverzerrte Kollektorwechselspannung werden (SKIZZE!!) CE RC = UB −U = 5.5 kΩ ⇒ UCE = 0V: IC ≈ 3mA, UCE = 15V: IC =0 ⇒ maximale IC unverzerrte Kollektorwechselspannung ca. 3,9 V 10 Abbildung 2.5: Maximal unverzerrte Kollektorwechselspannung 9. Der Arbeitspunkt einer Verstärkerstufe soll temperaturstabilisiert werden. Welche Maßnahmen kann man ergreifen? Wird benötigt, da mit steigender Temperatur IC steigt. Bei den ersten beiden Methoden ist es nötig, dass Transistor und temperaturabhängiges Kompensationselement möglichst gleiche Temperatur besitzen • Einbau eines NTC-Widerstandes (Negative Temperature Coefficient bzw. Heißleiters). Steigt die Temperatur, so sinkt der Widerstand des NTC-Widerstandes → geringer Basisstrom, wodurch der Anstieg des IC bei geeigneter Dimensionierung des NTC-Widerstandes kompensiert werden kann → Arbeitspunktstabilisierung • Einbau einer Diode. Durch den Einbau einer Diode mit ähnlichem Temperaturgang wie der Transistor erfolgt bei Temperaturanstieg ein Absinken der UBE ⇒ Basisstrom blebt konstant. 11 2 Bipolartransistoren Abbildung 2.6: Temperaturkompensation mittels Diode • Stromgegenkopplung: In die Emitterleitung wird ein Widerstand RE eingebaut, welcher bei Zunahme von IC infolge einer Temperaturerhöhung, selbstätig eine Abnahme der UBE bewirkt → Stromanstieg verhindert. Die Ausgangsgröße ICA wirkt auf den Eingang zurück ⇒ Stromgegenkopplung. Vorteile: kein Abgleich für die Einstellung des Arbeitspunktes bzw. optimale Stabilisierung nötig Änderungen erfolgen selbsttätig, Nachteil: schlechters Signalverhalten (RE wird deshalb häufig durch einen Kondensator kurzgeschloßen) Abbildung 2.7: Temperaturkompensation mittels Stromgegenkopplung • Spannungsgegenkopplung: Ein Teil der Ausgangsspannung wird über Widerstand R1 auf die Basis zurückgeführt (es wirkt die Ausgangsgröße UCE,A auf den Eingang). Dadurch, dass der Spannungsteiler R1 , R2 an UCE,A angeschlossen ist, verkleinert sich bei Temperaturerhöhung UBE , sodass ein weiters Absinken von UCE verhindert wird. Vorteil: Widerstandswerte gut vorausberechenbar, Arbeitspunktstabilisierung erfolg selbsttätig. Nachteil: Stablisierung 12 schlechter als bei Stromgegenkopplung, Einfluss auf das Signalverhalten der Schaltung (wieder Abhilfe durch Kondensatoren) Abbildung 2.8: Temperaturkompensation mittels Gleichspannungsgegenkopplung 13 2 Bipolartransistoren 10. Welche Parameter beschreiben die Eigenschaften eines Impedanzwandlers? Skizzieren Sie die zwei möglichen Schaltungsvarianten (Verwendung eines pnp-Transistors bzw. OPV) und zeigen Sie die Unterschiede der beiden Schaltungen Impedanzwandler besitzen einen großen Eingangswiderstand und einen geringen Ausgangswiderstand (beschreibenden Parameter: re und ra ). Sie werden daher verwendet um Signalquellen nicht zu sehr zu belasten. • PNP-Transistor: Eingangs- und Ausgangswechselspannung sind phasengleich, Emitterpotential folgt Basispotential (Emitterfolger), Verstärkung näherungsweise 1, besitzt ∗RL (sehr hoch), ra ≈ rBEβ+Ri hohe Stromverstärkung, re ≈ R1 k R2 k β ∗ RREE+R L (sehr klein) ⇒ Sehr kleine Ausgangswiderstände erfordern deshalb hohe Basisbzw. Kollektorgleichströme im Arbeitspunkt Abbildung 2.9: Impedanzwandler bestehend aus einem pnp-Transistor • OPV: Eingangs- und Ausgangswechselspannung wieder in Phase, re ≈ 10 MΩ bis 10 TΩ, ra ≈ 0; Gleichtaktsignale werden nicht verstärkt, Differenzensignale sehr stark, Ausgangswiderstand ist um Schleifenverstärkungsfaktor kleiner als der Ausgangswiderstand des nicht gegengekoppelten OPVs. Am Ausgang wirkt die Schaltung wie eine Spannungsquelle. 14 Abbildung 2.10: Impedanzwandler bestehend aus einem OPV 11. Wie arbeitet ein Unijunktiontransistor (J-FET)? Nach Anlegen einer Spannung zwischen Drain und Source dehnt sich die Sperrschicht in den n-leitenden Kanal aus Ab einer bestimmten spannung (UP -PinchoffSpannung) berühren sich die Sperrzonen. Der Kanal ist nur abgeschnürt und der FET sperrt. Bis zu diesem Punkt steigt der Drainstrom linear mit der DrainSource-Spannung. Der Drainstrom ID kann durch die negative UGS , durch Verbreiterung der Sperrzone um p-Gebiete, gesteuert werden ⇒ Der Drainstrom wird durch die Sperrschichten gesteurt (Sperrschicht-FET). Sehr hoher Eingangswiderstand (108 bis 1010 Ω) ⇒ Sperrstrom im Bereich von 5nA bis 20nA, Steuerung wird hier durch eine Spannung erreicht 12. Es sind die Verstärkerkennwerte Vu , re und ra des gegebenen Transistorverstärkers zu berechnen. Arbeitspunkt: UCE = 6V VU = I β∗RC , rBE UT (UT = 26mV) IB UB −UCE = 4mA RC rBE = IB = C,A , IC,A = β R1 ∗ IB,A = UB − UBE,A ⇒ UBE,A = 2.8 V → rBE = 700Ω → VU ≈ 143 ra = Rc = 1kΩ, re = Rc k ra =7.52kΩ 15 2 Bipolartransistoren 13. Welche Größen bestimmen den Eingangswiderstand der Kollektorschaltung? Es ist auch das Schaltbild anzugeben! re = R1 k R2 k re,tr , re,tr = β ∗ RE k RL 14. Was versteht man unter Darlingtonschaltung? Es ist auch das Schaltbild anzugeben! Unter der Darlingtonschaltung versteht man zwei in Serie geschaltete Kollektorschaltungen. Sie findet Verwendung im Fall, dass der Eingangswiderstand einer 16 Kollektorschaltung verhältnismässig klein (nur sehr hochohmig wenn Parallelschaltung von RE ∗ RL genügend groß ist) ist und damit der Signalquelle eine beträchtliche Leistung entnimmt (z.B: oft muss Signal einer hochohmigen Quelle auf niederohmigen Verbraucher gegeben werden (Koaxialkabel)). Inerster Näherung ist die Stromverstärkung der Darlingtonschaltung gleich dem Produkt der Stromverstärkungen der einzelnen Transistoren: Vi,ges = β1 ∗ β2 15. Nennen Sie die zentrale Eigenschaft des Differenzenverstärkers. Zentrale Eigenschaft: Der Differenzenverstärker verstärkt die Differenzspannung zwischen den beiden Eingängen unabhängig von der Gleichtaktspannung, solange diese innerhalb eines zulässigen Bereichs liegt. Bei der Verstärkung von Gleichspannungen sind kleinste Änderungen in der Arbeitspunkteinstellung zu vermeiden. Beim Differenzenverstärker wird dies (der Temperaturdrift der Basis-Emitter-Spannung) durch Einbau eines zweiten Transistor der unter gleichen Bedingungen arbeitet kompensiert (hierfür wird eine völlig symmetrische Schaltung vorausgesetzt). Gleichtaktunterdrückung: Die Konstantstromquelle sorg im Gleichtaktmode dafür, dass unabhängig von der Eingangsspannung keine Änderung der Ausgangsspannung auftritt. Differenzenverstärkung: Bei schiefsymmetrischer Aussteuerung mit einer Differenzenspannung UD = Ue1 - Ue2 ändert sich die Stromverteilung → Die Ausgangs- 17 2 Bipolartransistoren spannung bei Differenzaussteuerung nicht konstant (Stromverteilung zwischen Kollektorströmen hängt von Differenzspannung ab → Änderung der Basis-EmitterSpannung der Transistoren: dUBE1 = -dUBE2 = 12 ∗ dUD : Emitterspannung bleibt konstant ⇒ Gesamte Differenzenverstärkung wie bei Emitterschaltung AD = −S ∗ RC ) Gleichtaktaussteuerung: Eine Änderung von UGl ¨’andert nichts an der Stromverteilung → Ausgangsspannung bleiben bei Gleichtaktaussteuerung im Idealfall konRc stant (Gleichtaktverstärkung im Idealfall Null, real 10−4 bis 1, AGl ≈ − 2R ) E Gleichtaktunterdrückung(CMRR): gibt in dB das Verhältnis der Gleichtaktspannung zur Differenzenspannung an, welche die gleiche Ausgangsspannung bewirkt, wie die Gleichtaktspannung. Der Differenzenverstärker verstr̈kt das Gleichtaktsignal um einen Faktor G schw¨’acher als das Differenzsignal, er unterdr¨’uckt also ein eventuell vorhandenes GleichtaktD = 2∗S∗RE ) signal (G= 20 ∗ AAGl 16. Aus welcher Kennlinie bestimmt man den differentiellen Eingangswiderstand rBE eines npn-Transistors für einen Arbeitspunkt A. Es ist eine Skizze anzugeben Man bestimmt rBE aus der Eingangskennlinie des Transistor ∂UBE = rBE ∂IB A Abbildung 2.11: Bestimmung des differentiellen Eingangswiderstandes 18 3 Feldeffekttransistoren 1. Erklären Sie die Eigenschaften eines Verarmungs-IG-FET und skizzieren Sie die beiden Kennlinien Verarmungstyp (oder auch selbst leitender Ty) bedeutet, dass dieser sowohl durch positive als auch durch negative Gate-Source-Spannungen gesteuert werden kann. Verarmungs-IG-FET ist auch bei UGS = 0 leitend. ID kann durch die Gatespannung (welche die Kanalbreite steuert) gesteuert werden. Bei positiver UGS werden unterhalb des Gates Elektronen angereichert (es kehrt sich unterhalb des Gates der Ladungstyp um, zwische Source und Drain entsteht ein leitender n-Kanal), Uth . . . Schwellspannung Abbildung 3.1: Kennlinien des Verarmungs-IG-FETs 2. Erklären Sie die Eigenschaften eines PN-FET (Sperrschicht-FET, JunctionFET) und skizzieren Sie die beiden Kennlinien analog zu 2.11 (stichwortartig), Eigenschaften: Pinchoff-Voltage, nach Anlegen einer UDS dehnt sich die Sperrschicht in den n-leitenden Kanal aus, Steuerung von ID durch negative UGS ⇒ Sperrzonenverbreiterung um p-Gebiete, Drainstrom wird 19 3 Feldeffekttransistoren durch Sperrschichten gesteuert (Sperrschicht-FET) sehr hoher Eingangswiderstand 108 bis √ 1010 Ω, PN-FET ist spannungsgesteuert rDS ∝ ID , Übertragungskennlinie vermittelt den Zusammenhang von UGS und ID , nicht lineare Beziehung: ID = IDS ∗ (1 − UUGS ), IDS fließt auch bei UGS =0V, Anstieg P √ ∂ID 2 der Kennlinie gibt Steilheit S an: S= ∂U IDS ID , S < BipolarU =const. = UP ∗ GS DS transistoren → VU,max = S ∗ rDS Bipolartransistoren; liegt zwischen Gate und Source eine Spanung an → so gut wie kein Stromfluss → rDS näherungsweise konstant (1010 bis 1014 Ω, Sperrstrom Isperr ≈ 5nA bis 20nA) Abbildung 3.2: Kennlinien des PN-FETs 3. Welchen Vorteil haben PN-FETs gegenüber IG-FETs MOSFETs sind sehr empfindlich gegenüber statischen Aufladungen des Gates gegen das Substrat 4. Welches Verhalten bezüglich der Stromleitung ohne Aussteuerung haben Verarmungs-IG-FETs und Anreicherungs-IG-FETs 20 Verarmungstyp: selbstleitend, Anreicherungstyp: selbstsperrend; 5. IG-FETs (MOS-FETs) sind besonders empfindlich gegenüber elektrostatischen Aufladungen. Was ist die Ursache dieser Empfindlichkeit? Die Ursache ist, dass der Gateanschluss mit dem Substrat eine Kapazität bildet (CGS = 2 bis 5 pF), wodurch es schon bei geringen Ladungsmengen zum Durchsclag ) kommt (U = Q C 6. Was versteht man unter Steilheit S eines IG-FETs S= ∂ID ∂UGS = √ 2 ∗ β ∗ ID = β ∗ (U − Uth ) ≈ 5 bis 12 mA , V Uth . . . Schwellspannung 7. Wodurch wird der Drainstrom beim unipolaren Transistor gesteuert? ID wird beim unipolaren Transistor durch Gatespannung gesteuert (stromlos) 21 3 Feldeffekttransistoren 8. Erklären Sie die Eigenschaften eines Anreicherungs-IG-FET und skizzieren Sie die beiden Kennlinien Anreicherungstyp (selbstsperrend): Bei UGS =0 oder offenem Eingang ist Strecke zwischen Drain und Source gesperrt. ID liegt im ohmschen Bereich ID = β ∗ (UGS − 2 , rDS = 10 kΩ bis Uth ) ∗ UDS , Abschnürbereich ID ≈ β∗(UGS2−Uth ) , S = 5 bis 12 mA V 50 kΩ Durch Anlegen einer positiven UGS lässt sich ID steuern Abbildung 3.3: Kennlinien des Anreicherungs-IG-FETs 22 4 Operationsverstärker 1. Wie ist die Schleifenverstärkung g eines gegengekoppelten OPVs definiert? g = k ∗ AD ≈ AAD , mit A = UUae . . . Betriebsverstärkung k . . . Gegenkopplungsfaktor 2. Stellen Sie die wichtigsten Eigenschaften des idealen OPVs zusammen Verstärkungsfaktor Eingangswiderstand Ausgangswiderstand Untere bzw. Obere Grenzfrequenz Gleichtaktverstärkung Gleichtaktunterdrückung vollkommen symmetrischer Aufbau AD = ∞ re = ∞ Ω → beliebig belastbar ra = 0 Ω 0 Hz bzw. ∞ Hz (frequenzunabhängig - verwendbar für AC oder DC) AGl = 0 D =∞ G = AAGl UD = UP − UN = 0 P . . . P-Eingang, N . . . N-Eingang 3. Mit einem OPV, dessen Leerlaufverstärkung AD = 100000 beträgt, soll ein Verstärker mit Verstärkung A = 10 hergestellt werden. Wie groß muss der Rückkopplungsfaktor kR sein? AD A= 1+k∗A ⇒ 1 + k ∗ AD = D k= AD A −1 AD AD A ⇒ → k = 0.09̇ ≈ 0.1 23 4 Operationsverstärker 4. Skizzieren Sie die Schaltung eines invertierenden Spannungsverstärkers. Wie groß ist die Verstärkung? Knotenregel: Ue R1 + Ua RN Ue ⇒ + IN = 0 (mit IN =0) → − RUNa = R 1 Ua Ue =A=- RN R2 5. Skizzieren Sie die Schaltung eines nicht-invertierenden Spannungsverstärkers. Wie groß ist die Verstärkung? AD A= 1+k∗A D A= ( 1 , k k ∗ AD 1 AD , k ∗ AD 1 A = 1+ 24 RN , R1 1 k= RNR+R 1 6. Wie groß ist der unbekannte Widerstand RX , wenn der Spannungsmesser -8V anzeigt un der Strom über den 0.1 MΩ-Widerstand zum virtuellen Nullpunkt des OPV vernachlässigbar klein ist? 6 = -10, I2 ≈ 1mA (da I1 vernachlässigbar klein ist) A = UUae = − RRN1 = − 10 105 Ue = − U10a = 0.8V ⇒ Ue = I2 ∗ Rx ⇒ Rx = UI2e = 800Ω 25 4 Operationsverstärker 26 5 OPV - Anwendungen 1. Nennen Sie die Eigenschaften eines Fensterkomperators. Wie ist er aufgebaut? Der Fensterkomperator liefert am Ausgang y eine logische 1, wenn die Eingangsspannung Ue zwischen zwei Vergleichsspannungen U1 und U2 liegt; eine logische 0, wenn die Eingangsspannung außerhalb dieses Spannungsfensters liegt. 2. Skizzieren Sie eine Subtraktionsschaltung durch Rückführung auf eine Addition. Die Differenz kann gebildet werden, indem man ausgehend von der Summierverstärkerschaltung eine Eingangsspannung (z.B.: für die Differenz Ua = Ue1 −Ue2 ) invertiert (z.B. hierfür Ue1 ) 27 5 OPV - Anwendungen 28 6 Kippschaltungen 1. Wie unterscheidet sich eine digitale Größe von einer analogen Größe? Bei einer analogen Größe kann die Amplitude (Stärke des Signals) jeden Wert (kontinuierlich) zwischen einem Maximum und einem Minimum annehmen (z.B.: alle zu verarbeitenden Messgrößen: Temperatur, Druck, Winkel, Beschleunigung); Probleme bei Verarbeitung durch Rauschen bzw. Nichtlinearität des Signals führen zu Störungen beim Auslesen durch den Messwandler bzw. bei Übertragung des Signals. Bei der analogen Übertragung wird eine physikalische Größe direkt oder indirekt durch eine andere physikalische Größe übertragen. Bei einer digitalen Größe liegt die Information quantisiert in Form einer Zahlenkolonne, welche die Information mathematisch beschreibt vor(z.B.: bei einer Messung wird unterschieden ob eine Größe < oder > als bestimmte Schranken ist & wird mittels Boolscher Algebra weiterverarbeitet.). 2. Erläutern Sie die Arbeitsweise einer monostabilen Kippstufe und skizzieren Sie das Schaltzeichen. Wenn T2 völlig durchgesteuert ist ⇒ T1 gesperrt und sein Kollektor liegt auf V + (stabile Zustand) Falls nun über R2 ein positives Triggersigal gegeben wird ⇒ T1 leitend, Spannung am Kollektor schnell ab ⇒ T2 nun gesperrt Kollektorspannung steigt schnell an und verstärkt über R1 die Wirkung des Triggersignals. Durch diese Rückkopplung wird die Spannungsänderung erheblich beschleunigt bis T1 völlig gesättigt und T2 gesperrt ist ⇒ Spannungsänderung erfolgt so schnell, dass sich die Spannung am Kondensator nicht wesentlich ändert. Im Ausgangszustand liegt der linke Kontakt von C auf V +, während rechter Kontakt praktisch auf 0-Potential liegt ⇒ Kondensator über R auf Basisseite wieder positiv aufgeladen (Ohne T2 würde C so von -V+ auf V+ umgeladen werden mit t VB2(t) ≈ V + ∗(1 − 2 ∗ e− RC )) ⇒ Umladung wir plötzlich abgebrochen, wenn T2 29 6 Kippschaltungen leitend wird (VB2(t) = 0.6V ) ⇒ Schaltung kippt schnell in den stabilen Zustand zurück. Aus der Bedingung VB2(t) ≈ 0 folgt die Einschaltdauer: te ≈ RC ∗ ln 2 ≈ 0.7 ∗ RC 3. Was versteht man bei einer monostabilen Kippstufe unter retriggerbar und nicht retriggerbar? retriggerbar: ein während des Zeitablaufes eintreffendes Triggersignal bewirkt, dass die interne Zeit jeweils erneut startet & der aktive Schaltzustand dementsprechend zeitlich verlängert wird nicht retriggerbar: ein Triggersignal hat während aktiver Phase keine Wirkung 30 4. Was bedeutet H-Störabstand? Bei Digitalschaltungen ist es nur von Interesse, ob ein Zustand größer oder kleiner als ein vorgegebener Wert UH oder UL ist. Der Zustand H (High) ist erfüllt für Spannungen U > UH , der Zustand L (Low) für Spannungen U < UL worst-case-Bedingung am Eingang: SH = Ua − UH und SL = UL − Ua . . . SH : H-Störabstand, SL : L-Störabstand Unter H-Störabstand versteht man den Abstand zwischen UH und der Ausgangsspannung. (Beispiel: Transistor als Inverter) Abbildung 6.1: H-Störabstand 5. Erklären Sie den Begriff Gatterlaufzeit (Signal-Laufzeit) tpdL einer Digitalschaltung. Es ist auch eine Skizze anzufertigen! Die Gatterlaufzeit(tpd ) charakterisiert das Zeitverhalten einer Digitalschaltung, sie beschreibt in welcher Zeitspanne eine Eingangsspannungsänderung zu einem neuen Ausgangszustand führt: tpd = (tpdL +tpdH )∗ 21 mit tpdL : Zeitdifferenz zwischen 50%Wert der Eingangstaktflanke und 50%-Wert der abfallenden Ausgangstaktflanke (analog für tpdH ) Abbildung 6.2: Gatterlaufzet 31 6 Kippschaltungen 6. Erklären Sie die Schaltung Multivibrator mit Schmitt-Trigger (Schaltungsskizze und Signalverauf !) Abbildung 6.3: Multivibrator Abbildung 6.4: Multivibrator Bei der Verwendung von CMOS-Gattern kann man den Widerstand R hochohmig dimensionieren und damit auch relativ große Schwingungsdauern erreichen. In diesem Fall benötigt man jedoch einen Vorwiderstand am Eingang des Gatters G1 um die Belastung des RC-Gliedes klein zu halten, die dadurch entsteht, daß die Schutzschaltung am Eingang von G1 leitend wird, solange V die Betriebsspannung überschreitet bzw. das Massepotential unterschreitet. Eine Schaltung, bei der dieses Problem nicht auftritt, ist der Multivibrator mit Schmitttrigger. Dabei wird der Kondensator C über den Widerstand R bis zum Ausschaltpegel des Schmitt-Triggers aufgeladen und anschließend wieder bis zum Einschaltpegel entladen. Man erkennt im Signalverlauf, dass die Spannung am Kondensator zwischen den Triggerpegeln hin und her pendelt. Beim Einsatz von Low-power-Schottky TTL-Schaltungen muss R so niederohmig gewählt werden, dass er den Eingang bei dem fließenden Eingangsstrom unter den Einschaltpegel ziehen kann. Günstig sind Werte zwischen 220 Ω und 680 Ω. Diese Einschränkung 32 entfällt bei CMOS-Schmitt-Triggern. siehe TietzeSchenk S.609 7. Erklären Sie die Schaltung Univibrator für kurze Schaltzeiten (Schaltungsskizze mit Signalverlauf !) siehe Frage 6.2 Abbildung 6.5: Univibrator - Schaltung mit Signalverlauf 33 6 Kippschaltungen 34 7 Grundlagen der Digitaltechnik 1. Was versteht man unter Exklusiv-Oder-Glied? Geben Sie für dieses Glied die Wahrheitstabelle an Am Ausgang eines XOR-Gliedes liegt immer dann der Zustand 1 an, wenn beide Eingangszustände ungleich sind. y = (x1 ∧ x¯2 ) ∨ (x¯1 ∧ x2 ) x1 1 1 0 0 x2 1 0 1 0 y 0 1 1 0 Tabelle 7.1: Wahrheitstabelle 2. Wie viele Fälle hat die Wahrheitstabelle eines Oder-Gliedes mit sechs Eingängen? es existieren 26 = 64 mögliche Fälle, wobei nur 000000 den Ausgangszustand 0 liefert (alle anderen liefern am Ausgang eine 1) 3. Warum kann man alle möglichen Verknüpfungsschaltungen auch ausschließlich mit NAND-Glliedern aufbauen? Es ist möglich, da sich alle Grundverknüpfungsarten (NOT, AND und OR) mittels NAND-Gliedern erzeugen lassen. 4. Die Grundglieder UND, ODER, NICHT sollen 35 7 Grundlagen der Digitaltechnik • nur mit NAND-Gliedern • nur mit NOR-GLiedern aufgebaut werden Geben Sie die Schaltbilder an. 5. Wie lauten die beiden Morganschen Gesetze? x1 ∨ x2 = x¯1 ∧ x¯2 und x1 ∧ x2 = x¯1 ∨ x¯2 6. Wie ist die disjunktive Normalform (Oder-Normalform) aufgebaut? Geben Sie ein Beispiel an. Die Disjunktive Normalform ermöglcht es eine gesuchte logische Funktion, die eine vorgegebene Funktionstabelle erfüllt, auf die einfachste Form zu bringen: 36 • Man sucht in der Wahrheitstabelle alle Zeilen auf, in denen die Ausgangsvariable den Wert 1 besitzt. • Von jeder dieser Zeilen bildet man die Konjunktion aller Eingangsvariablen → und zwar setzt man xi ein wenn bei der betreffenden Eingangsvariable eine 1 steht, andernfalls x̄i . Auf diese Weise erhält man so viele Produktterme wie Zeilen mit y=1. • Die gesuchte Funktion erhält man schließlich, wenn man die Disjunktion aller gefundenen Produktterme bildet. BSP: ⇒ Zeile 3,5,7 ⇒ K3 = x¯1 x2 x¯3 , K5 = x1 x¯2 x¯3 und K7 = x1 x2 x¯3 Zeile x1 1 0 2 0 3 0 4 0 5 1 6 1 7 1 8 1 x2 0 0 1 1 0 0 1 1 x3 0 1 0 1 0 1 0 1 y 0 0 1 0 1 0 1 0 Tabelle 7.2: Wahrheitstabelle ⇒ y = K3 + K5 + K7 7. Welche Nachbarschaftsbedingungen gelten für KV-Diagramme mit 4 Variablen? Als Nachbarschaftsbedingung gilt, dass sich beim Übergang von einem Feld zum Nachbarfeld nur eine Eingangsvariable ändern darf. Zur Gewinnung der Konjunktion eier Gruppe ( Rechteck oder Quadrat mit 2,4,8,... Feldern) berücksichtigt man nur die Eingangsvariablen, die in allen Feldern einen konstanten Wert besitzen. 8. Was versteht man unter einer Schaltkreisfamilie Unter Schaltkreisfamilie versteht man logische Bausteine, die nach bestimmten Prinzipien aufgebaut sind (so existieren beispielsweise für die Grundverknüpfungsarten eine ganze Reihe von Schaltungstechniken, die sich hinsichtlich Leistungs- 37 7 Grundlagen der Digitaltechnik aufnahme, Betriebsspannung, H- & L-Pegel, Gatterlaufzeit und Ausgangsbelatsbarkeit unterscheiden.). Logische Bausteine einer Schaltkreisfamilie lassen sich problemlos zusammenschalten, Bausteine verschiedener Schaltkreisfamilien lassen sich nur unter bestimmten Voraussetzungen kombinieren. 9. Was sind binäre Spannungspegel? Unter Pegel versteht man eine elektrische Spannung, die zwischen einer Leitung und einem gemeinsamen Bezugspotential anliegt. Binärer Spannungspegel bedeutet, dass es nur zwei bestimmte Bereiche für einen gültigen Pegel gibt (z.B.: positive Logik: Spannungen U ≥ UH entsprechen einem H-Pegel (logische 1) und Spannungen U ≤ UL entsprechen einem L-Pegel (logische 0)), dazwischen liegt ein ungültiger (verbotener) Bereich. Mitglieder einer Schaltkreisfamilie produzieren immer Pegel, die an den Eingängen anderer Bausteine der gleichen Familie verwendet werden können. H: High, L: Low 10. Was bedeutet positive Logik oder negative Logik? positive Logik: 1-Zustand wird der Logik-Pegel H und dem 0-Zustand der LogikPegel L zugeordnet negative Logik: 1-Zustand wird der Logik-Pegel L und dem 0-Zustand der LogikPegel H zugeordnet 11. Nennen Sie die Namen der wichtigsten Schaltkreisfamilien? DTL - Dioden-Transistor-Logik LSL - Langsame-Störsichere-Logik TTL - Transistor-Transistor-Logik MOS-Schaltungen: Logische Bausteine aus MOS-FETs aufgebaut (fast keine Steuerleistung benötigt, kurze Schaltzeiten ⇒ PMOS-p-Kanal-MOSFETs, NMOS- nKanal-MOSFETs, CMOS - sowohl mit p- als auch n-Knal-MOSFETs) 38 12. Für ein Antivalenzglied wird die Gleichung Z = (a∧ ē)∨(ā∧e) angegeben. Es soll aus UND, ODER und NICHT Gattern gemäß der Gleichung aufgebaut werden. Zeichnen Sie das Schaltbild. 13. Man sagt, eine integrierte Schaltung sie in Bipolartechnik, die andere in MOS-Technik aufgebaut. Was sagen die Bezeichnungen aus? In der Bipolartechnik werden Bipolartransistoren verwendet (hiebei steuert wie für Bipolartransistoren (z.b.: npn-Transistor) typisch ein kleiner Löcherstrom einen großen Elektronenstrom) Bei der MOS-Technik werden MOSFETs verwendet (fast keine Steuerleistung, kurze Schaltzeiten) 39 7 Grundlagen der Digitaltechnik 14. Geben Sie das Schaltbild und die Wahrheitstabelle für die AntivalenzVerknüpfung mit drei Eingangsvariablen an. x1 1 1 1 1 0 0 0 0 x2 1 1 0 0 1 1 0 0 x3 1 0 1 0 1 0 1 0 y 1 0 0 1 0 1 1 0 Tabelle 7.3: Wahrheitstabelle XOR mit 3 Eingängen 15. Geben Sie das Schaltbild und die Wahrheitstabelle für die ÄquivalenzVerknüpfung mit drei Eingangsvariablen an. x1 1 1 1 1 0 0 0 0 x2 1 1 0 0 1 1 0 0 x3 1 0 1 0 1 0 1 0 y 0 1 1 0 1 0 0 1 Tabelle 7.4: Wahrheitstabelle XNOR mit 3 Eingängen 40 16. Welche Ausgangsstufen gibt es bei den TTL-Schaltugnen? Geben Sie die Schaltsymbole an. 17. Ein Gatter einer bestimmten Schaltkreisfamilie hat einen Ausgangsleistungsfaktor von 10. Was bedeutet das? Wie viele Eingänge derselben Schaltungsfamilie man anschließen kann, ohne daß der garantierte Störabstand unterschritten wird, charakterisiert man durch die Ausgangsleistungsfaktor (Fan Out). Ein Fan Out von 10 bedeutet also, daß man 10 Gattereingänge anschließen kann. Wenn die Ausgangsbelastbarkeit nicht ausreicht, verwendet man statt eines Standard-Gatters ein Leistungsgatter 18. Was bedeutet der Begriff gesättigte Schaltkreisfamilie? 41 7 Grundlagen der Digitaltechnik Eine gesättigte Schaltkreisfamilie (Logik) ist so dimensioniert, dass sie beim Durchschalten übersteuert und so voll in den Sättigungsbereich gelangt. z.B: Schaltungen der Standard-TTL-serie 74xx bestehen aus Bipolartransistoren, die als Schalter arbeiten. 19. Wie wirkt bei den TTL-Schaltungen ein offener Eingang auf den Ausgang? offene Eingänge wirken wie H-Pegel 20. Welche Verknüpfung erzeugt die nachfolgende Schaltung bei positiver bzw. negativer Logik. Geben Sie für beide Fälle die Wahrheitstabelle an. Fall 1 2 3 4 B A 0V 0V 0V +5V +5V 0V +5V +5V Z 0V +4.3V +4.3V +4.3V Tabelle 7.5: Logikpegel Fall 1 2 3 4 positive Logik B A Z 0 0 0 0 1 1 1 0 1 1 1 1 ODER negative Logik B A Z 1 1 1 1 0 0 0 1 0 0 0 0 UND Tabelle 7.6: Wahrheitstabelle für positive und negative Logik 42 21. Die Schaltfunkton einer binären Verknüpfung lautet Q = AB ∨C. Die gegebene Schaltfunktion ist durch NAND-Glieder zu realisieren. Hinweis: Verwenden Sie die doppelte Negation und die de Morgansche Regeln. Q = AB ∨ C = AB ∧ C̄ = A ∧ B ∧ C̄ 22. Für ein Äquivalenzglied wird die Gleichung Z = (A ∧ B)∨(Ā ∧ B̄) angegeben. Es soll aus Grundgliedern aufgebaut werden. Entwickeln Sie die 43 7 Grundlagen der Digitaltechnik Wahrheitstabelle und zeichnen Sie den Schaltplan. Fall 1 2 3 4 A 0 0 1 1 B 0 1 0 1 Z 1 0 0 1 Tabelle 7.7: Äquivalenzglied Abbildung 7.1: Äquivalenzglied aus Grundgliedern 23. Geben Sie die Schaltung eines 3-Bit-Adresskodierers an. 44 Abbildung 7.2: 3-Bit-Adresskodierer 24. Erklären Sie die Unterschiede zwischen einem Demultiplexer und einem Multiplexer. Es sind auch die Schaltzeichen anzugeben. Der Multiplexer legt eines von mehreren Eingangssignalen (di ) auf einen Ausgang. Das Eingangssignal wird dabei über die Adressiereingänge (ai ) ausgewählt. Der Demultiplexer legt mittels Adressiereingänge eine Eingangsinformation d auf verschiedene Ausgänge. Abbildung 7.3: Demultiplexer und Multiplexer 45 7 Grundlagen der Digitaltechnik 46 8 Schaltwerke (Sequentielle Logik) 1. Wodurch unterscheidet sich ein taktzustandsgesteuertes Flip-Flop von einem taktflankengesteuerten Flip-Flop? taktzustandgesteuert: währenddessen die Clock C=1 ist, reagiert das Flipflop auf den Eingangszustand. Bei C=0 speichert das Flipflop den alten Zustand. Störsignale können während C=1 den Ausgang beeinflussen. taktflankengesteuert: Bei taktflankengesteuerten Flipflops werden die Eingänge nur während der ansteigenden und/oder abfallenden Taktflanke aktiv → weniger störanfällig aufgrund kürzerer Zeiten der Aktivität. 2. Was versteht man unter einem Master-Slave-Flip-Flop? Ein Master-Slave-Flipflop besitzt eine Zwischenspeicherung und ist zweiflankengetriggert, d.h. das Master-Flipflop nimmt die Information von außen mit ansteigender Taktflanke auf und übergibt mit abfallender Taktflanke die Information an das Slave-Flipflop. 3. Beschreiben Sie ein transparentes RS-Flip-Flop aus NOR-Gattern. Es ist die Wahrheitstabelle anzugeben. Wenn S=1, R=0: Q̄ = S + Q = 1 + Q = 0, Wenn R=1, S=0: umgekehrter Ausgangszustand, Flipflop ist zurückgesetzt S R Q Q̄ 0 0 Q−1 Q−1 0 1 0 1 1 0 1 0 1 1 (1) (1) nicht zulässig Tabelle 8.1: Wahrheitstabelle JK-Flipflop 47 8 Schaltwerke (Sequentielle Logik) 4. Beschreiben Sie die Eigenschaften eines zweiflanken-getriggerten JKFlip-Flops. Es sind auch das Schaltzeichen und die Wahrheitstabelle anzugeben Der Eingangszustand R=S=1 führt bei RS-Flipflops zwangsläufig zu undefiniertem Verhalten. Bei einem JK-Flipflop wird das RS-Master-Slave-Flipflop folgendermaßen erweitert, sodass R & S nicht mehr gleichzeitig 1 werden können: Der Ausgang Q̄ des RS-Master-Slave-Flipflop wird mit dem neuen J-Eingang UNDverknüpft und auf den Master-Eingang S zurückgeführt, der Ausgang Q mit dem K-Eingang UND-verknüpft und auf den Master-Eingang R zurückgeführt. Der Ausgangszustand invertiert für J=K=1 bei jedem Taktimpuls. JK-Flipflops können als Frequenzteiler und Digitalzähler verwendet werden. C J 1 0 1 0 1 1 1 1 0 d K 0 1 0 1 d Qm+1 Qm 0 1 ¬Qm Qm Tabelle 8.2: Wahrheitstabelle JK-Flipflop Abbildung 8.1: Zweiflankengetriggertes JK-Flip-Flop 5. Erklären Sie die Bedeutung der Eingänge und die Arbeitsweise des in 48 der Abbildung dargestellten Flip-Flops. es handelt sich um ein JK-Master-Slave-Flip-Flop mit mehreren J- bzw. K-Eingängen, wobei die internen J- & K-Variablen nur für 011 bzw. 110 eins sind. Mit Set & Reset (taktunabhängig) lassen sich Master- und Slave-Flipflop setzen bzw. löschen. RS-Eingänge besitzen Priorität gegenüber JK-Eingängen, über C1 wird das Taktsignal eingespeist. Arbeitsweise siehe MS-Flipflops Die Wahrheitstabelle gilt nur dann, wenn sich während C=1 die JK-Eingänge sich nicht ändern. 6. Erklären Sie den Unterschied von ein- und zweiflankengestuerten FlipFlops? zweiflankengesteurt: Eingangszustand wird zwischengespeichert und erst an den Ausgang übertragen, wenn die Eingänge wieder verriegelt sind ⇒ zweiflankengesteuerte Flipflops nehmen bei ansteigender Taktflanke das Eingangssignal auf und schalten es bei abfallender Taktflanke zum Ausgang durch (ist dort verfügbar). Master-Flipflop nimmt die Information von außen auf und übergbt diese and das Slave-Flipflop. einflankengesteuert: Eingangsvariable wird nur beim Wechsel der Taktflanke von 0 auf 1 oder 1 auf 0 aufgenommen und, nachdem die Pufferung auf den Wert abgeschlossen ist, kurze Zeit später an den Ausgang weitergegeben. 7. Wodurch unterscheiden sich Synchron- und Asynchronzähler 49 8 Schaltwerke (Sequentielle Logik) Synchronzähler: alle Flipflops schalten/kippen gleichzeitig (synchron) Asynchronzähler: Flipflops schalten nicht gleichzeitig, sondern zeitlich nacheinander ⇒ Schaltverzögerug, die durch die Signallaufzeit gegeben ist. 8. Schalten Sie ein einflankengetriggertes SR-Flip-Flop so, dass es wie ein T-Flip-Flop arbeitet. Abbildung 8.2: Toggle-Flip-Flop aus einem einflankengetriggerten SR-Flip-Flop ( Q−1 , T = 0 Q= Q̄−1 , T = 1 50 9. Skizzieren Sie die Schaltung eines asynchron arbeitenden 3-Bit-Vorwärtszählers. Zu verwenden sind einflankengetriggerte JK-Flip-Flops, die mit der ansteigenden Taktflanke kippen. Abbildung 8.3: 3-Bit-Vorwärtszähler 10. Wie kann man aus einem asynchron arbeitenden 4-Bit-Dual Vorwärtszählers, der mit T-Flip-Flops aufgebaut ist, einen BCD-Vorwärtszähler machen? Die T-Flip-Flops solle mit abfallender Taktflanke kippen und einen taktunabhängigen Rückstelleingang haben, der mit 0-Signal das Flip-Flop rückstellt Im BCD-Code wird einer natürlichen Zahl (0 bis 9) eine 4-stellige Dualzahl zugewiesen. Um aus einem Dualzähler einen BCD-Zähler, der mit 0-Signal umkippt, zu machen, muss ein weiterzählen von 10 bis 15 verhindert werden. Dies geschieht durch eine NAND-Verknüpfung von Q2 und Q4 (dessen Ausgangssignal 0 wird, wenn Q2=Q4=1 (=Dualzahl≥10)) und auf die Reset-Eingänge der Flipflops zurückgeführt wird. 51 8 Schaltwerke (Sequentielle Logik) Abbildung 8.4: 4-Bit-Vorwärtszähler 11. Wie arbeitet die her dargestellte Schaltung? Skizzieren Sie die ZeitablaufDiagramme. Schaltung arbeitet als Zähler,w wobei über x-Eingang eingestellt werden kannn, ob der Zähler vorwärts x=0 oder rückwärts x=1 zählt. 52 Abbildung 8.5: Zeit-Ablauf-Diagramm 53 8 Schaltwerke (Sequentielle Logik) 54 9 DA- und AD-Umsetzer 1. Erklären Sie die Arbeitsweise eines Ad-Umsetzers nach dem Wägeverfahren. Es ist auch das Blockschaltbild zu zeichnen. digit at a time: Es wird in einem Schritt jeweils nur eine Stelle der zugehörigen Dualzahl ermittelt. Man benötigt so viele Vergleichsschritte, wie die Zahl Stellen besitzt und ebenso viele Referenzspannungen. Beim Wägeverfahren wird pro Messschritt ein Bit des Digitalwortes erzeugt. In sukzessiven Schritten wird mit Hilfe des Komparators geprüft, ob die zu wandelnde Spannung größer oder kleiner ist als die vom DAC erzeugte Spannung U(Z). Zunächst wird das höchstwertige Bit (MSB) gesetzt, das vom DAC in eine entsprechende Analogspannung U(Z) umgesetzt und mit der Eingangsspannung UE verglichen wird. Je nachdem, ob das Ergebnis U(Z) kleiner oder größer ist als UE wird die Referenzspannung zum Ergebnis addiert oder subtrahiert und die entsprechende Stelle der resultierenden Ausgangsbinärzahl auf 0 oder 1 gesetzt. Daraufhin wird dieser Vergleichsvorgang für die nächst niedrigere Binärstelle bis zu LSB wiederholt. Für einen N-Bit-Umsetzer sind somit N Vergleichsschritte notwendig, die sequentiell abgearbeitet werden müssen. Jedes Bit wird versuchsweise gesetzt. Wenn dadurch die Eingangsspannung überschritten wird, wird es gleich wieder gelöscht. Nach 8 Wägeschritten ist dann in diesem Beispiel die Umsetzung abgeschlossen. 55 9 DA- und AD-Umsetzer 2. Erklären Sie die Arbeitsweise eines AD-Umsetzers nach dem Ein-RampenVerfahren (Single Slope- oder Sägezahnverfahren). Es ist auch das Blockschaltbild zu zeichnen. (level at a time) Man zählt ab, wie oft man die Referenzspannung zur niedrigsten Stelle addieren muss, um die Eingangsspannung zu erhalten. Beträgt die größte darstellbare Zahl n, benötigt man also maximal n Schritte, um das Ergebnis zu erhalten. Umsetzdauer wesentlich größer als bei den anderen Verfahren. Sie liegt in der Regel zwischen 1 ms und 1 s. Die Eingangsspannung wird in eine dazu proportionale Zeit übersetzt. SagezahnU e e t − V0 ,Zählerstand: Z = ∆t = τ ∗ f UUref mit ∆t = τ UUref , spannung: VS = ref τ T Messgenauigkeit: bestenfalls 0.1 % 3. Erklären Sie die Arbeitsweise eines AD-Umsetzers nach dem ZweiRampen-Verfahren (Dual Slope- oder Doppelintegrationsverfahren). Es ist auch das Blockschaltbild zu zeichnen. Referenz- und Eingangsspannung werden integriert. Ruhezustand: S1 und S2 offen, S3 ist geschlossen ⇒ Ausgangsspannung des Integrators ist Null. Messbeginn: S3 offen und S1 geschlossen ⇒ Ue wird für eine durch den Messdauerzähler festgelegte Zeit t1 integriert. Ist Ue positiv, wird Integrator-Ausgang negativ und Komparator gibt den Taktgenerator frei. Referenzspannung integriert: S1 offen und S2 geschlossen. ⇒ Ausgangsspannung des Integrators steigt bis auf Ut = 0 Sei T die Periode des Taktgenerators und Z1 die Anzahl der Taktimpulse fur den Messdauerzähler, so gilt: t1 = Z1 T ⇒ Integratorspannung R t1 Z1 T 1 UI = − RC Ue dt = − UeRC Nach Ablauf von t1 liegt die Referenzspannung an 0 t ⇒ UI (t) = UI (t1 ) + Uref RC 56 Hat UI (t) Null erreicht, ist die Zeit t2 = Z2 T verstrichen. Z2 ist die Anzahl der e 2T 1T gezählten Impulse im Ergebniszähler ⇒ Uref ZRC = Ue ZRC ⇒ Z2 = Z1 UUref Weder Taktfrequenz 1/T noch Integrationszeitkonstante τ = RC gehen in das Ergebnis ein. 4. Erklären Sie die Arbeitsweise eines AD-Umsetzers nach dem Parallelverfahren. Es ist auch das Blockschaltbild zu zeichnen. (word at a time) Die Eingangsspannung wird gleichzeitig mit n Referenzspannungen verglichen und festgestellt zwischen welchen beiden sie liegt. Man erhält die vollständige Zahl in einem Schritt. Aufwand sehr hoch! Für jede mögliche Zahl wird ein Komparator benötigt. Eingangsspannung wird mit n Referenzspannungen verglichen. Aus einer Referenzquelle werden über einen Spannungsteiler die nötigen Spannungsstufen hier für n = 8 erzeugt und mit der Eingangsspannung über n − 1 Komparatoren mit diesen Stufen verglichen. Die unbekannte Spannung Ue wird mittels der Komparatoren mit den einzelnen Abgriffen der Normalen-Spannungsteiler verglichen. Alle Komparatoren, deren Spannungen an den Teilereingängen kleiner als Ue sind, liefern am Ausgang eine logische 1, alle anderen eine 0. Diese Werte werden mit einem Abtastimpuls D-Flipflops zugeführt und in der Dekodierlogik (Prioritätsencoder) in die N = ld n Bit umgesetzt. Hoher Aufwand durch große Anzahl von Präzisionswiderständen und Komparatoren. Geschwindigkeit des Umsetzers durch den langsamsten Komparator bestimmt. Die Linearität der AD-Umsetzer ist bei niedrigen Signal-Frequenzen gleich der Auflösung ± 1/2 LSB, zum Teil sogar ± 1/4 LSB. Bei hohen Signalfrequenzen steigt die Nichtlinearität jedoch an. Dadurch kan das niedrigste oder sogar auch das zweitniedrigste Bit unbrauchbar werden. 57 9 DA- und AD-Umsetzer 5. Vergleichen Sie die Umsetzfrequenzen und die Auflösung von AD-Umsetzern 6. Erklären Sie das Prinzip eines DA-Umsetzers. Es ist auch das Schaltbild zu zeichnen. Digital-Analog-Umsetzer haben die Aufgabe, ein binäres Datenwort(normalerweise eine Dualzahl D) in eine analoge Grß̈e umzusetzen. Eine N-Bit-Binärzahl wird über das Eingangsregister dem DA-Umsetzer zugeführt, der eine Ausgangsspannung UA bildet. Digitalwert Z soll mit einer Auflösung von N Bit als Dualzahl im Dualkode vorliegen und in paralleler Form (1 Bit pro Datenleitung) zur Verfügung stehen. unipolare Digital-Analog-Umsetzer (es konnen nur positive Zahlen verarbeitet werden): 0 ≤ Z ≤ Zmax = 2N −1 Dualzahl Zdual = zN −1 . . . z1 z0 durch ihre N Binärstellen zi festgelegt: Z = 2N −1 zN −1 +. . .+22 z2 +21 z1 +20 z0 Stufenbreite ULSB entspricht 58 der Differenz im analogen Ausgangssignal zwischen zwei aufeinander folgenden Digitalwerten: ULSB = UAmax 2N UAmax : maximal mogliche Ausgangsspannung des DAU. Entspricht dem zum niedrigsten Bit gehorenden Analogwert. (Least Significant Bit, LSB). Analoge AusN gangsspannung uA des DAC: 0 ≤ ua ≤ ULSB (2N − 1) = UAmax 2 2N−1 Konversionsrate: Anzahl der Digitalwerte pro Zeiteinheit die in analoge Werte umgesetzt werden konnen. Konversionszeit: Reziprokwert der Konversionsrate. Technische Realisierung mittels: • Summation gewichteter Ströme: Kennzeichen dieses Prinzips ist die konstante Betriebsspannung Uref und dual gestufte Widerstände. Die Umsetzung einer Dualzahl in eine entsprechende Analogspannung wird schaltungstechnisch mit Hilfe eines Summierverstärkers erreicht. Je nachdem welcher Schalter nun durch die Digitaleingänge betätigt wird, fließen die Ströme über den Operationsverstärker oder die Masse. URK = UA = (I3 S3 + I2 S2 + I1 S1 + I0 S0 ) ∗ Rk , S0 bis S3 können die Werte 0 oder 1 annehmen. S3 + 4 ∗ UREF S2 + 2 ∗ UREF S2 + 1 ∗ UREF S0 ) ∗ RK UA = (8 ∗ UREF R0 R0 R0 R0 UREF ∗RK =(8 ∗ S3 + 4 ∗ S2 + 2 ∗ S1 + 1 ∗ S0 ) ∗ R0 bei beliebiger Bitzahl n am Digitaleingang: UA = (2n−1 ∗ Sn−1 + 2n−2 ∗ Sn−2 + ∗RK . . . + 20 ∗ S0 ) ∗ UREF R0 ∗RK Maximalspannung: UAmax = (2n − 1) ∗ UREF R0 RK RK MSB = 2n−1 ∗ ∆U = 2n−1 ∗ UREF LSB = ∆U = UREF R0 R0 • Leiternetzwerk: Die Referenzspannung wird zunächst mit einem Leiternetzwerk entsprechend der dualen Wertigkeit geteilt. Die einzelnen Ströme können dann mit gleichartigen Widerständen gebildet werden. Die beiden Parallelwiderstände 2Rk”2R am Knoten C ergeben zusammen den Wert R. Gemeinsam mit dem Längswiderstand ergibt sich die Teilung 2. Zugleich erhält man am Knoten B die 59 9 DA- und AD-Umsetzer Parallelschaltung aus 2Rk(R+R) also wieder zusammen R und so kommt wiederum die Teilung 2 zum Knoten A hin zustande. Es entsteht eine duale Spannungsteilung. Die einzelnen Ströme I0 bis I3 stehen ebenfalls im Verhält, I1 = 14 UREF , I2 = 12 UREF , I3 = UREF nis 2 zueinander: I0 = 18 UREF 2R 2R 2R 2R Die Digitalschalter können wieder auf Masse (S = 0) oder auf den Verstärkereingang gestellt werden (S = 1). URK = UA = (I3 S3 + I2 S2 + I1 S1 + I0 S0 ) ∗ Rk = + 21 UREF ∗ S2 + 14 UREF ∗ S1 + 18 UREF ∗ S0 = S3 ∗ UREF 2R 2R 2R 2R ∗RK n−1 Bei beliebiger Bitzahl n: UA = (2 ∗Sn−1 +2n−2 ∗Sn−2 +. . .+20 ∗S0 )∗ U2REF n−1 ∗2R UREF n−1 n−2 0 Mit RK =R: UA = (2 ∗ Sn−1 + 2 ∗ Sn−2 + . . . + 2 ∗ S0 ) ∗ 2n Maximalspannung: UAmax = (2n − 1) UREF 2n Kleinster Spannungsschritt: LSB = ∆U = UREF 2n MSB = 21 ∗ UREF • DAU mit gewichteten Stromquellen: Teilströme werden durch gesteuerte Stromquellen erzeugt. Der gegengekoppelte Operationsverstärker N1 regelt die Basisspannung von V1 so, dass sich Besitzen die Transistoren ein konstanter Kollektorstrom I3 einstellt. I3 = URREF V V1 bis V6 die exakt gleiche Kennlinien, dann entstehen in diesen Transistoren ebenfalls konstante Ströme, die nur noch von den Emitterwiderständen abhängen. V2 erhl̈t den gleichen Strom wie V1, bei V3 bis V5 nehmen die Ströme in dualen Schritten ab. V5 und V6 haben wieder die gleichen Ströme. Dioden V7 bis V14 dienen als Umschalter. Für die maximale Ausgangsspannung, LSB und MSB ergeben sich die selben Gleichungen wie für das Leiternetzwerk. URK = UA = (I3 S¯3 + I2 S¯2 + I1 S¯1 + I0 S¯0 ) ∗ Rk , I2 = 12 ∗ I3 , I1 = 14 ∗ I3 , I0 = 81 ∗ I3 Mit I3 = URREF V REF ⇒ UA = (S¯3 + S¯2 12 + S¯1 14 + S¯0 18 ) ∗ Rk ∗U RV ¯ + 2n−2 ∗ Sn−2 ¯ + bei beliebiger Bitzahl n und RV = 2 ∗ RK : UA = (2n−1 ∗ Sn−1 60 . . . + 20 ∗ S¯0 ) ∗ UREF 2n 61 9 DA- und AD-Umsetzer 62 10 11 bis 14 1. Zeichnen Sie den Geräteplan und den Signalflussplan für eine Temperaturmesseinrichtung (Füllstandseinrichtung, Kraftmesseinrichtung, Längenmesseinrichtung,..) Abbildung 10.1: Geräteplan und Signalflussplan einer Temperatur-, Kraft- und Füllstandsmesseinrichtung 2. Skizzieren Sie den Aufbau und die Eigenschaften eines Instrumentenverstärkers. Ermöglicht eine hochohmige Verstärkung von Differenzspannungssignalen bei gleichN )(U1 − zeitig hoher Unterdrückung von störenden Gleichtaktsignalen. Ua = n(1+ 2R R1 63 10 11 bis 14 Abbildung 10.2: Instrumentenverstärker U2 ) 3. Skizzieren Sie den Aufbau und die Eigenschaften eines Logarithmierers. Abbildung 10.3: Logarithmierer Der Logarithmierverstärker wird eingesetzt, wenn sich die Sensoreigenschaften um mehrere Größenordnungen ändern, andererseits aber eine Signalverarbeitung durch einen Analog-Digital-Umsetzer nur in einem begrenzten Wertebereich erfolgt. 4. Skizzieren Sie das Prinzip eines Strom-Spannungs-Umformers. 64 Abbildung 10.4: Strom-Spannungsumformer 5. Skizzieren Sie das Prinzip eines Strom-Strom-Umformers. Abbildung 10.5: Strom-Strom-Umformer 6. Skizzieren Sie das Prinzip eines Spannungs-Spannungs-Umformers. Abbildung 10.6: Spannungs-Spannung-Umformer 65 10 11 bis 14 7. Skizzieren Sie das Prinzip eines Spannungs-Strom-Umformers. Abbildung 10.7: Spannungs-Strom-Umformer 8. Skizzieren Sie das Prinzip eines Ladungs-Spannungs-Umformers. Abbildung 10.8: Ladungs-Spannungs-Umformer 9. Warum muss die Abtastfrequenz eines AD-Umsetzers größer sein als die doppelte Signalfrequenz? 66 Die Abtastfrequenz eines Analog-Digital-Umsetzers muss größer sein, als die doppelte Analogwertfrequenz, damit nach einer späteren Digital-Analog-Umsetzung das Ursprungssignal (bis auf die Quantisierungseffekte) fehlerfrei rekonstruiert werden kann. Abbildung 10.9: Aliasing-Effekt anhand einer unterabgetasteten Schwingung 10. Beschreiben Sie die Temperaturmessung mit einem Thermoelement Werden zwei unterschiedliche Materialien A und B miteinander verlötet oder verschweißt und befinden sich die beiden Verbindungsstellen auf unterschiedlicher Temperatur bildet sich die Thermospannung aus. Die Summe der beiden Kontaktspannungen U1 und U2 ergibt die Thermospannung U. Die Thermospannung ist proportional der Temperaturdifferenz zwischen der Tem- 67 10 11 bis 14 peratur T2 der heißen Lötstelle und der Temperatur T0 der Vergleichsstelle. Soll die Temperatur T2 angegeben werden, so muss die Temperatur T0 (Vergleichsstelle) bekannt sein. Funktionsweise des Thermoelementes: An den freien Enden der beiden miteinander verbundenen Leiter wird bei einer Temperaturdifferenz entlang der Leiter aufgrund des Seebeck-Effekts eine elektrische Spannung erzeugt. Die Verbindungsstelle und die freien Enden müssen somit hierzu unterschiedliche Temperaturen aufweisen. Als Seebeck-Effekt wird das Auftreten einer Spannung zwischen zwei Stellen unterschiedlicher Temperatur eines Leiters genannt. Die Potentialdifferenz ist annähernd proportional zur Temperaturdifferenz, und abhängig vom Leitermaterial. Temperaturdifferenzen innerhalb eines Leiters heben sich stets auf, da die Enden zum Messen auf gleicher Temperatur liegen ms̈sen (sonst misst man zusätzlich die in der Messleitung entstehende Thermospannung). Wenn man jedoch zwei unterschiedliche Leitermaterialien verbindet, kann an den Enden eine Spannung gemessen werden, die wiederum annḧernd proportional zur Temperaturdifferenz zwischen den Enden und der Kontaktstelle ist. Bei metallischen Leitern treten Spannungen im Bereich einiger Mikrovolt bis Millivolt auf. Da die Proportionalitätskonstante eines einzelnen Leiters nicht gemessen werden kann, wird ein relativ zu Platin ermittelter thermoelektrischer Koeffizient angegeben. Dieser so genannte k-Wert gestattet es, die Thermospannung der Metallpaarung eines Thermoelementes zu errechnen, die nach ihm sortierten Metalle bilden die thermoelektrischen Spannungsreihe (Thermoelektrische Spannungsreihe gibt die Empfindlichkeit gegenüber Platin wider). Abbildung 10.10: Schaltzeichen und Signalflussplan eines Thermoelementes 68 Hinzugefügte Fragen Zuletzt bearbeitet von Christian Hartler Bipolartransistoren 1. Die Basisvorspannung für den Transistor BC 107 von UBE =0.62 V soll durch einen Vorwiderstand erzeugt werden. Die Betriebsspannung beträg UB = 10 V. Der Arbeitspunkt liegt bei UCE,A = 5V , ICE,A = 2mA, B=170. Berechnen Sie den Kollektorwiderstand und den Vorwiderstand. ICE,A = IC IB = IC /B = 0.0118mA UB = IC ∗ RC + UCE → RC = UB = IB ∗ R1 + UBE → R1 = UB −UCE IC UB −UBE IB = 2.5kΩ = 797.3kΩ 2. Eine Verstärkerschaltung wird ohne Emitterwiderstand jeoch mit einem Basisspannungsteiler betrieben. Der Transistor BC 107 hat die Daten im Arbeitspunkt: UCE,A = 5V, ICE,A = 2mA. Ferner gelte B=170 und UBE = 0.62V . Die Schaltung liegt an UB = 10V und Iq soll 5 ∗ IB sein. Berechnen Sie die Werte für RC , R1 und R2 69 Hier hatte ich das Problem, dass ich nur 3 Gl. mit 4 unbekannten Widerständen aufstellen konnte und glaube, dass die Angabe von RE oder UE fehlt: IB = IC B ≈ 0.012mA Iq = 5IB = 0.06mA I1 = IB + Iq = 0.072mA IE = 2.012mA GL1)IC RC + UCE + IE RE = UB → RC = GL2)I1 R1 + UBE + IE RE =→ R1 = GL3)I1 R1 + Iq Rq = UB =→ Rq = UB −UCE −IE RE IC UB −UBE −IE RE I1 UB −I1 R1 Iq = 2.5kΩ + 1.006RE = 130.28kΩ + 1.006RE = 166.67kΩ + 1.2R1 3. Berechnen Sie Rq und RV für die nebenstehende Schaltung unter den Annahmen: UCE = 5V, B = 100, UBE = 0.7V, Iq /IB = 10. 70 IC RC + UCE + (IC + IB )RE = UB 100IB RC + 101IB RE = UB − UC E IB = UB −UCE 100RC +101RE → IB = 0.05mA, IC = 5mA, Iq = 0.5mA IV = IB + Iq = 0.55mA IV RV + UBE + (IC + IB )RE = UB RV = UB −UBE −(IC +IB )RE IV = 16.89kΩ IV RV + Iq Rq = UB Rq = UB −IV RV Iq = 3.4kΩ 4. Gegeben ist die nebenstehende Verstärkerschaltung. Unter der Voraussetzung eines richtig eingestellten Arbeitspunktes beantworten Sie folgende Fragen: a Wie verändern sich IC und UCE , wenn RV vergrößert wird? b Wie verändern sich IC und UCE , wenn RE vergrößert wird? c Wie verändern sich IC und UCE , wenn RC vergrößert wird? 71 Frage b und c: GL1)IC RC + UCE + IE RE = UB → → UCE IC UCE IC = UB − RC − IE R IC E (IE /IC = IB +IC IC = 1/B + 1 = const) = UB − RC − const ∗ RE Frage a: GL2)IC RC + UCE + IE RE = UB GL2-GL1: IV RV − IC RC − UCE = 0 → RV IIVC − RC = ( IIVC = → UCE IC IB IC + Iq IC = const) = const ∗ RV − RC 72 UCE IC OPV 1. Bei einem Operationsverstärker wird die Ausgangsspannung über einen Widerstand R2 = 0.2M Ω auf den Eingang gegengekoppelt. Der Widerstand R1 hat einen Wert von R1 = 5kΩ. Wie groß ist die Ausgangsspannung, wenn an den Eingang eine Spannung von Uein = 1.5mV gelegt wird. Tja irgendwie fehlt bei der Angabe ob der OPV invertierend oder nicht-invertierend geschalten wurde, bei invertierend gilt: A = −R2 /R1 für die Verstärkung und für nicht invertierend: A = 1 + R2 /R1. Bei meinen Rechnung nahm ich bei allen Bsp. bei denen nicht dabeistand wie der OPV betrieben wird an, dass er nicht-invertierend geschalten wurde. A= Ua Ue =1+ → Ua = (1 + R2 R1 R2 )Ue R1 ≈ 61mV 2. Ein Operationsverstärker hat eine Transitfrequenz von 5 MHz. Welchen Wert muss der Gegenkopplungswiderstand R2 haben, wenn R1 = 5.6kΩ beträgt und eine Grenzfrequenz von 100 kHz gefordert wird? f0 ...Grenzfrequenz fg ...Bandbreite fg ≈ f0 ft ...Transitfrequenz V0 fg = ft Vorsicht V0 Verstärkung in dB! V0 = ft fg = 50dB Umrechnung von dB in einhotslose Verstärkung: V0 = 20log10 (A) V0 → A = 10 20 ≈ 316 A=1+ R2 R1 → R2 = (A − 1)R1 ≈ 1765.28kΩ 3. Ein Operationsverstärker hat laut Datenblatt folgende Werte: re = 20kΩ, ra = 1kΩ, V0 = 70dB. Er wird als nicht invertierender Verstärker betrieben, mit einem Eingangswiderstand R1 = 5kΩ. Der Ausgangswiderstand dieser Schaltung soll ra0 = 10Ω betragen. Berechnen Sie: • die Spannungsverstärkung, • den Gegenkopplungswiderstand, • den Eingangswiderstand der Schaltung 73 V0 = 20log10 (AD ) V0 → AD = 10 20 ≈ 3162.28 ra0 ≈ Ra AAD A = ra0 AraD ≈ 31.62 A=1+ R2 R1 R2 = (A − 1)R1 ≈ 158.1kΩ re0 = Ue Ie gG = re g+G /g << G re0 = re g = ra AAD = 20000kΩ 74 OPV-Anwendungen 1. Ein Operationsverstärker wird als Differenzverstärker wie folgt beschaltet: R2 = 100kΩ, R1 = 10kΩ, R3 = 68kΩ, R4 = 150kΩ. Die Eingangsspannungen betrage Ue1 = +0.6V, Ue2 = +0.8V . Wie groß ist die Ausgangsspannung. Ua = Ua1 + Ua2 2 Ua1 = −Ue1 R R1 Ua2 = Ue0 2 (1 + R2 R1 4 Ue0 2 = Ue2 R3R+R = Ue2 1+R14 /R3 4 → Ua ≈ 0.055V 2. Bei einem Differenzverstärker stehen die Beschaltungswiderstände in folgenden Verhältnissen zueinander: R1 /R5 = 1/5 und R3 /R4 = 1/5. Berechnen sie die Größe der Ausgangsspannun.g Es wurden leider die Spannungen vergessen dazuzuschreiben, hab die aus dem vorigen Bsp. entnommen, da diese Bsp. analog funktioniert. Ua = 1V (Formeln siehe vorheriges Bsp.) 3. Ein Operationssverstärker ist als Summierverstärker mit folgenden Widerständen beschaltet: R2 = 120kΩ, R11 = 10kΩ, R12 = 12kΩ, R13 = 20kΩ. Berechnen sie die Ausgangsspannung, wenn Ue1 = −3V, Ue2 = +0.5V, Ue3 = −2V betragen. 75 U Ua = −( Re111 + Ue 2 R12 + Ue 3 )R2 R13 = 43V 76 Kippschaltungen 1. Ermitteln Sie für die folgende Schaltung die Funktionsgleichung ABC = AB + C = (A ∧ B) ∨ C 2. Gegeben ist das logische Schaltnetz. Ermitteln sie die Wahrheitstabelle. A B C Z1 Z2 Z3 x 0 0 0 1 1 0 1 0 0 1 1 0 0 1 0 1 0 0 1 0 1 0 1 1 0 0 1 0 1 0 0 0 1 0 1 1 0 1 0 0 1 0 1 1 0 0 1 0 1 1 1 1 0 0 1 0 77