- SteuerregiSter (CR) Schreiben Sie für einen 8

Werbung

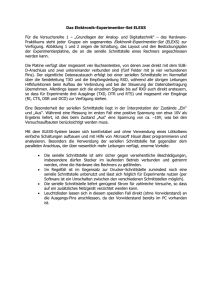

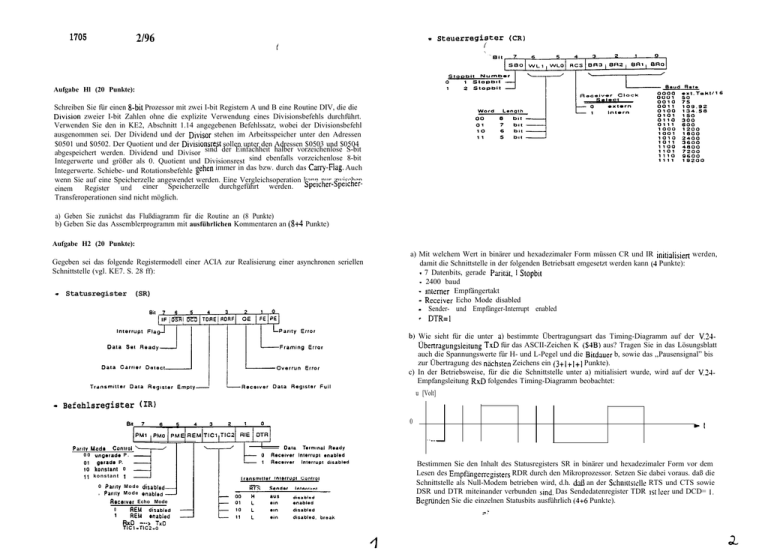

1705 2196 - SteuerregiSter (CR) f Aufgabe Hl (20 Punkte): Schreiben Sie für einen 8-bit Prozessor mit zwei I-bit Registern A und B eine Routine DIV, die die Dtvision zweier I-bit Zahlen ohne die explizite Verwendung eines Divisionsbefehls durchführt. Verwenden Sie den in KE2, Abschnitt 1.14 angegebenen Befehlssatz, wobei der Divisionsbefehl ausgenommen sei. Der Dividend und der Dtvisor stehen im Arbeitsspeicher unter den Adressen $0501 und $0502. Der Quotient und der Divtsionsrest sollen unter den Adressen $0503 und $0504 abgespeichert werden. Dividend und Divisor sind der Einfachheit halber vorzeichenlose S-bit Integerwerte und größer als 0. Quotient und Divisionsrest sind ebenfalls vorzeichenlose 8-bit immer in das bzw. durch das Carry-Flag. Auch Integerwerte. Schiebe- und Rotationsbefehle mehen 0 wenn Sie auf eine Speicherzelle angewendet werden. Eine Vergleichsoperation kann nur zwischen Register und einer Speicherzelle durchgeführt werden. Speicher-Speichereinem Transferoperationen sind nicht möglich. a) Geben Sie zunächst das Flußdiagramm für die Routine an (8 Punkte) b) Geben Sie das Assemblerprogramm mit ausführlichen Kommentaren an (8+4 Punkte) Aufgabe H2 (20 Punkte): Gegeben sei das folgende Registermodell einer ACIA zur Realisierung einer asynchronen seriellen Schnittstelle (vgl. KE7. S. 28 ff): - Statusregister (SR) a) Mit welchem Wert in binärer und hexadezimaler Form müssen CR und IR initialisiert werden, damit die Schnittstelle in der folgenden Betriebsatt emgesetzt werden kann (4 Punkte): - 7 Datenbits, gerade Paritat. 1 Stopbu - 2400 baud - Interner Empfängertakt - Receiver Echo Mode disabled - Sender- und Empfänger-Interrupt enabled - DTR=l b) Wie sieht für die unter a) bestimmte Übertragungsart das Timing-Diagramm auf der V.24Übertragungsleitung TxD für das ASCII-Zeichen K ($4B) aus? Tragen Sie in das Lösungsblatt auch die Spannungswerte für H- und L-Pegel und die Bitdauer b, sowie das ,,Pausensignal” bis zur Übertragung des nachsten Zeichens ein (3+l+l+l Punkte). c) In der Betriebsweise, für die die Schnittstelle unter a) mitialisiert wurde, wird auf der V.24 Empfangsleitung RxD folgendes Timing-Diagramm beobachtet: u [Volt] - Befehloregiater (IR) 0 ct . . .._ Par,ty Mods Conlrol 0 0 ungarade P . 01 ,O 1, gerada P. konalanl 0 konstant t 0 Parlty M o d e disibled , PUliy M o d e @nab,ed Recatver 0 1 Echo Mode REM difabled REM .“abled FIX0 ---> TxO TICl-TICz-o Bestimmen Sie den Inhalt des Statusregisters SR in binärer und hexadezimaler Form vor dem Lesen des Empfangerregisters RDR durch den Mikroprozessor. Setzen Sie dabei voraus. daß die Schnittstelle als Null-Modem betrieben wird, d.h. dah an der Schtnttstelle RTS und CTS sowie DSR und DTR miteinander verbunden sind. Das Sendedatenregister TDR ist leer und DCD= 1. Begninden Sie die einzelnen Statusbits ausführlich (4+6 Punkte). Aufgabe H3 (12 Punkte): i i Aufgabe H4 (20 Punkte): a) Gegeben sei die folgende BCD-Zahl im Format erner gepackten Gleitpunktdezimalzahl, wie sie in KE3, Abschnitt 1.1 beschrieben wurde: Gegeben sei ein 8bit-Mikroprozessor mit einem alkbyte großen Speicher und einem two-way set associative Cache mit zweimal 256 Einträgen. Der ZugrIff zum SpeIcher erfolgt durch die Assemblerbefehle: Z=90003000069531?5000000000 Die Belegung ‘00’ im Typfeld kennzeichne dabei jede gtiltige Zahl des darstellbaren Zahlenbereichs. Der Exponent beziehe sich auf die Basis IO. LDA n (n E (0000, .__, FFFFJ) Lade den Akkumulator A tmt dem Inhalt der Speicherzelle n. i) Wie lautet Z als Dezimalzahl? (1 Punkt) ii) Wandeln Sie diese Zahl in das folgende Format eines Arithmetikprozessor um, der nicht den einfach-genauen die folgenden verarbeite IEEE-754Standard untersttitzt. E r Glrltpunktzahlen: 311)I)II)I 23 i/Exponent E STA n (n E (0000, . . . . FFFF)) Speichere den Inhalt des Akkumulators A unter der Adresse n ab. Im Falle eine5 vvrite hit tindrt der Speicherzugriff im write through modus statt. Bei einem write rmss sei angenommen. da13 nur in den Arbeitsspeicher geschrieben wird. 0 122 ~ll~~l(llllllllllllIlI Mantisse M Es wird die LRU-Verdrungungsstrategie verwendet. Die Mantrsse M liegt dabei Immer in normalisierter Form 0,5 I M c 1 vor. Der Exponent E ist als vorzeichenbehaftete Zahl tm zer-Komplement zur Basis 2 gegeben (3 Punkte,. iii)Geben Sie die umgewandelte Zahl als Hexadezimalzahl an (1 Punkt). b) Gegeben sind die beiden folgenden Abschnitt 2.3 beschrieben wurden: Die aktuelle Speicherbelegung ist ausschnittsweise wie folgt: gepackten ganzen Dezimalzahlen, wie sie in KE3. und 9F3D Wie lautet das Produkt dieser betden Zahlen als gepackte ganze Dezimalzahl in hexadezimaler Darstellung, im Format der unter a) beschriebenen einfach-genauen Gleitpunktzahl (IEEE-754). als DezImalzahl und als gepackte Gleitpunktdezimalzahl in hexadezimaler Darstellung’? (7+2+1+2 Punkte1 14 0’2FA EB 92CD 9B 0122 53 9122 36 0027 82 Die Belegung des Cache zu Brgmn dss Beobuchtungsztrltraumb ibt ausschntttswclbe wi: 3D 74 c3 t 01 36 2F 86 BB t A.4 53 22 01 53 + 3D 82 folgt: Dabei zeigt der Pfetl des SB-Bits jeweils auf den Im nichsten ZugrIff eventuell LU verdrangenden Eintrag. Geben Sie für die Im LosungFhogen beschriebenen Sprlcherzu:ritic dn. ob ~‘ln hit oder ein miss vorliegt. Wie sieht die Belegung des Akkumulators und dcs Cache> nach dem lerztcn Spricherzugriti aus’> Welche Andeyngcn rrcten im SprIcher aui7 t5+1+10+4 Punkte) 3 Lidngsblatt Aufgabe H2: i i Aufgabe H5 (18 Punkte): a) Ein einfacher 8bit-Mikroprozessor mit 64 kbyte Memory-Adreßraum und 256 Byte YO-Adreßraum soll mit folgenden Speicher- und Peripherieanschlüssen ausgestattet werden. 32 kbyte EPROM ab Adresse SOOOO. 32 kbyte RAM 8 kbyte Video-RAM ab Adresse $8000. ab Adresse SEOOO. Interrupt-Controller a b A d r e s s e 920 Zihlerbaustein Timer 0 Out 0 verwendet Interrupt 7 a b A d r e s s e S30 b) u [Volt] t - Timer 1 Out 1 verwendet Interrupt 6 Serielle Schmttstelle I Serielle Schnittstelle 2 Parallele Schnittstelle ab Adresse SJO, Interrupt 3 a b A d r e s s e S50, I n t e r r u p t 3 ab Adresse $60, Interrupt 5 Um rme Überlappung der beiden RXMs zu verhmdem, muß der Xdreßdekoder die oberen 8 kbyte eines RAM-Bausteins ausblenden. Diese 8 kbyte des RAMs bleiben ungenutzt, damit Platz für das Video-RAM geschaffen wird. d verwendet werden können und die im L-Pegel aktiv sind. eingesetzt werden. Geben Sie die notwendigen Eingangssignale des PLA-Baustems an und die Boole’schen Gletchungen für die Funktton jedes Ausgangs. Benutzen Ste nur die Adreßlettungen, Überschneidung der Adreßberetche die für die Kodierung wirklich zu verhindern. (8+lO Punkter Aufgabe H6 (10 Punkte): Das folgende Bttmuster wird unter Verwendung der HDLC-Prozedur übertragen: o1lllIIoIoo1l~olo~oooooo~lIoIlolIloIoIoI oIoloI~lolIoloollIooloI1Io1IoooIoooool 00100~1/1110010110011011~011111010110011 0 0 i i i 0 I 0 0 Der HDLC-Rahmen enthalt Iobit-CRC-Prüfsumme. 0 0 1 ojo 0 0 I eine Sbtt-Zieladresse, Dir Daten reprisentieren I I I 0 010 0 I l ein Bbtt-Steuerfeld 1 I o i l l l l 10 mit Rahmennummer und eine 7blt-XSCII-Zeichen. Geben Sie die übertragene Zieladresse und die Rahmennummer als Hexadezimalzahl und die Daten als Zstcheniolge an. Die CRC-Pnifsumme ist nicht auszuwerten. (2+2+6 Punkte) - - -b - L b = Bitdauer Vervollsttindigen Sie die Verdrahtung der Bausteine. Benutzen Sie dazu das Lösungsblatt. Als Adreßdekoder soll ein PLA-Baustein mit 16 E/A-Anschlüssen, von denen maximal 8 als Ausgänge benotigt werden, um rme tl 0 c) = i Lösungsblatt Aufgabe H4: Lösungsblatt Aufgabe HS: Reihenfolge der Speicherzugriffe (bit bzw. miss bitte ankreuzen!): ADR RAM Cs r-7 ADR VIDEO-RAM Es ADR i5s S I O - 2 IRQ Akumulatorbelegungnach dem letzten Speicherzugriff: A = Cache-Belegung nach dem letzten SpeicherzugrIff: Way A Index Tag Datum SB-Bit Tag r-l ADR Cs so-1 Way B Datum I FA IRQ ADR 1 DE ADR CD Cs PI0 c c r IRQ - 7F r 3D 22 Anderurigen 1 ADR Cs 2F OUT1 OUT0 l l TIMER i m kbeitsspetcher: 7 8