Technische Universität Dresden Grundlagen der Technischen

Werbung

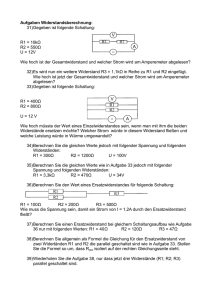

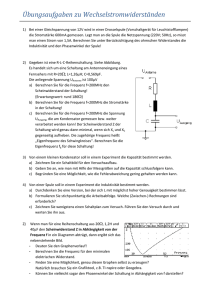

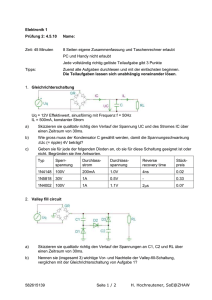

Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe ET_1 Bei Anschalten eines Widerstandes von 50 Ω an eine 4,5V-Batterie verringert sich die Klemmenspannung um 10%. Wie groß ist der Innenwiderstand der Batterie? Aufgabe ET_2 An einer Teilschaltung wurden die nachstehenden angegebenen Potentiale und Ströme gemessen: U4 U2 IC UE U1 IA R2 UB UA R4 UC U3 R1 U5 UF UD R3 IE ID R5 IF UA = 10 V, UB = 1 V, UC = -4,5 V, UD = 100 mV, UE = -4,5 V, IA = 10 mA, IF = 10 µA, R3 = 200 Ω, R4 = 5 kΩ, R5 = 2 kΩ Hinweis: Beachten Sie die vorgegebenen Zählrichtungen für Spannungen und Ströme. Die Ströme durch die Widerstände sollen prinzipiell immer in der gleichen Richtung positiv gezählt werden wie die Spannungsabfälle über den Widerständen. a) Was versteht man unter dem Begriff „Potential“? b) Beurteilen Sie, ob die angebenen Zählrichtungen für die Ströme in jedem Fall mit der tatsächlichen Stromflußrichtung übereinstimmen werden! c) Berechnen Sie die Spannungsabfälle über den Widerständen R1, R2, R3 und R4! d) Wie groß sind die Ströme durch die Widerstände R1, R2, R3, R4 und R5 ? Welchen Einfluß hat bei den angegebenen Werten R4 auf die Größe von IR4 ? e) Wie groß sind R1 und R2? f) Welche Werte ergeben sich für IC , ID und IE ? g) Wie groß ist das Potential UF ? h) Berechnen Sie die Leistung, die in R1 umgesetzt wird! Aufgabe ET_3 Gegeben sei die Reihen- , bzw. die Paralleschaltung zweier Widerstände Ra und Rb. a) Geben Sie allgemein die Größe des Gesamtwiderstandes für beide Fälle an ! b) Wie groß ist in beiden Fällen der Gesamtwiderstand, wenn b1) Ra = Rb b2) Ra = 0,001 Rb c) Charakerisieren Sie allgemein für Reihen- und Parallelschaltung von Widerständen das Verhältnis der Größe des Gesamtwiderstandes zu den Größen der Einzelwiderstände! ET - 1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe ET_4 Berechnen Sie in nachstehender Schaltung die Größe des Widerstandes R3! U1 I R1 U2 R2 I =20 mA U1 = 10 V R1 =1 kΩ R2 = 250 Ω U3 R3 Aufgabe ET_5 Berechnen Sie für die angebene Schaltung den Gesamtwiderstand an den Klemmen A-B ! R1 R5 A R7 R2 R6 R3 R8 R4 B R1 = 1 kΩ, R2 = 500 Ω, R3 = 100 kΩ, R4 = 1kΩ, R5 = 20 kΩ, R6 = 10 kΩ, R7 = 100 Ω, R8 = 50 kΩ Aufgabe ET_6 Eine Autoglühlampe (12 V, 60 W) wird in 10m Entfernung über ein entsprechend langes 2-adriges Kupferkabel (Querschnitt: 0,5 mm2, ρ = 0,0178 Ωmm2 /m) an eine 12 V - Spannungsquelle (Ri ≈ 0) angeschlossen. Welche tatsächliche Leistung wird in der Lampe umgesetzt? Aufgabe ET_7 A R3 R2 Ri UB B R1 UB = 10 V, Ri = 100 Ω, R1 = 500 Ω , R2 = 1 kΩ R3 = 200 Ω a) Tragen Sie in nebenstehender Schaltung für alle Ströme und Spannungen Zählrichtungen ein! b) Berechnen Sie allgemein den Gesamtwiderstand, mit dem die Spannungsquelle belastet ist! c) Wie groß ist für die Spannungsquelle die Leerlaufspannung UAB ? d) Auf welchen Wert sinkt UAB bei Belastung gemäß nebenstehender Schaltung ab? e) Welche Leistung wird in der gesamten Schaltung verbraucht? Welcher Anteil davon in den Lastwiderständen R1, R2 und R3 ? f) Berechnen Sie allgemein die Spannung über dem Widerstand R1 ! g) Wie groß ist der Strom durch den Widerstand R2 ? Welche Leistung wird in diesem Widerstand verbraucht? ET - 2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe ET_8 Wieviel Lastelemente RL können an den angegebenen Spannungsteiler angeschlossen werden, ohne daß die Ausgangsspannung den Bereich 4,2 V ≤ UA ≤ 5 V verläßt ? UB R1 = 10 kΩ R2 = 1 MΩ RL = 300 kΩ UB = 5 V R1 UA R2 RL RL Aufgabe ET_9 R R b 1 R 2 Ua U U e1 U e2 b In nebenstehender Schaltung werden zwei Spannungen Ue1 und Ue2, die eine gewisse Information verkörpern, mit einer konstanten Spannung Ub verknüpft. a) Berechnen Sie den Wert der resultierenden Spannung Ua ! b) Welchen Wert nimmt Ua an, wenn R1 << R2, Rb wird ? AufgabeET_10 Die Ladung einer 1,2 V - Knopfzelle beträgt 10 mAh. Wie groß müsste die Plattenfläche eines Plattenkondensators (Dielektrikum: Luft, d = 1 mm) sein, der bei 1,2 V die gleiche Ladungsmenge speichert? (ε0 = 0,885 10-11 As/Vm) Aufgabe ET_11 Gegeben sei die nachstehende Zusammenschaltung dreier Kondensatoren. C1 A C2 C3 UAB A C1 = 2 µF C2 = 6 µF C3 = 3,5 µF UAB = 2 V a) Berechnen Sie die Gesamtkapazität! b) Wie groß ist die Ladung des aus der Reihenschaltung C1 --- C2 gebildeten Kondensators? c) Welche Spannung stellt sich über dem Kondensator C1 ein? Hinweis: Überlegen Sie sich zunächst, wie groß die Ladung auf jedem der in Reihe geschalteten Kondensatoren sein muss. ET - 3 Technische Universität Dresden Institut für Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 1.1 Für die nebenstehende Schaltung sind folgende I Aufgaben zu lösen: a) Geben Sie I in Abhängigkeit von R2 UR1, Ub und R2 an! b) Stellen Sie diese Funktion in einem I - UR1 -Koordinatensystem dar. c) Stellen Sie IR1 = f(UR1) in dem gleichen UR1 Koordinatensystem dar. Ub d) Was beschreibt der Schnittpunkt der beiden R1 Funktionen? e) Welche Veränderungen ergeben sich bei ± R1, ± ∆UB sowie ± ∆R2? f) Bestimmen Sie graphisch die Werte von UR1, UR2 und I für UB = 5 V und R2 = 1 kΩ sowie R1 = 500 Ω, 1 kΩ, 2kΩ. g) Überprüfen Sie f) auf analytischem Weg. h) Ermitteln Sie graphisch den zulässigen Wertbereiche für R1, wenn die maximale Leistung am Widerstand R1 den Wert 4 mW nicht überschreiten darf ? (Zeichnen Sie sich dazu die Funktion IR1 = f(UR1) bei konstanten P = 4 mW ein.) i) Überprüfen Sie das Ergebnis aus h) durch Rechnung! Aufgabe 1.2. Gegeben ist die folgende Schaltung mit einem steuerbaren Widerstand (SR), bei dem mit dem Potential an der Klemme X die Größe des Widerstandes zwischen den Klemmen Y und Z gesteuert wird. steuerbarer Widerstand (SR): Ub IY R IY Uin X Y SR Z X Uout Y SR UYZ Z U XZ 2 IY = K U U XZ YZ a) Skizzieren Sie das IY - UYZ - Kennlinienfeld des steuerbaren Widerstandes! b) Leiten Sie allgemein die Spannungsübertragungskennlinie Uout = f(Uin) für die Schaltung her. c) Zeichnen Sie die Spannungsübertragungskennlinie für Ub = 5 V, R = 1 kΩ, K = 0,2 mA V -3 , Uin = 0...5 V d) Stellen Sie die Kennlinien für SR und für R im IY-Uout-Kennlinienfeld graphisch dar, und versuchen Sie die Spannungsübertragungskennlinie graphisch zu ermitteln, indem Sie eine zusätzliche 3. Achse für Uin einführen. WS2000 1-1 Technische Universität Dresden Institut für Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 1.3. -16 Es sei eine Diode gegeben mit IS = 10 A, UT = 26 mV und I = IS (exp U/UT -1). a) Skizzieren Sie den ungefähren Verlauf der Diodenkennlinie (Berechnung einiger charakteristischer Werte) b) Wie groß ist der statische und der dynamische Widerstand der Diode bei UD = 0,4 V; 0,6 V; 0,7 V; 0,8 V, 0,9 V. Machen Sie sich den Unterschied zwischen statischen und dynamischen Widerstand klar! Aufgabe 1.4. Für die gegebene Schaltung ist der Verlauf von uD(t), uR(t) und i(t) graphisch zu ermitteln! i(t) a) Die Quellspannung uQ(t) sei eine Gleichspannung mit dem Wert U0 = 2V. R uR(t) uQ(t) b) Die Quellspannung uQ sei eine Wechselspannung mit uQ(t) = U0 sin ωt , U0 = 2V R = 500Ω uD(t) Diodenkennlinie: U/V 0,6 0,7 0,8 0,85 0.9 I/mA 0 0,2 Hinweis: - Wenden Sie die Erkenntnisse aus Aufgabe 1.2. an - Maßstab: 5 mm entsprechen 0,1 V bzw. 0,2 mA. 0,6 1.4 3 Aufgabe 1.5. Gegeben seien die Diodenschaltungen A und B A I Rb ID UD1 Ub = 10V R b= 1 kΩ D 1 Ue1 Ue2 Ue3 D2 D3 Ub = 0V B ID Rb= 1 kΩ Ue1 Ua Ue2 Ua Ue3 mit Ue1 = 7 V, Ue2 = 5 V, Ue3 = 1 V, UF0 = 0,7 V, IS = 10 µA, Innenwiderstand der Spannungsquellen ≈ 0 a) Machen Sie sich die Funktion der beiden Schaltungen klar! In der Literatur sind für diese Schaltungen manchmal die Bezeichnungen Minimum- bzw. Maximumschaltung zu finden. Begründen Sie diese Bezeichnungen! b) Berechnen Sie für beide Schaltungen die Ausgangsspannung Ua, die Ströme durch die Dioden und durch den Widerstand Rb! Welche Spannungen liegen über den Dioden? WS2000 1-2 Technische Universität Dresden Institut für Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben I c) Welche logischen Funktionen werden durch die Schaltungen realisiert, wenn gelten soll: U(1) > U(0) (positive Logik), mit U(1) : 1-Pegel, U(0) : 0-Pegel D Hinweis: Bei der Lösung ist die idealisierte Diodenkennlinie zu Grunde zu legen. U F0 UD Aufgabe 1.6 Ub Rb U D1 Ub =5V, Ue1 =3V, Ue2 =2V, UF0 =0,8V, Ra = 5 kΩ, Rb = 1 kΩ, IS = 0 ideale Diodenkennlinie: ID D1 Ue1 Ue2 Ra D2 Ua UF0 UD a) Berechnen Sie für die angegebene Schaltungdie Werte von Ua, IRa, IRb, ID1, ID2 ! b) Welcher Wert ergibt sich für Ua, wenn Ra auf 1 kΩ absinkt? In welchem Zustand sind dann die Dioden? c) Auf welchen Wert darf Ra absinken, ohne daß beide Dioden sperren ? Aufgabe 1.7 U = 10 V b R Ue1 b ID ideale Dioden kennlinie: D1 Ra Ue10 UF0 UD D10 Welcher Wert kann für Rb minimal gewählt werden, wenn der Flußstrom durch eine Diode kleiner als 20 mA sein soll und weiterhin gilt: 0 V ≤ Uen ≤ 8 V, Ra ≥ 2 kΩ, IS = 50 µA , UF0 = 0,6 V ? WS2000 1-3 Technische Universität Dresden Institut für Technische Informatik Aufgabe 1.8 Grundlagen der Technischen Informatik Seminaraufgaben Ub ID ideale Dioden kennlinie: Rb Ue1 D1 R a UF0 Ca U =5V U = 0,8 V b F0 Ra = 5 k Ω U = 0,2 V e1 Rb= 1 kΩ U = 4,5 V e2 C a = 1 µF I = 0 S Ua Ue2 UD D2 a) Berechnen Sie im statischen Zustand Ua und den Strom durch die leitende Diode! b) Skizzieren Sie qualitativ den voraussichtlichen Verlauf von Ua , wenn Ue1 von 0,2V auf 3V springt c) Mit welcher Zeitkonstante wird dann Ca aufgeladen? d) Mit welcher Zeitkonstante erfolgt die Entladung bei Rücksprung von Ue1? e) Berechnen Sie die Aufladezeit tauf auf im Fall b)! (Schaltverhalten der Dioden, Diodenkapazitäten und Flußwiderstand sind zu vernachlässigen) Aufgabe 1.9. Gegeben ist die nachstehende, aus 2 spannungsgesteuerten Widerständen bestehende Schaltung. Ub = 5 V ue (t) R2 ue (t) u a(t) R1 ti C = 10 pF t T ti T Für die Widerstände gilt ue/V 0 5 R 1 /Ω ∞ 300 = 0,5 R 2 /Ω 600 ∞ a) Zeichnen Sie den ungefähren Verlauf der Ausgangsspannung ua(t), wenn am Eingang die angegebene Impulsfolge liegt a1) f = 5 Mhz a2) f = 25 MHz. b) Berechnen Sie die Größe der Energie, die bei einem Auflade - und einem Entladevorgang des Kondensators in der Schaltung umgesetzt wird ! WS2000 1-4 Technische Universität Dresden Institut für Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben c) Wie groß darf die Frequenz der Impulsfolge maximal sein, wenn die thermische Belastbarkeit der Schaltung maximal eine Verlustleistung von 2,5 mW zuläßt ? d) Wie verändert sich die Ausgangsimpulsfolge, wenn die Frequenz über 25 MHz ansteigt? e) Welche Wirkung hat ein Widerstand Ra parallel zum Kondensator? f) Skizzieren Sie den ungefähren Verlauf der Ausgangsspannung bei f = 25 MHz und Ra = 50 Ω. Hinweis: Zur näherungsweisen Ermittlung des Verlaufs der Ausgangsspannung brauchen Auflade- und Entladefunktionen nicht genau berechnet zu werden. Es genügt, den ungefähren Verlauf einer Exponentialfunktion zu kennen. -t/τ (Beispielsweise ist e bei t= 3τ bereits auf 5 % des Anfangswertes abgesunken.) Aufgabe 1.10 An nachstehende RC-Schaltung wird zum Zeitpunkt t = 0, die Spannung ue angelegt. ue (t) R 10 V C u (t) e ua (t) ti t T ti/T = ½, R = 1 kΩ, C = 1 µF, ua(t = 0) = 0, f = 500 Hz a) Berechnen Sie für die ersten beiden Perioden jeweils die minimale und maximale Spannung über der Kapazität und stellen Sie den Verlauf von ua (t) graphisch dar! (Anfangswert: Ua(t=0) = 0V ) b) Zeichnen Sie den ungefähren Verlauf von ua(t) im eingeschwungenem Zustand ! c) Welche mathematische Operation wird näherungsweise durch die Schaltung realisiert, wenn τ = CR >> T ist ? AUFGABE 1.11 a) Bestimmen Sie für die angegebene Schaltung den ungefähren Verlauf der Ausgangsspannung, wenn am Eingang die skizzierte Impulsfolge mit einer Frequenz von a1) 50 kHz und a2) 500 kHz vorliegt. b) Welche mathematische Operation wird näherungsweise durch die Schaltung realisiert, wenn τ = CR << T ist ? ue (t) C 10 V ue (t) R ua (t) ti ti/T = 0,5 , C = 1 nF, WS2000 R = 1 kΩ T t 1-5 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 2.1. Gegeben ist nachstehende Transistorstufe U CC R RB UCC BN UBE UBEF C = = = = 5V 100 0,7 V 0,7 V URC = 2,5V RC = 1 kΩ PTr.max= 200 mW T a) In welchem Zustand befindet sich der Transistor? b) Berechnen Sie den Arbeitspunkt (UCE, IC, IB) des Transistors und machen Sie sich seine Lage im IC - UCE - Kennlinienfeld klar! c) Wie groß muß RB sein, damit sich der oben ermittelte Arbeitspunkt einstellt ? d) Überprüfen Sie, ob die zulässige Verlustleistung des Transistors überschritten ist ! Aufgabe 2.2. UCC = 5 V, UBEX = 0,8 V UCEX = 0,1 V, BN = 100 RC = 100 Ω, RB = 800 Ω Restströme = 0 Bemerkung: Spanungen u. Ströme am übersteuerten Transistor werden mit dem Index „x“ gekennzeichnet, am gesperrten mit dem Index „y“. U CC RC S 1 RB T 2 In oben stehender Schaltung ist jeweils für Schalterstellung 1 und 2 zu ermitteln: a) Zustand des Transistors sowie Werte für UBE, UCE, IB, IC und gegebenenfalls Übersteuerungsgrad m , b) Lage der Arbeitspunkte im Ausgangskennlinienfeld (qualitativ). Aufgabe 2.3. Gegeben ist nachstehender Übersteuerungsschalter, der durch eine gleichartige Stufe angesteuert wird. ICX = 5 mA RB = 200 kΩ U CC IBX = 0,25 mA UCC = 10 V UCEX = 0,2V UBB = -10 V UBEX = 0,75 V RC BN = 50 RK Restströme = 0 T U E RB U WS2000 BB U A Berechnen Sie a) die Widerstände RC und RK , b) den Übersteuerungsgrad m , c) die Spannung UBEY . 2-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 2.4. Gegeben ist die nachstehende Schaltung eines NOR-Gatters mit den angegebenen Werten: R R = RC , U CC UE UCEX = 0,1V, UBEX = 0,75V 1 R mmin = 2, BN= 50, UCC= 10V RC UE .. 2 . UA Wie groß darf die Anzahl der Eingänge maximal werden, damit der Transistor bei UA= Ulow auch R im ungünstigsten Fall mit UE T n m ≥ mmin im Übersteuerungsbereich arbeitet? (Ansteuerung durch gleichartige Stufen vorausgesetzt). Aufgabe 2.5. Dimensionieren Sie den nachstehenden Übersteuerungsschalter unter Beachtung der angegebenen Bedingungen U OC UBEX = 0,7 V UCEX = 0,2 V RC BN = 50 Restströme = 0 UA UOC = 5V RB UE T (Ansteuerung erfolgt durch gleichartige Stufe) a) Berechnen Sie RC und RB, wenn ICX = 4,8 mA und m = 6 sein soll! b) Wie groß ist der high- und der low-Pegel am Ausgang für die unbelastete Stufe? c) Wieviel gleichartige Schaltstufen können maximal angeschlossen werden, wenn UAhigh ≥ 3,5 V sein soll? d) Berechnen Sie den Übersteuerungsgrad der nachfolgenden Stufen in Abhängigkeit von der Anzahl n der nachfolgenden Stufen! Wie groß ist m für n = 1 und für n = n max? Aufgabe 2.6. Gegeben sei nachstehende Übersteuerungsschaltstufe U OD U OC RC RB UE T RA UOC = 5 V UOD = 2,9 V UF = 0,6 V UBEX = 0,7 V U A CA = 0,1 µF UCEX = 0,1 V CA BN = 100 500 Ω ≤ RA ≤ 10 kΩ a) Welche Wirkung hat die am Kollektor angeschaltete Diode (RC = 150 Ω)? WS2000 2-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben b) Dimensionieren Sie RC so, daß im Fall RA = RAmax die maximale Flankenzeit am Ausgang tfl ≤ 12 µs ist! Verwenden Sie dabei die Näherungen: RC << RAmax, UCEX << UOC ! c) Wählen Sie RB so, daß bei Dimensionierung gemäß Aufgabe b) im Ruhezustand m ≥ 4 in jedem Fall gewährleistet ist! (Die Ansteuerung erfolge durch eine gleichartige Stufe, aber ohne Diode und RA.) d) Berechnen Sie den maximalen Strom durch die Diode! e) Wie verhält sich UAH bei verschiedenen Werten von RA innerhalb des vorgegeben Bereichs? Aufgabe 2.7. Bei UGS = 5 V fließt durch einen n-Kanal-MOS-Transistor vom Anreicherungstyp (ß=20 µA⋅V -2, Ut = 1,5 V)ein Drainstrom von 100 µA. a) In welchem Bereich wird der Transistor betrieben? b) Wie groß ist UDS? Aufgabe 2.8. Zwei MOS-Transistoren seien wie angegeben beschaltet. U tE D 0 D U tD 0 I I UDS UDS G G S S B A a) Berechnen Sie für die so entstandenen Zweipole die StromSpannungskennlinie und stellen Sie den Verlauf graphisch dar! b) Beide Zweipole werden wie nebenstehend gezeigt mit einem Widerstand R zu einem Spannungsteiler ergänzt. Ermitteln Sie die Größe von UR graphisch ! c) Welchen maximalen Wert kann UR in beiden Fällen bei Variation von R annehmen? d) Welcher der beiden Zweipole eignet sich in einem MOS-Inverter besser als Ersatz für den Lastwiderstand RD? U 0 U R R D U 0 UtE G 0 S RD D A G UtD 0 S WS2000 2-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 2.9. a) Berechnen Sie für einen ER-MOSFET-Schalter die Spannungsübertragungskennlinie UA = f(UE). U Hinweis 0D Führen Sie die Berechnung getrennt für RD die einzelnen Arbeitsbereiche des Transistors durch. U A UE b) Welche Größe muß der Widerstand RD haben, wenn für den Transistor das angegebene Layout vorgegeben ist und UA(L) ≤ 0,2 V bei UE = 5V sein soll (UOD = 5V, Ut=1V)? B L = 2,0 µm B = 2,3 µm ε ox ⋅ µ µA = 20 d ox V2 L Zusatzaufgabe Welche Länge müßte die Widerstandsbahn für den Widerstand RD auf Silizium haben, wenn bei einer Breite von 2 µm ein Widerstandswert von 75 Ω pro µm Länge auftritt? WS2000 2-4 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 3.1 Die dargestellte OV-Schaltung soll als 3-bit-Digital-Analog-Wandler gemäß angegebener Tabelle eingesetzt werden. (digitale Spannungspegel am Eingang: U(0) = 0V, U(1) = 1V) U3/V U2/V U1/V -UA/V 0 0 0 0 0 0 1 1 0 1 0 2 0 1 1 3 1 0 0 4 1 0 1 5 1 1 0 6 1 1 1 7 RN U R3 3 R2 R1 U2 U1 U A Wie sind R1, R2, R3 zu dimensionieren? Aufgabe 3.2 Ein OV wird, wie nachstehend gezeigt, gegengekoppelt: U C E 0,1V R U E U U A t1 t2 =50ms A - 0,5V t t ? a) Berechnen Sie allgemein UA = f(t)! ( UA(t=0) = 0 ) b) Skizzieren Sie für den angegebenen Verlauf von UE den Verlauf von UA und berechnen Sie die Größe von UA nach 50ms! ( R=10kΩ, C=1µF, UC(t=0)=0 ) Aufgabe 3.3 Ein OV wird, wie nachstehend gezeigt, gegengekoppelt: U R E Uo =0,1V C U E U A U A 10 20 t1 t2 50 t3 70 t4 t /ms t 3-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben a) Berechnen Sie allgemein UA = f(t) ! b) Skizzieren Sie für den angegebenen Verlauf von UE qualitativ den Verlauf von UA und berechnen Sie die entsprechnden Werte der Ausgangsspannung! ( R=10 kΩ, C=1 µF, UC(t=0) = 0 ) Aufgabe 3.4. R2 R1 UE 1 R3 UE 2 U UD A R4 a) Berechnen Sie UA = f ( UE1, UE2 ) b) Wie müssen die Widerstände gewählt werden, Subtraktionsschaltung gemäß der Formel UA = α ( UE2 - UE1 ) wirkt? damit die Schaltung als Aufgabe 3.5. UD U E R1 U A R2 a) Für die angegebene invertierende Schmitt-Trigger-Schaltung sind die Schaltschwellen UELH und UEHL zu berechnen. Hinweis: Der Schmitt-Trigger schaltet genau dann um, wenn zu einem kleinen ∆UE ein großes ∆UA gehört, das durch die Mitkopplung verstärkend auf den Eingang zurückwirkt, sodaß der OV schnell in die Sättigung gesteuert wird. Im Umschaltpunkt des Schmitt-Triggers gilt UD = UP - UN = 0. Aus der Berechnung von UD in Abhängigkeit von UE und UA kann so bei der Vorgabe von UA die Spannung UE für den Umschaltpunkt bestimmt werden. b) Zeichnen Sie die Übertragungskennlinie und berechnen Sie die Größe der Schalthysterese! c) Welchen Einfluß hat eine zusätzliche Diode in Reihe zu R1? 3-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 4.1. Der angegebene ED-Schalter hat bei UE = 5V eine Ausgangsspannung UA = 0,2V. Ermitteln Sie a) Arbeitsbereiche von TS und TL, b) Verhältnis Kanalbreite/ Kanallänge für den Schalttransistor (B/L)S, c) Größe der Kanallängen und Breiten von TL und TS, wenn die technologisch bedingte minimale Strukturgröße 1µm beträgt und für den ED-Schalter minimale Fläche gefordert ist. U0 TL A U0 = 5V UtS = 1V (εox µ dox )S = (εox µ dox )L UtL = -3V (B/L)L = 0,2 TS E Aufgabe 4.2. Die Transistoren eines CMOS-Inverters (Versorgungsspannung U0 =5V) haben folgende Eigenschaften: Ut/V ε ox ∗ µ B/µm L/µm d ox Tn 1 20 µA V-2 10 5 Tp -1,5 10 µA V-2 20 5 a) Bei welcher Eingangsspannung UE(SP) gilt UE = UA ? (SP: Schaltpunkt der Übergangskennlinie; im SP sind beide Transistoren im Abschnürbereich!) b) Wie ist das B/L - Verhältnis bei Tn zu verändern, damit UE(SP) = 0,5 U0 wird? c) Welchen Wert hat UE(SP) , wenn βn = βp und Utn = -Utp ist? Lösungshinweise: - Im Schaltpunkt SP arbeiten beide Transistoren im pinch-off-Bereich (siehe Vorlesung). - Beachten Sie beim Lösen der Gleichungen, daß a = ± a 2 ist, d.h. wählen Sie die technisch sinnvolle Lösung aus! 4-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 4.3. Gegeben ist die nachstehende NMOS-Schaltung. U U0 = 5 V 0 T Uts = 1 V, UtL = - 3 V L (εox µ dox )S = (εox µ dox )L (B / L)S = 2, A E E2 1 E3 UE = 0 V oder 5 V a) Welche logische Funktion erfüllt die Schaltung bei positiver Logik? b) Wie groß muß B/L des Lasttransistors gewählt werden, damit bei der ungünstigsten Eingangsbelegung UA(L) ≤ 0,3 V eingehalten wird? c) Berechnen Sie UA für UE1 = UE2 = UE3 = 5 V! Aufgabe 4.4. UB T L A E1 TS1 UA UE1 E2 TS2 UB UE1/2 UTS UTL βS βL = 5V = 0 V oder UB = 1V = -3V = 40 µAV-2 = 10 µAV-2 UE2 a) Berechnen Sie UA(L)! Hinweis: Nehmen Sie an, daß auf jeden Fall gilt UA(L) < 2 V. b) Durch welche Maßnahme kann erreicht werden, daß UA(L) verkleinert wird? c) Vergleichen Sie den zu erwartenden Flächenbedarf der Schaltstufe mit dem einer MOS-NOR-Schaltstufe (bei gleichen statischen Eigenschaften). 4-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe4.5. Welche logischen Verknüpfungen realisieren am Ausgang A die nachstehenden MOSLogikbausteine? UB UB T T L L A E1 E2 E4 E3 E5 A E1 E4 E7 E2 E5 E8 E3 E6 E9 (1) (2) Aufgabe 4.6. Gegeben ist nachstehende CMOS-Schaltung a) Welche logische Funktion realisiert die Schaltung an den Punkten B, C, D und A? b) Wozu dient CS? UB B C D E1 E2 A E3 CS 4-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 4.7. Gegeben ist die nachstehende Schaltung eines TTL-Gatters. U0 R1 R2 R4 U0 = 5 V, UCEX = 0,2 V, R1 T3 E1 T1 D T2 E2 T4 IE IA A UBEX = 0,8 V UBCX1 = 0,8 V R3 = 3,8 kΩ, R2 = 1 kΩ = 1,5 kΩ BN4 = 20, Restströme ≈ 0 Ausfächerung nmin = 1 R3 0 a) Berechnen Sie die Eingangsströme IE1 und IE2 für die Fälle α) UE1 = 3 V β) UE1 = 3,5 V UE2 = 0,2 V. UE2 = 3,5 V In welchen Betriebszuständen befinden sich in beiden Fällen die Transistoren T1 bis T4? b) Wie groß sind die Basisströme IBX2 und IBX4? c) Mit welcher maximalen Ausfächerung nmax darf das Gatter belastet werden, wenn 2 ≤ m4≤ 60 gelten soll? d) Welcher maximale Übersteuerungsgrad tritt bei T4 auf? Aufgabe 4.8. Bei einem TTL-NAND-Gatter mit 8 Eingängen werden nur 6 Eingänge benötigt. Welche Möglichkeiten bestehen zur Beschaltung der freien Eingänge? 4-4 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Seminaraufgaben Aufgabe 4.9. Gegeben sei ein TTL-Gatter mit offenem Kollektor a) Welche logische Funktion entsteht am Ausgang, wenn die Gatter wie skizziert zusammen geschaltet werden? b) Welcher Wert ist für RC maximal zulässig, wenn UA(H) ### 2,4 V sein soll und an A zwei nachfolgende TTL-Gatter mit IE(H) = 40 µA angeschaltet sind? (ICy = 0,25mA) UB=5V R1 R2 E1 UB T1 T2 A E2 T3 IE E1 E2 & E3 & R3 0 E6 R C A & Aufgabe 4.10. a) Untersuchen Sie die Funktion der beiden nachstehenden Schaltungen, insbesondere die Wirkung des Einganges EN. b) Charakterisieren Sie den Zustand der Ausgangsleitung, wenn EN = low ist und überlegen Sie, für welche Anwendungsfälle dieser Zustand bedeutsam ist! UB R1 EN R2 R4 UB D1 E1 T3 T1 T2 T4 E2 I E E D2 IA A A EN R3 0 4-5 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.1. Beweisen Sie, daß folgende Relationen gelten: X1 ∨ X1X2 = X1 X1 ∨ X 1X2 = X1 ∨ X2 Aufgabe 5.2. Gegeben seien die Ausdrücke Y1 = X1 ∨ X2X3 Y2 = (X1 ∨ X2) (X1 ∨ X3) a) Weisen Sie die Richtigkeit der Aussage Y1 = Y2 nach! b) Die angegebene logische Funktion soll nur mit AND- und OR-Gattern realisiert werden. Welcher der beiden Ausdrücke ist günstiger? c) Geben Sie die Schaltung an! d) Formen Sie die Funktion so um, daß eine minimale Realisierung nur mit NAND-Gattern bzw. nur mit NOR-Gattern möglich ist. Geben Sie die Schaltungen an! Aufgabe 5.3. Geben Sie für die Bool´sche Funktion gemäß nebenstehender Tabelle andere Darstellungsformen an : a) kanonische disjunktive Normalform a b c y b) kanonische konjunktive Normalform 0 0 0 1 c) Karnaugh-Tafel 0 0 1 1 d) minimale disjunktive Normalform 0 1 0 0 e) minimale konjunktive Normalform 0 1 1 1 f) geordnetes binäres Entscheidungsdiagramm (OBDD) für die Variablenordnungen a-b-c und c-b-a . 1 0 0 1 1 0 1 0 g) Entwickeln Sie die reduzierte Form für beide Entscheidungsbäume (ROBDD) 1 1 0 0 1 1 1 0 WS01/02 5-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.4. Unter einem Halbadder versteht man eine kombinatorische Schaltung, die nachstehende Schaltbelegungstabelle erfüllt. a b a 0 0 1 1 s c HA b 0 1 0 1 s 0 1 1 0 c 0 0 0 1 a) Ermitteln Sie die logische Funktion des HA, die bei der Realisierung mit NANDGattern einen minimalen Aufwand ermöglicht. Zeichnen Sie die Schaltung! b) Ermitteln Sie die logische Funktion für einen Volladder (siehe Tabelle), die zu einem möglichst minimalen Realisierungsaufwand mit NAND-Gattern führt. a i bi c i-1 s VA i ci Index i: i-te Stelle in einem mehrstelligen dualen Addierer Ci-1: einlaufender Übertrag der vorhergehenden Stelle ai 0 0 0 0 1 1 1 1 bi 0 0 1 1 0 0 1 1 ci-1 0 1 0 1 0 1 0 1 si 0 1 1 0 1 0 0 1 ci 0 0 0 1 0 1 1 1 c) Wie kann ein Volladder aus 2 Halbaddern gemäß Aufgabe a) aufgebaut werden? d) Zeichnen Sie die Schaltung, die den geringsten Aufwand erfordert ! Aufgabe 5.5. Für ein Haus mit 3 Etagen soll die Steuerung für die Treppenbeleuchtung entworfen werden. Dabei soll das Hauslicht in jeder Etage durch Umlegen eines Schalters ein- bzw. ausgeschaltet werden können, unabhängig von der aktuell vorliegenden Schalterstellung. Wenn alle 3 Schalter auf 0 stehen, soll das Licht nicht brennen. "1" 220 V x0 x1 x2 kombinatorische Schaltung Entwerfen Sie die kombinatorische Schaltung mit NAND-Gattern! WS01/02 5-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.6. Für die nachstehend gegebenen Schaltbelegungstabellen sind kombinatorische Schaltungen mit jeweils minimalen Gesamtaufwand an Gattern zu entwerfen. a) X3 X2 X1 X0 Y2 Y1 b) X3 X2 X1 X0 Y3 Y2 Y1 0 0 0 0 1 1 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 0 1 1 0 0 1 0 1 0 0 0 1 0 0 1 1 0 0 1 1 1 0 0 0 1 1 0 1 * 0 1 0 0 0 1 0 1 0 0 0 0 * 0 1 0 1 0 1 0 1 0 1 * 0 0 0 1 1 0 0 0 0 1 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 1 1 1 1 0 0 0 1 1 1 0 0 0 0 0 1 1 0 0 1 0 1 1 0 0 1 1 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 1 0 1 1 0 0 1 0 1 1 1 0 0 1 1 0 0 0 0 1 1 0 0 0 0 0 1 1 0 1 0 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 Hinweis: Achten Sie darauf, daß es nicht auf das Minimum der Einzelfunktion, sondern auf das Minimum für die Gesamtschaltung ankommt. Aufgabe 5.7. Gegeben ist die nachstehende Schaltung. Entwerfen Sie eine Schaltung mit gleichem logischen Klemmenverhalten und minimalen Aufwand. Zur Verfügung stehen nur NAND-Gatter mit 2 Eingängen. x3 x 2 x 1 x 0 1 1 1 & 1 & & >1 = y & & & WS01/02 5-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.8. Es ist eine Steuerlogik für eine Alarmanlage zu entwerfen, die Druck und Temperatur in einem Kessel überwacht. Signalgeber sind 2 Temperatursensoren (T1 und T2) sowie 2 Drucksensoren (P1 und P2), die folgende logische Pegel liefern: T1 = 1, wenn T ≥ 50 oC, sonst T1 = 0 o T2 = 1, wenn T ≥ 70 C, sonst T2 = 0 P1 = 1, wenn P ≥ 500 kPa, sonst P1 = 0 P2 = 1, wenn P ≥1000 kPa, sonst P2 = 0 Die Alarmanlage soll 4 Alarmstufen unterscheiden: A1, wenn mindestens 1 Sensor aktiv ist, A2, wenn mindestens 2 Sensoren aktiv sind, A3, wenn mindestens 3 Sensoren aktiv sind, A4, wenn mindestens 4 Sensoren aktiv sind. (Eine höhere Alarmstufe soll die niedere einschließen.) Bei technisch nicht sinnvollen Eingangsbelegungen soll ein Fehlersignal F = 1 ausgegeben werden. Da eine Auswertung der Alarmstufen bei Fehlersignal sinnlos ist, soll in diesem Fall die Belegung von A1 ... A4 ohne Interesse sein. F muß dann als allgemeines Alarmsignal gewertet werden. T 1 T 2 P1 P 2 kombinatorische Schaltung A1 A2 A3 A4 F Zur Verfügung stehen NAND-Gatter mit 2 Eingängen. Hinweis: Nutzen Sie die technisch nicht sinnvollen Eingangsbelegungen zur Schaltungsvereinfachung. Aufgabe 5.9. Über ein Förderband laufen in unregelmäßiger Folge Werkstücke der Länge 25 cm und 35 cm (Mindestabstand > 30 cm). An dem Förderband befinden sich in einem Abstand von jeweils 10 cm vier Lichtschranken. Bei Unterbrechung des Lichtstrahles liefert der zugehörige Ausgang "1". Entwerfen Sie eine kombinatorische Schaltung, die mit minimalen Aufwand eindeutig Werkstücke der Länge 25 cm und 35 cm erkennt (y25, y35)! WS01/02 5-4 Technische Universität Dresden Institut Technische Informatik 10 10 Grundlagen der Technischen Informatik Übungsaufgaben Förderband cm (Draufsicht) 10 30cm Aufnahmeelektronik x3 x2 x1 Laufrichtung x0 kombinator. Schaltung y 25 y35 Hinweise: - Untersuchen Sie die Signalfolgen X3...X0, die sich beim Durchlauf der Werkstücke ergeben. Welche Folgen bestimmen eindeutig die Werkstücke? - Nutzen Sie technisch unmögliche Eingangsbelegungen als don`t care-Bedingungen. - Auswertung ohne Berücksichtigung des Zeitverhaltens. Aufgabe 5.10 Zur Ansteuerung eines 7-Segment-Anzeigeelementes ist ein Codeumsetzer BCD- zu 7Segment-Code unter Verwendung von AND-OR- und NEG-Gattern zu entwerfen. x 0 20 x1 21 x2 22 x3 23 BCD 7-Segm.Code a b c d e f g a f g e b c d Zifferngestaltung: Der Entwurf ist auf einen minimalen Aufwand für die Gesamtschaltung (nicht Einzelfunktionen) auszurichten. WS01/02 5-5 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.11 Realisieren Sie die Schaltfunktion y=ab∨ ad ∨ abc ∨acd als Multiplexernetzwerk. a) Entwickeln Sie für die Funktion einen möglichst minimalen reduzierten binären Entscheidungsbaum (ROBDD). b) Geben Sie das entsprechende Multiplexernetzwerk an. Aufgabe 5.12 a) Ermitteln Sie für nachstehendes Multiplexernetzwerk die minimale disjunktive Normalform und die Wahrheitstabelle. b) Welche Operation erfüllt diese Schaltung, wenn a =(a1 a0 ) und b = (b1 b0 ) zwei zweistellige Dualzahlen darstellen? c) Vereinfachen Sie die gegebene Schaltung. Dabei sollen auch 4:1 - Multiplexer zur Verfügung stehen. 0 b0 1 MUX 0 2:1 1 MUX 0 2:1 0 a0 b1 1 1 MUX 0 2:1 1 MUX 0 2:1 0 b0 1 MUX 0 2:1 y a1 b1 a0 Aufgabe 5.13 Welche Funktion wird durch die nachstehende Multiplexer-Schaltung erfüllt? 0 1 WS01/02 3 2 1 0 MUX 4:1 Y G 0/3 1 0 A B 5-6 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 5.14 Realisieren Sie die durch die nebenstehende Funktionstabelle gegebene kombinatorische Schaltung mit möglichst geringem Schaltungsaufwand unter ausschließlicher Verwendung von a) 2 :1 – Multiplexern, b) NAND – Gattern mit maximal 2 Eingängen. Hinweis: Beachten Sie, dass bei beiden Realisierungsvarianten eine Vereinfachung durch die gegebenen Don´t-Cares ( * ) möglich ist. Beide Varianten müssen hinsichtlich der Nutzung der Don´t-Cares nicht übereinstimmen. WS01/02 a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 c 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 d 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 y * 0 1 1 1 0 * 1 * 1 0 1 1 1 * 0 5-7 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 6.1. a) Unter Verwendung eines Basis-Flipflop`s ist eine Schaltung zu entwerfen, mit deren Hilfe man auf einer im Normalfall ständig high-führenden Leitung einen low-Impuls nachweisen kann. b) Wie ist die Schaltung zu gestalten, wenn auf einer im Normalfall ständig low führenden Leitung ein high-Impuls nachzuweisen ist? Sehen Sie in beiden Fällen eine Rücksetzmöglichkeit vor! Aufgabe 6.2. Ermitteln Sie die Funktion nachstehender Schaltung, indem Sie die Wertetabelle aufstellen. G4 G6 1 1 1 G3 G5 R G1 C G7 1 1 Q 1 Q G8 1 D 1 G2 Aufgabe 6.3. Bei mechanischen Schaltern prellt die Konktaktzunge nach dem Umschalten mehrmals auf dem jeweiligen Schaltkontakt. a) Skizzieren Sie den zeitlichen Verlauf der Ausgangsspannung eines TTL-Gatters, das durch H inen solchen prellenden Schalter angesteuert (2) wird, 1 für einen low-high- und einen high-lowU (t) (1) a Umschaltvorgang. b) Entwerfen Sie unter Benutzung eines NAND/NAND-Flipflops eine Entprellschaltung, welche die Auswirkungen des Prellens auf die nachfolgende Signalleitung unterdrückt. Hinweis: Bei TTL-Gattern wirkt eine hochohmige Eingangsbelegung wie high-Potential Aufgabe 6.4. Gegeben sei die Schaltung eines Schmitt-Triggers mit CMOS-Gattern, die eine Übertragungskennlinie, wie nachstehend angegeben, besitzen sollen. IR 2 R1 UE IR 1 I UE G=0 UaG R2 1 1 UA Usp= 2,5V UeG (R1 = 400 Ω, R2 = 2,2 kΩ, U(L) = 0 V, U(H) = 5 V, USP ≈ ½ U(H) = 2,5 V) a) Wie groß ist UA, wenn UE = U(L) bzw. UE = U(H) ist (statisch)? b) Berechnen Sie näherungsweise die Schaltschwellen UE = UT+ (low-high-Sprung am Ausgang) und UE = UT- (high- low-Sprung am Ausgang) ! c) Berechnen Sie die Größe der Hysterese (allgemein und Zahlenwerte)! WS 04/05 6-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 6.5. Ein Bus B<2:0>, bestehend aus den Leitungen b2b1b0 wird in unregelmäßiger Folge mit den Dualzahlen (0...7) belegt. Nachstehende Schaltung soll anzeigen, wenn eine Zahl <5 vorgelegen hat. (2 2 21 2 0 ) b2 b1 b0 5V G5 111 G3 & L8 L5 G8 G1 & Y G6 & 1 G4 L6 & L7 G7 & & G2 Reset a) Machen Sie sich die Funktion der Schaltung klar. b) Untersuchen Sie, bei welcher Aufeinanderfolge von Zahlen eine Fehlanzeige am Ausgang Y infolge von Hazards auftreten kann, wenn pro Gatter eine Einheitsverzögerung TV = 1 vorliegt. c) Skizzieren Sie für die vorgegebene Signalfolge das Impulsdiagramm in folgender Form: B<2:0> 5 6 5 7 5 0 L5 L6 L7 L8 4 8 12 16 20 t/ T v Aufgabe 6.6. Gegeben sei nachfolgende Schaltung einer monostabilen Kippstufe (CMOS) UE G1 UC & C UG1 R G2 CMOS: Usp = U(H) / 2 & U R U A ∆U = U(H) - U(L) ≈ U(H) a) Welche Werte nehmen die Spannungen UR und UA im Ruhezustand an? (UE = U(H) und UE = U(L), jeweils konstant) b) Mit welcher Eingangsflanke ist die Schaltung zu triggern? c) Stellen Sie für einen Triggerzyklus die Verläufe der Spannungen UE, UG1, UR, UA und UC graphisch dar. d) Mit welchen Zeitkonstanten wird der Kondensator C umgeladen? WS 04/05 6-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben e) Berechnen Sie den Verlauf der Spannung UR! − t (Ansatz: U R = K1 + K 2 e τ ) f) Berechnen Sie die Haltezeit tH und die Dauer der Erholphase tE! (Es soll angenommen werden, daß bei |UR | = 0,05 ⋅ U(H) die Schaltung erneut getriggert werden kann, ohne daß eine wesentliche Verfälschung der Haltezeit eintritt.) g) Wie kann die Dauer der Erholphase verkürzt werden? h) Wie verändert sich der Verlauf von UR, wenn die Breite des Ansteuerimpulses größer als tH ist? Aufgabe 6.7. U 0D G1 C R 1 UE D G2 1 U U EG2 A Machen Sie sich die Funktion der Schaltung (CMOS) klar und stellen Sie die wesentlichen Unterschiede zur Schaltung Aufgabe 6.7. heraus (Ruhespannung, Triggerflanke, Verlauf der Eingangsspannung von Gatter G2)! Aufgabe 6.8. Gegeben sei folgende Schaltung (CMOS) 5V 5V Ds1 Ds2 A 1 UE (t) C 1 B 1 1 UM (t) Das Meßgerät soll den zeitlichen Mittelwert der anliegenden Spannung UM(t) anzeigen. T 1 U= U M ( t )dt T 0 a) In welche Teilschaltungen kann die angegebene Schaltung zerlegt werden? Erläutern Sie grob die Funktionsweise der Gesamtschaltung! Welche Aufgabe haben die Dioden DS1 und DS2? b) Skizzieren Sie qualitativ die Signalverläufe an den Punkten A, B, C und UM(t)! (UE(t) sinusförmig) c) Stellen Sie einen Zusammenhang zwischen der Frequenz der Eingangsspannung UE(t) und dem Anzeigewert des Instrumentes her! d) Wozu kann die Schaltung verwendet werden? WS 04/05 6-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 7.1. Nachstehende Schaltung ist zu analysieren! R A _ >1 C & 1 D 1 _1 > Q _ >1 Q C' 1 _ >1 1 S A a) Machen Sie sich die Teilschaltung zwischen C und C' klar! Skizzieren den Pegelverlauf am Punkt C', wenn am Eingang C eine impulsförmige Eingangsspannung liegt und alle Gatter die gleiche Verzögerungszeit haben. b) Wie wirken die Eingänge RA und SA ? Wie verhält sich die Schaltung, wenn RA= SA= 1 gesetzt wird? c) Welchen FF-Typ stellt die Gesamtschaltung dar? Charakterisieren Sie die Schaltung durch ein entsprechendes Schaltsymbol! d) Wie wirken sich Störspitzen am Eingang D auf den Ausgang Q aus? Wie ändert sich das Verhalten der Schaltung, wenn statt der Teilschaltung C - C' nur ein Negator steht? Aufgabe 7.2. Entwerfen Sie ausschließlich mit NOR-Gattern ein FF, das folgender Zustandstabelle genügt: CLKn 0 1 1 1 1 E1n * 0 0 1 1 E2n * 0 1 0 1 Qn+1 Qn Qn 0 1 Qn /Qn+1 /Qn /Qn 1 0 /Qn Aufgabe 7.3. Die Belegung auf einem 8 bit-Datenbus soll immer dann zur Anzeige gebracht werden, wenn die Leitungen s3, s2, s1, s0 eines Steuerbus die Belegung 1010 aufweisen. Die Anzeige erfolge über Lumineszenzdioden. Die Anzeige soll solange erhalten bleiben, bis sie über ein RESET-Signal zurückgestellt wird, bzw. bis sie durch ein erneutes Auftreten von 1010 auf dem Steuerbus aktualisiert wird. Entwerfen Sie die Schaltung unter Verwendung von NAND-Gattern und D-FF´s. WS 04/05 7-1 Technische Universität Dresden Institut Technische Informatik Steuerbus Grundlagen der Technischen Informatik Übungsaufgaben Datenbus 8 s3...s 0 4 Erkennungslogik Anzeige L 8 Anzeigespeicher 8 8 x 1 bit RESET Aufgabe 7.4. An den Eingängen des nebenstehenden JK-Master-Slave-FF mit asynchronen, low-aktiven Setz- und Rücksetzeingängen (wirken jeweils auf das Master- und auf das Slave-FF) liegt nachstehende Signalfolge an. Q S 1J C1 1K R Q Ermitteln Sie den entsprechenden Signalverlauf am Ausgang des Masters- und des SlaveFF! R S t J t K t C t Qm t Qs t t WS 04/05 7-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 7.5. Bestimmen Sie für die nachfolgende Schaltung mit JK-Master-Slave-FF bei vorgegebenen Signalen CLR und C die Verläufe von Q0, Q1und Q2 ! Q CLR 1 C H H S 1J C1 1K R Q 0 H 1 S 1J C1 1K R H H S 1J C1 1K R H Q 2 CLR t C t Aufgabe 7.6. Gegeben sei die nachstehende asynchrone Zählerschaltung a) Ermitteln sie die Impulsdiagramme an den Ausgängen Q0, Q1, Q2, wenn an X eine Rechteckimpulsfolge anliegt. (Anfangsstellung: Q1= Q2=Q3=0) b) Wie groß ist die maximale Zählfrequenz, wenn ein Flip Flop eine Schaltzeit von 20ns hat? c) Nach welcher Verzögerungszeit, gemessen von der Vorderflanke der Taktimpulse, liegt im ungünstigstem Fall ein gültiges Zählergebnis an, wenn die Frequenz der Zählimpulse 20 MHz beträgt (Tastverhältnis ti/T = 1:2) H X 1T C1 Q0 WS 04/05 1J C1 1K 1J C1 1K Q1 Q2 7-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 7.7. Gegeben sei ein integrierter Zählerbaustein modulo 16 gemäß nebenstehendem Schaltsymbol (DIN 40900, Teil 12) a) Machen Sie sich die Funktion des Bausteins klar! b) Ergänzen sie den Baustein durch eine externe Logik, so daß ein Vorwärts-Dezimalzähler entsteht. c) Wie muß der Baustein ergänzt werden, wenn der Zähler im Rückwärtsbetrieb nur den Zyklus 7, 6, ... 1, 0, 7, 6 durchlaufen soll. WS 04/05 RST TV TR PE D0 D1 D2 D3 CT=0 2+ G1 1G2 C3 3D CTRDIV16 1 CT=15 Co 2 CT = 0 Bo 0 1 2 3 Q0 Q1 Q2 Q3 7-4 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 8.1 Die nachstehenden Schaltungen (1) und (2) sind hinsichtlich ihrer Funktion zu analysieren. Ermitteln Sie jeweils a) die Ausgangs- und die Übergangsfunktion (Ansteuergleichungen für die FF-Eingänge), b) die Zustandsfolge- / Ausgabetabelle, c) den Zustandsgraphen. d) Stellen Sie für die Schaltung ein Impulsdiagramm auf! (Anfangzustand: A1 = A2 = A3 = 0) (1) & E ≥1 1 & ≥1 & ≥1 A 0 1J C1 FF1 1K A1 1J C1 FF2 1K A2 1J C1 1K A3 FF3 (2) E & & ≥1 & & & A0 1J C1 1K FF1 A1 1J C1 1K FF2 A2 1J C1 1K FF3 A3 C WS04/05 8-1 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 8.2 Entwerfen einen Dualzähler modulo 3 (Zählfolge: 0→1→2→0→1→ ... ), der beim Übergang von 2 nach 0 einen Übertragsimpuls abgibt. Der Zähler soll über eine high-aktive RESETLeitung synchron (das heißt, mit dem nächsten Zählimpuls) auf 0 rückstellbar sein. Für den Aufbau stehen JK-FF, die keinen eigenen Rücksetzeingang besitzen, zur Verfügung. Achten Sie auf minimalen Schaltungsaufwand! a) Zustandsgraph b) Zustandsfolge- / Ausgabetabelle c) Ansteuergleichungen für die FF-Eingänge d) Schaltung Aufgabe 8.3. Eine Impulsfolge ist im Verhältnis 1:10 zu untersetzen. Entwerfen Sie die Schaltung unter Verwendung von JK-FF´s, die einen asynchronen RESET-Eingang besitzen sollen. Achten Sie auf minimalen Schaltungsaufwand. Aufgabe 8.4. Entwerfen Sie unter Verwendung von taktflankengesteuerten RS-FF´s einen 2 bit-Vor/Rückwärts-Dualzähler (Eingangsleitung V=1: Vorwärtszählen, V=0: Rückwärtszählen). Beim Übergang von 3 nach 0 und von 0 nach 3 soll ein Übertragsimpuls ausgegeben werden. Die RS-FF´s sollen über asynchrone RESET-Eingänge verfügen. Achten Sie auf minimalen Bauelementeaufwand. Aufgabe 8.5. Ein Fahrzeug, das über 4 Geschwindigkeitsstufen (einschließlich v=0) verfügt, soll über zwei Tasten B und V beschleunigt bzw. verzögert werden können. Dabei soll sich bei Betätigung der Taste B jeweils die nächst höhere, bzw. bei Betätigung von V jeweils die nächst niedrigere Geschwindigkeitsstufe einstellen. S1 S0 Stufe Die einzelnen Geschwindigkeitsstufen sind über 0 0 v0 (Stopp) 2 Steuerleitungen S0 und S1 gemäß nebenstehender 0 1 v1 (langsam) Kodierung am Fahrzeug einstellbar. 1 0 v2 (mittel) Eine Betätigung der Beschleunigungstaste B bleibt ohne 1 1 v3 (schnell) Wirkung, wenn sich das Fahrzeug bereits in der Stufe "schnell" befindet. Gleiches gilt für die Verzögerungstaste bei bereits stehenden Fahrzeug. Wenn keine oder beide Tasten gedrückt sind, dann soll das Fahrzeug in der jeweiligen Geschwindigkeitsstufe verharren. Entwerfen Sie ein synchrones Schaltwerk zur Ansteuerung der beiden Steuerleitungen S0 und S1 unter Benutzung von JK-Master-Slave-FF´s mit minimalem Bausteinaufwand. Das Schaltwerk wird mit einem Takt versorgt, dessen Frequenz genügend klein ist, um ein zu schnelles Durchlaufen der Geschwindigkeitsstufen zu verhindern. B V Takt WS04/05 Schaltwerk S0 S1 Fahrzeug 8-2 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 8.6 Eine Maschine, die zur Herstellung eines Produktes drei Arbeitsgänge benötigt, soll mit Hilfe eines Steuerautomaten (siehe Prinzipskizze) automatisiert werden. ZE _1 > START S H F Steuerautomat M1 M2 M3 Produkt.maschine H Taktgeber - Die Ansteuerung der Produktionsmaschine erfolgt über 3 Ansteuerleitungen M1, M2 und M3, auf denen nur 4 Signalbelegungen technisch sinnvoll eingesetzt werden (siehe Tabelle). Befehl Ruhe 1. Arbeitsg. 2. Arbeitsg. 3. Arbeitsg. M1 0 1 0 0 M2 0 1 1 0 M3 0 1 1 1 - Die Signale auf M1, M2 und M3 müssen solange erhalten bleiben, bis die Produktionsmaschine durch ein high-aktives Fertigsignal F zu erkennen gibt, daß ein Arbeitsgang beendet ist und der nächste begonnen werden kann. F wird zurückgesetzt, sobald die Maschine einen neuen Arbeitsgang beginnt. - Bei Störungen gibt die Produktionsmaschine ein Havariesignal H ab. In diesem Fall muß die Maschine sofort in den Ruhezustand zurück gehen. - Jedes Mal, wenn die Maschine in den Ruhezustand zurückkehrt (auch bei Havarie), soll der Steuerautomat ein Zyklusendesignal ZE abgeben. - Nach dem letzten Arbeitsgang soll die Maschine solange im Ruhezustand verbleiben, bis durch einen Startimpuls ein neuer Arbeitszyklus begonnen wird. - Der Steuerautomat soll durch einen Taktgeber getaktet werden, dessen Periodendauer sehr viel größer ist als die Reaktionszeit, mit der die Ausgangssignale der Produktionsmaschine geschaltet werden. a) Entwerfen Sie den Steuerautomat mit JK-Master-Slave-FF´s und NAND-Gattern, wobei auf minimalen Aufwand zu achten ist. b) Wie könnte verhindert werden, daß bei zu langem START-Impuls der 1. Arbeitsgang übersprungen wird? WS04/05 8-3 Technische Universität Dresden Institut Technische Informatik Grundlagen der Technischen Informatik Übungsaufgaben Aufgabe 8.7 Zur Analyse eines taktsynchronen Bitstromes auf einer Leitung x sollen durch einen Sequenzdetektor Sequenzen von jeweils genau drei aufeinanderfolgenden „1“ erkannt werden. Eine solche Sequenz ist durch den Wert „1“ auf der Ausgangsleitung y des Detektors anzuzeigen. Bei mehr als drei aufeinanderfolgenden Einsen, wird jede dritte „1“ angezeigt. Eine besondere RESET-Leitung zur Einstellung eines Anfangszustandes, z.B. über spezielle Rückstelleingänge der einzelnen FF, kann vorausgesetzt werden. Bitstrom Takt RESET x T Sequenzdetektor y Beispiel: x: 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 0 1 1 0 1 0 y: 0 0 0 1 0 0 0 1 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 Entwerfen Sie die Schaltung für den Sequenzdetektor mit T-FF (2-Zustands-gesteuert)! a) Zustandsgraph b) Zustandsfolge- /Ausgabetabelle (Realisierung als Mealy-Automat) c) Ansteuergleichungen für die FF-Eingänge und Ausgang y (Achten Sie auf minimalen Aufwand für die Schaltung!) d) Schaltung WS04/05 8-4