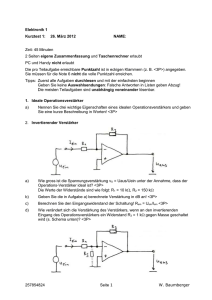

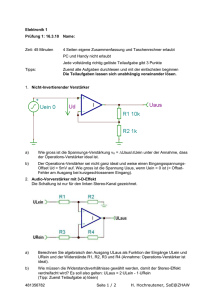

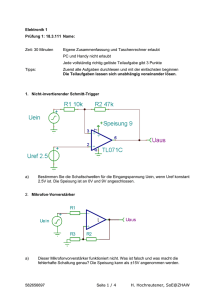

Physik-Institut - Universität Zürich

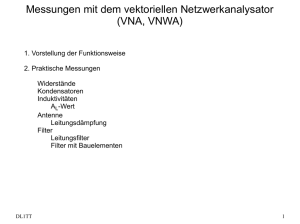

Werbung