Überblick über ESD

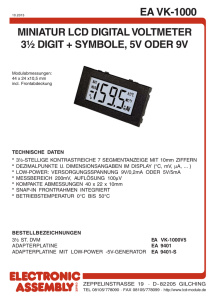

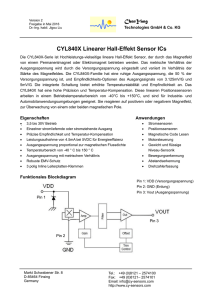

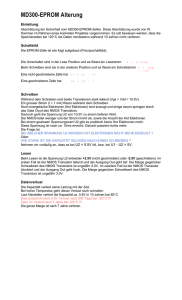

Werbung

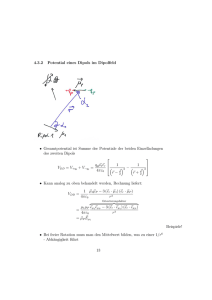

Überblick über ESD-Schutzstrukturen VDD Mp IESD 0V +V IESD IESD Primary ESD Clamp IESD Internal circuits R Input Pad NMOS Secondary ESD Clamp Mn Input Circuit Roland Pfeiffer 19. Vorlesung VSS Problemstellung statische Aufladung von Menschen und Maschinenteilen, Entladung über IC oder statische Aufladung von IC, Entladung über Menschen und Maschinenteilen Electric Static Discharge (ESD) Mp Interne Schaltung VDD Mn VSS Input Circuit MOS-Schaltungen: ESD-Schutz von Gate-Oxid Problemstellung „Human Body Model (HBM)“ 400 [mA] Modellierung ESD-Test: 600 Anstiegszeit ≤ 10ns 200 0 -100 -100 0 100 200 [ns] 10 [mA] „Machine Model (MM)“ 5 Anstiegszeit ≤ 10ns 0 -5 -10 -100 0 100 200 [ns] „Charged Device Model (CDM)“ [mA] 20 Anstiegszeit ≤ 200ps 10 0 -5 0 2,5 [ns] 5 Problemstellung ESD-Test: jeweils RC-Kreise, die zur Nachbildung eines menschlichen Körpers bzw. eines metallischen Maschinenteils bzw. des IC dienen RV R DUT Hochspannungquelle VESD RV R C C HBM: MM: 1 MΩ 1 MΩ 1,5 kΩ 100 Ω 100 pF 200 pF CDM: >10 MΩ 0Ω CBauelement Device Under Test Problemstellung VESD ESD-Test: +V Erklärung der Namen: 0V (1) PS-mode: Positive Spannung zwischen Pin und VSS-Anschluß (2) NS-mode: Negative Spannung zwischen Pin und VSS-Anschluß (3) PD-mode: VESD Positive Spannung zwischen +V 0V Pin und VDD-Anschluß (4) ND-mode: Negative Spannung zwischen Pin und VDD-Anschluß (2) NS-mode (1) PS-mode VESD VDD VDD 0V -V + VSS VSS (4) ND-mode (3) PD-mode VESD VDD VDD 0V -V VSS VSS Problemstellung ESD-Test bei analogen Schaltungen (z.Bsp. Operationsverstärker): (2) Negative-mode (1) Positive-mode VESD +V VESD VDD VDD 0V 0V -V OP + VSS OP + VSS Problemstellung Auswirkungen des ESD-Test bei analogen Schaltungen bei keiner ESD-Schutzstruktur: VDD VESD +V 0V Vo IESD Vin Vin Pad Pad IESD Vbias VSS IESD Prinzip der ESD-Schutzstrukturen Konventielle zweistufige ESD-Schutzstruktur bei PS,NS: Hauptlast: erste ESD-Schutzstruktur über Widerstand zweite ESD-Schutzstruktur „gate-grounded NMOS“ gate-grounded NMOS (ggNMOS) Input Pad R IESD IESD Erster ESD Schutz +V IESD Interne Schaltung Mp IESD 0V VDD Mn NMOS Zweiter ESD Schutz Input Circuit VSS bei PD,ND: komplementäre zweistufige Verbindung mit VDD Prinzip der ESD-Schutzstrukturen Konventielle zweistufige ESD-Schutzstruktur: Problem bei Hochfrequenz-Schaltungen: RC-Zeitkonstante !! Sperrschicht-C VDD R≈ kΩ Input Pad 0V Mp R IESD IESD Erster ESD Schutz +V IESD Interne Schaltung IESD Mn NMOS Zweiter ESD Schutz Input Circuit gate-grounded NMOS (ggNMOS) VSS ESD-Schutzstrukturen Untersuchung der HF-ESD-Schutzstruktur: Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 DWanne p-Substrat Dp1 p+ n+ n-Wanne ESD-Schutzstrukturen PS-Test: VESD +V (1) PS-mode VDD 0V + VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 Dp1 p+ n+ n-Wanne DWanne p-Substrat Diode n+-Draingebiet/p-Substrat in Sperrrichtung, NMOS-Transistor belastet ⇒ Drain-Breakdown !! ⇒ maximale ESD-Spannung begrenzt ESD-Schutzstrukturen NS-Test: VESD 0V (2) NS-mode VDD +V + VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 Dp1 p+ n+ n-Wanne DWanne p-Substrat Diode n+-Draingebiet/p-Substrat Dn1 in Durchlassrichtung, NMOS Transistor unbelastet ⇒ maximale ESD-Spannung bedeutend höher als PS ESD-Schutzstrukturen (4) ND-mode VESD VDD ND-Test: 0V -V VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 Dp1 p+ n+ n-Wanne DWanne p-Substrat Diode p+-Draingebiet/n-Wanne in Sperrrichtung, PMOS-Transistor belastet ⇒ Drain-Breakdown !! ⇒ maximale ESD-Spannung begrenzt ESD-Schutzstrukturen VESD PD-Test: (3) PD-mode VDD +V 0V VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 p+ n+ Dp1 n-Wanne DWanne p-Substrat Diode p+-Draingebiet/n-Wanne Dp1 in Durchlassrichtung, PMOS Transistor unbelastet ⇒ maximale ESD-Spannung bedeutend höher als ND ESD-Schutzstrukturen PS-Test: VESD +V (1) PS-mode VDD 0V + VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ p+ n+ Dn1 Dp1 n-Wanne DWanne p-Substrat Idee: bei PS-Test: n-Wanne positiv aufgeladen über Dp1 ⇒ Ableitung zu VSS möglich ?? ESD-Schutzstrukturen (4) ND-mode VESD VDD ND-Test: 0V -V VSS Input Pad gate-grounded NMOS gate-grounded PMOS VSS VDD p+ n+ p+ n+ Dn1 Dp1 p+ n+ n-Wanne DWanne p-Substrat Idee: bei ND-Test: p-Substrat negativ aufgeladen über Dn1 ⇒ Ableitung zu VDD möglich ?? ESD-Schutzstrukturen Schaltung Analog ESD Protection Circuid Mp2 VG VX Rp1 R VDD Mp1 Dp1 PAD AMP C Mn3 Mn2 Rn1 Mn1 Dn1 Analog Circuits VSS Vorteil: Mn3 (W/L groß) belastet nicht Input-Pad !! ESD-Schutzstrukturen VESD Volt ~ ~ VG(t) Schaltung: Vth Analog ESD Protection Circuid 0 ton Time VDD Mp2 VG VX Rp1 R Mp1 Dp1 PAD AMP C Mn3 Mn2 Rn1 Mn1 Dn1 Analog Circuits VSS ESD-Streß: über Mn3 (W/L groß) gesteuert über Inverter und RC-Glied wird eine Verbindung VDD-VSS geschaffen Volt ESD-Schutzstrukturen ~ ~ VDD Power-on Schaltung: Vth Analog ESD Protection Circuid VG(t) 0 1mS Time VDD Mp2 VG VX Rp1 R Mp1 Dp1 PAD AMP C Mn3 Mn2 Rn1 Mn1 Dn1 Analog Circuits VSS Normalbetrieb: RC-Glied wird aufgeladen, über Mn2 wird die Spannung VG auf ≈ 0 Volt gesetzt, bevor über Mn3 Leistung verlorengeht ESD-Schutzstrukturen Vorteil: Mn3 (W/L groß) belastet nicht Input-Pad !! Mp2 VG VX Rp1 R Mp1 Dp1 PAD AMP C Mn3 Mn2 Analog ESD Protection Circuid Resultat der Messung: Rn1 VDD Mn1 Dn1 Analog Circuits VSS ESD-Schutzstrukturen nur ein Beispiel von Vielzahl von Veröffentlichung zum Thema „ESD-Schutz bei Hochfrequenz-Schaltungen“ ESD-Schutzstrukturen Bei höheren Frequenzen (ca. ab 5 GHz): „Human Body Model (HBM)“ [mA] Anstiegszeit ≤ 10ns ω0 400 ⇒ 200 0 -100 -100 Fourier 0 100 200 [ns] t 1 5 GHz f Tiefpass als ESDSchutz ESD-Schutzstrukturen Beispiel LNA mit Tiefpässen am Eingang und am Ausgang: VDD Vbais MESD CDEC LLoad R M2 RFIN CC LESD C1 RFOUT M1 Lg LS C2 LESD ESD-Schutzstrukturen Beispiel LNA mit Tiefpass am Eingang (Ausgang nicht betrachtet): RS Betrachtung bei ω0 ω0 LESD VS Resonanz ω0 RS 5 GHz VS Rg RFIN M1 CC Cpad +Cpar RESD @ω0 RFIN Rp,ESD RP , ESD = LS R‘S R‘S = 50 Ω ω0 2 ⋅ LESD 2 Bedingung: RP,ESD >> R‘S RESD RP,ESD ≈ kΩ !! ESD-Schutzstrukturen Beispiel LNA mit Tiefpass am Eingang (Ausgang nicht betrachtet): ESD-Betrachtung 1 GHz ⇒ [mA] RS 400 VS 200 0 -100 -100 LESD RESD 0 100 200 [ns] Rg RFIN CC Cpad +Cpar M1 LS Zusammenfassung Problemstellung Prinzip der ESD-Schaltung Zusammenfassung Literaturhinweise Literaturhinweise Artikel: -M.-D. Ker, „Whole-Chip ESD Protection Design with Efficient VDD-to-VSS ESD Clamp Circuits for Submicron CMOS VLSI“ Transaction on Electron Devices, Januar 1999 -M.-D. Ker et al., „ESD Protection Design on Analog Pin with Very Low Input Capacitance for High-Frequency or Current-Mode Applications“, Journal of Solid-State Circuits, August 2000 -D. Linten et al., „A 5-GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 90-nm RF CMOS“, Journal of Solid-State Circuits, July 2005