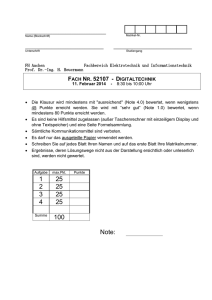

1 26 2 24 3 20 4 20 5 20 6 20 7 20 150 Note

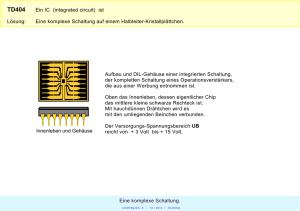

Werbung

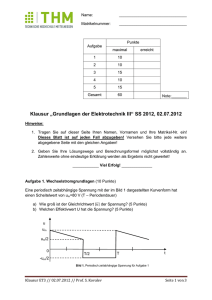

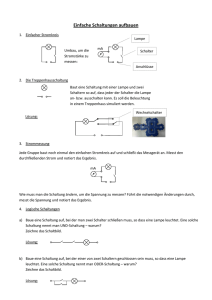

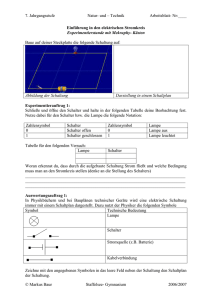

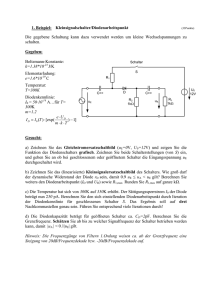

__________________________________ Name (Blockschrift) Matrikel-Nr. _________________________________ Informatik Unterschrift Studiengang Fachhochschule Aachen Prof. Dr.-Ing. F. Wosnitza Fachbereich Elektrotechnik und Informationstechnik Prof. Dr.-Ing. H. Heuermann 5522 - DIGITALTECHNIK UND TECHNISCHE INFORMATIK Mo., 10. Juli 2006 - 8:30 bis 11:30 Uhr Es sind keine Hilfsmittel zugelassen (außer Taschenrechner mit einzeiligem Display und ohne Textspeicher). Ein Blatt ist als Formelsammlung für den DT-Teil zugelassen. Sämtliche Kommunikationsmittel sind verboten. Es darf nur das ausgeteilte Papier verwendet werden. Schreiben Sie auf jedes Blatt Ihren Namen und Ihre Matrikelnummer. Ergebnisse, deren Lösungswege nicht aus der Darstellung ersichtlich sind oder die unleserlich sind, werden nicht gewertet. Aufgabe max.Pkt. 1 2 3 4 5 6 7 26 24 20 20 20 20 20 Summe 150 Punkte Note: DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 9 ------------------------------------------------------------------------ Aufg. 4 (20 Punkte) Bei modernen digitalen Schaltungen sorgen Auf- und Entladeströme von parasitären Kapazitäten dafür, dass die logische Funktionalität erst verzögert durchgeführt wird. Durch die Verwendung von „Clock“-Signalen eliminiert bzw. minimiert man diese Laufzeiteffekte. Die Gatter der im Folgenden untersuchten Schaltungen haben eine Verzögerungszeit von jeweils 5ns. D.h. 5ns nachdem sich die Eingangssignale (einschließlich dem Clock-Signal) geändert haben, erfolgt eine Umschaltung. Die Eingänge A und B sowie das Clock-Signal C und die Startwerte der Ausgänge P’ und P’’ bzw. der Ausgänge Q’ und Q’’ sind gegeben. Für die im Folgenden angegebenen Digitalschaltungen soll das Schaltverhalten zunächst als nicht getaktete Schaltung dargestellt werden. A 1 1 1 B Die zweite Digitalschaltungen mit zusätzlichen Gattern zur Realisierung der getakteten Schaltung (Umschaltung bei „Clock“-Signal=“High“) ist im folgenden Bild dargestellt. A & X 1 P" C 1 & 1 B Y Q" a) Wie heißen diese Schaltungen? b) Tragen Sie das Schaltverhalten über der Zeit für B, P’ und Q’ im Falle einer asynchronen Schaltungsrealisierung ohne Clock-Signal ein. c) Tragen Sie das Schaltverhalten über der Zeit für B, X, Y, P’’ und Q’’ im Falle einer synchronen Schaltungsrealisierung mit Clock-Signal C ein. d) Welche Clock-Frequenz hat die Schaltung? e) Welche maximale Frequenz kann an den Ausgang Q’’ auftreten? DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 10 -----------------------------------------------------------------------Zu Aufg. 4 b): A 0 20 40 60 80 100 t/ns t B P’ t t Q’ t DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 11 -----------------------------------------------------------------------Zu Aufg. 4 c): C A 0 20 40 60 80 100 t/ns t B X t t Y P’’ t Q’’ t t DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 12 ------------------------------------------------------------------------ Aufg. 5 (20 Punkte) Das elektrische Ersatzschaltbild eines MOS-Transistors besteht im einfachsten Fall aus einem idealer Schalter Si (i=1,2,3,4) und einem Serienwiderstand R. Eine Logikschaltung mit den Eingängen US und den invertierten Eingängen zu US und dem Ausgang UA wird mit der Versorgungsspannung Vcc=5V betrieben. Die Schaltung ist aus Widerständen und spannungsgesteuerten Schaltern aufgebaut. Der Ausgang wird mit RA belastet. Die Schalter S1 bis S4 haben einen Serienwiderstand von R. Die Widerstände R weisen die Werte von 10W auf. RV hat den Wert von 10W. RA hat den Wert von 100W. Sofern die Steuerspannung am Schalter kleiner als Vcc/4 (gemessen gegen Masse) ist, befindet sich der Schalter im nichtleitenden Zustand. Liegt die Steuerspannung über Vcc*3/4, so ist der Schalter leitend. Die Zwischenzustände sind nicht definiert und sollen nicht auftreten. DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 13 -----------------------------------------------------------------------Zu Aufg. 5: a) Welcher Zusammenhang besteht zwischen den Strömen I1 und IA sowie zwischen I2 und IA? Wie groß ist IA, wenn der Ausgang nicht belastet wird? b) Wie nennt man diese Schaltung und wo wird diese Schaltung eingesetzt? c) Berechnen Sie Iq für beide möglichen Zustände. d) Tragen Sie für alle zwei Logikzustände und die Werte der gesuchten Spannungen und Ströme in der folgenden Tabelle ein! US I1 I2 I3 I4 IA UA in V in mA in mA in mA in mA in mA in V 0 5 e) Welche Leistung PA wird maximal in RA umgesetzt? f) Wie groß dürfen die Serienwiderstände der Schalter S1 bis S4 maximal sein, damit die Spannung UA einen weiteren Schalter einwandfrei ansteuern kann? g) Wie groß ist der Wirkungsgrad der Schaltung, wenn PA die Nutzlast ist? DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 14 ------------------------------------------------------------------------ Aufg. 6 (20 Punkte) Gegeben ist die folgende Innenbeschaltung eines CMOS-Gatters aus idealen Pund N-MOS Transistoren mit den Eingängen U und V, dem internen Punkt X und dem Ausgang Y. Die Schaltung wird mit Vcc=3V betrieben und alle Transistoren haben die Schaltschwelle von 1,5V. a) Vervollständigen Sie die folgende Tabelle. Zustände mit Spannungen > 2V werden mit einer logischen 1 und Zustände mit Spannungen < 1,0V mit einer logischen 0 gekennzeichnet. U V 0 0 0 1 1 0 b) Um welche Schaltung handelt es sich? X Y DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 15 -----------------------------------------------------------------------Zu Aufg. 6: Gegeben ist nun eine erweiterte CMOS-Schaltung nach dem folgenden Bild mit gleichen Transistoren und gleichen Logikzuständen und –pegeln. Getaktet wird die Schaltung über das Signal Clock (kurz C). c) Gegeben Sie die Logikzustände X und Y über der Zeit im folgenden Diagramm in Abhängigkeit der Eingangssignale U und V sowie des Clock-Signals an. Es müssen keine Laufzeiteffekte berücksichtigt werden. C t U t V X Y t t t d) Wie bezeichnet man diese Schaltung? DTTI – Klausur 07.2006 Heu/Wa Name: Matr.-Nr.: Blatt 16 ------------------------------------------------------------------------ Aufg. 7 (20 Punkte) a) Was sind die elektrischen Eigenschaften eines Kondensators und wie beschreibt man diese bzgl. Größe, Formelzeichen und Einheit? b) Wie wird den Strom I, der durch einen Widerstand fließt, aus der elektrischen Leistung P, die am Widerstand abfällt, und einem Widerstandwert R berechnet? c) Geben Sie mit Zuordnung die 1. und die 2. Kirchhoffsche Regel an. d) Handelt es sich beim CMOS-Transmissiongate um einen Serienschalter oder um ein gegen Masse geschalteten Schalter? e) Lässt sich ein JK-FF aus zwei getakteten D-FFs oder zwei getakteten RS-FFs zusammensetzen? f) Wieviel Transistoren und Kondensatoren gibt es in einer DRAM-Zelle? g) Wie heißen die drei Busssysteme innerhalb eines Mikrocomputers? h) Womit können die elektrischen Informationen auf einem EPROM gelöst werden? i) Wofür stehen innerhalb von CMOS-Speichern die beiden Abkürzungen BL und WL? j) Verwenden modernen (USB-) Speicherkarten EEPROMs oder FEPROMs? k) Woraus bildet sich der Zylinder bei einer Festplatte? l) Ist die Land/Pit-Anordnung einer DVD spiral- oder rundförmig? m) Skizzieren Sie den Prinzipaufbau eines Mikroprozessors?