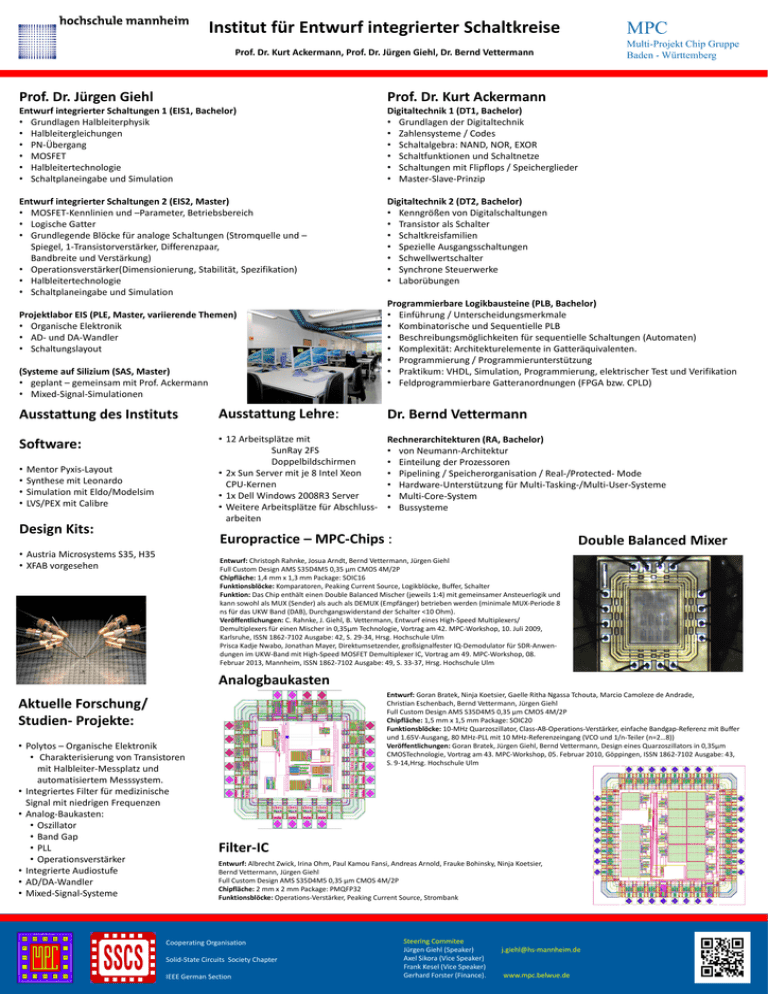

MPC Institut für Entwurf integrierter Schaltkreise - (MPC)

Werbung

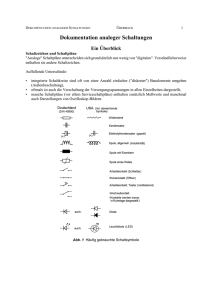

Institut für Entwurf integrierter Schaltkreise MPC Multi-Projekt Chip Gruppe Baden - Württemberg Prof. Dr. Kurt Ackermann, Prof. Dr. Jürgen Giehl, Dr. Bernd Vettermann Prof. Dr. Jürgen Giehl Prof. Dr. Kurt Ackermann Entwurf integrierter Schaltungen 2 (EIS2, Master) • MOSFET-Kennlinien und –Parameter, Betriebsbereich • Logische Gatter • Grundlegende Blöcke für analoge Schaltungen (Stromquelle und – Spiegel, 1-Transistorverstärker, Differenzpaar, Bandbreite und Verstärkung) • Operationsverstärker(Dimensionierung, Stabilität, Spezifikation) • Halbleitertechnologie • Schaltplaneingabe und Simulation Digitaltechnik 2 (DT2, Bachelor) • Kenngrößen von Digitalschaltungen • Transistor als Schalter • Schaltkreisfamilien • Spezielle Ausgangsschaltungen • Schwellwertschalter • Synchrone Steuerwerke • Laborübungen Entwurf integrierter Schaltungen 1 (EIS1, Bachelor) • Grundlagen Halbleiterphysik • Halbleitergleichungen • PN-Übergang • MOSFET • Halbleitertechnologie • Schaltplaneingabe und Simulation Projektlabor EIS (PLE, Master, variierende Themen) • Organische Elektronik • AD- und DA-Wandler • Schaltungslayout (Systeme auf Silizium (SAS, Master) • geplant – gemeinsam mit Prof. Ackermann • Mixed-Signal-Simulationen Digitaltechnik 1 (DT1, Bachelor) • Grundlagen der Digitaltechnik • Zahlensysteme / Codes • Schaltalgebra: NAND, NOR, EXOR • Schaltfunktionen und Schaltnetze • Schaltungen mit Flipflops / Speicherglieder • Master-Slave-Prinzip Programmierbare Logikbausteine (PLB, Bachelor) • Einführung / Unterscheidungsmerkmale • Kombinatorische und Sequentielle PLB • Beschreibungsmöglichkeiten für sequentielle Schaltungen (Automaten) • Komplexität: Architekturelemente in Gatteräquivalenten. • Programmierung / Programmierunterstützung • Praktikum: VHDL, Simulation, Programmierung, elektrischer Test und Verifikation • Feldprogrammierbare Gatteranordnungen (FPGA bzw. CPLD) Ausstattung des Instituts Ausstattung Lehre: Dr. Bernd Vettermann Software: • 12 Arbeitsplätze mit SunRay 2FS Doppelbildschirmen • 2x Sun Server mit je 8 Intel Xeon CPU-Kernen • 1x Dell Windows 2008R3 Server • Weitere Arbeitsplätze für Abschlussarbeiten Rechnerarchitekturen (RA, Bachelor) • von Neumann-Architektur • Einteilung der Prozessoren • Pipelining / Speicherorganisation / Real-/Protected- Mode • Hardware-Unterstützung für Multi-Tasking-/Multi-User-Systeme • Multi-Core-System • Bussysteme • • • • Mentor Pyxis-Layout Synthese mit Leonardo Simulation mit Eldo/Modelsim LVS/PEX mit Calibre Design Kits: Europractice – MPC-Chips : • Austria Microsystems S35, H35 • XFAB vorgesehen Double Balanced Mixer Entwurf: Christoph Rahnke, Josua Arndt, Bernd Vettermann, Jürgen Giehl Full Custom Design AMS S35D4M5 0,35 μm CMOS 4M/2P Chipfläche: 1,4 mm x 1,3 mm Package: SOIC16 Funktionsblöcke: Komparatoren, Peaking Current Source, Logikblöcke, Buffer, Schalter Funktion: Das Chip enthält einen Double Balanced Mischer (jeweils 1:4) mit gemeinsamer Ansteuerlogik und kann sowohl als MUX (Sender) als auch als DEMUX (Empfänger) betrieben werden (minimale MUX-Periode 8 ns für das UKW Band (DAB), Durchgangswiderstand der Schalter <10 Ohm). Veröffentlichungen: C. Rahnke, J. Giehl, B. Vettermann, Entwurf eines High-Speed Multiplexers/ Demultiplexers für einen Mischer in 0,35μm Technologie, Vortrag am 42. MPC-Workshop, 10. Juli 2009, Karlsruhe, ISSN 1862-7102 Ausgabe: 42, S. 29-34, Hrsg. Hochschule Ulm Prisca Kadje Nwabo, Jonathan Mayer, Direktumsetzender, großsignalfester IQ-Demodulator für SDR-Anwendungen im UKW-Band mit High-Speed MOSFET Demultiplexer IC, Vortrag am 49. MPC-Workshop, 08. Februar 2013, Mannheim, ISSN 1862-7102 Ausgabe: 49, S. 33-37, Hrsg. Hochschule Ulm Analogbaukasten Entwurf: Goran Bratek, Ninja Koetsier, Gaelle Ritha Ngassa Tchouta, Marcio Camoleze de Andrade, Christian Eschenbach, Bernd Vettermann, Jürgen Giehl Full Custom Design AMS S35D4M5 0,35 μm CMOS 4M/2P Chipfläche: 1,5 mm x 1,5 mm Package: SOIC20 Funktionsblöcke: 10-MHz Quarzoszillator, Class-AB-Operations-Verstärker, einfache Bandgap-Referenz mit Buffer und 1.65V-Ausgang, 80 MHz-PLL mit 10 MHz-Referenzeingang (VCO und 1/n-Teiler (n=2…8)) Veröffentlichungen: Goran Bratek, Jürgen Giehl, Bernd Vettermann, Design eines Quarzoszillators in 0,35μm CMOSTechnologie, Vortrag am 43. MPC-Workshop, 05. Februar 2010, Göppingen, ISSN 1862-7102 Ausgabe: 43, S. 9-14,Hrsg. Hochschule Ulm Aktuelle Forschung/ Studien- Projekte: • Polytos – Organische Elektronik • Charakterisierung von Transistoren mit Halbleiter-Messplatz und automatisiertem Messsystem. • Integriertes Filter für medizinische Signal mit niedrigen Frequenzen • Analog-Baukasten: • Oszillator • Band Gap • PLL • Operationsverstärker • Integrierte Audiostufe • AD/DA-Wandler • Mixed-Signal-Systeme Filter-IC Entwurf: Albrecht Zwick, Irina Ohm, Paul Kamou Fansi, Andreas Arnold, Frauke Bohinsky, Ninja Koetsier, Bernd Vettermann, Jürgen Giehl Full Custom Design AMS S35D4M5 0,35 μm CMOS 4M/2P Chipfläche: 2 mm x 2 mm Package: PMQFP32 Funktionsblöcke: Operations-Verstärker, Peaking Current Source, Strombank Cooperating Organisation Solid-State Circuits Society Chapter IEEE German Section Steering Commitee Jürgen Giehl (Speaker) Axel Sikora (Vice Speaker) Frank Kesel (Vice Speaker) Gerhard Forster (Finance). [email protected] www.mpc.belwue.de