Ubung Nr. 6 Inhaltsverzeichnis

Werbung

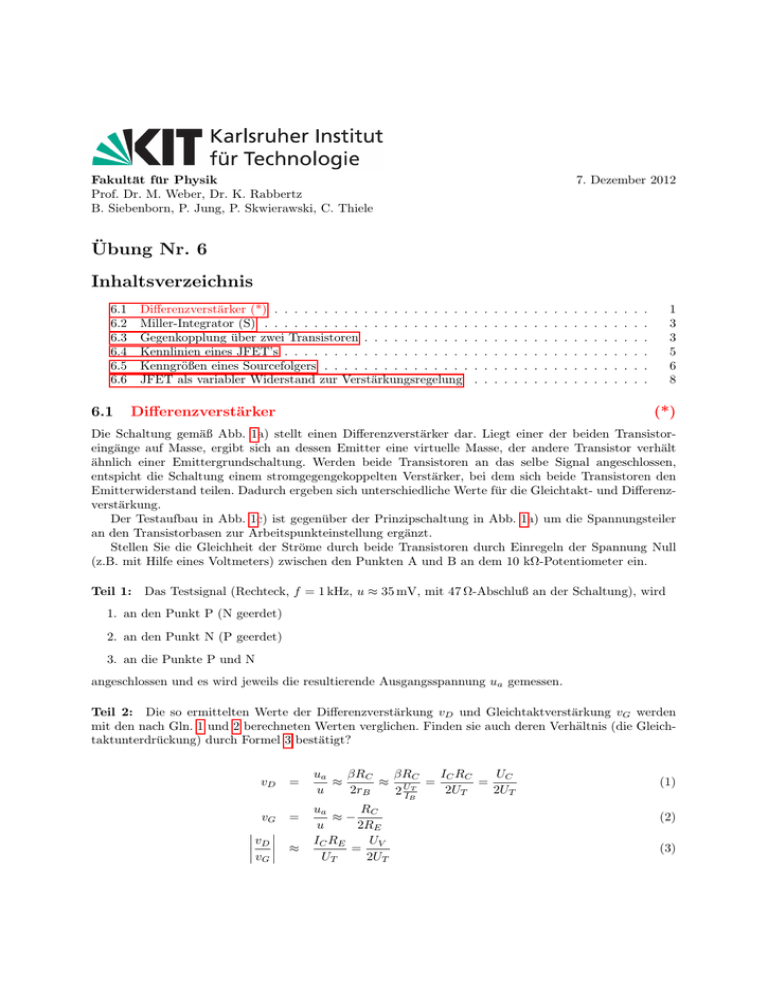

Fakultät für Physik Prof. Dr. M. Weber, Dr. K. Rabbertz B. Siebenborn, P. Jung, P. Skwierawski, C. Thiele 7. Dezember 2012 Übung Nr. 6 Inhaltsverzeichnis 6.1 6.2 6.3 6.4 6.5 6.6 6.1 Differenzverstärker (*) . . . . . . . . . . . . . . . . . . . . Miller-Integrator (S) . . . . . . . . . . . . . . . . . . . . . Gegenkopplung über zwei Transistoren . . . . . . . . . . . Kennlinien eines JFET’s . . . . . . . . . . . . . . . . . . . Kenngrößen eines Sourcefolgers . . . . . . . . . . . . . . . JFET als variabler Widerstand zur Verstärkungsregelung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Differenzverstärker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 3 3 5 6 8 (*) Die Schaltung gemäß Abb. 1a) stellt einen Differenzverstärker dar. Liegt einer der beiden Transistoreingänge auf Masse, ergibt sich an dessen Emitter eine virtuelle Masse, der andere Transistor verhält ähnlich einer Emittergrundschaltung. Werden beide Transistoren an das selbe Signal angeschlossen, entspicht die Schaltung einem stromgegengekoppelten Verstärker, bei dem sich beide Transistoren den Emitterwiderstand teilen. Dadurch ergeben sich unterschiedliche Werte für die Gleichtakt- und Differenzverstärkung. Der Testaufbau in Abb. 1c) ist gegenüber der Prinzipschaltung in Abb. 1a) um die Spannungsteiler an den Transistorbasen zur Arbeitspunkteinstellung ergänzt. Stellen Sie die Gleichheit der Ströme durch beide Transistoren durch Einregeln der Spannung Null (z.B. mit Hilfe eines Voltmeters) zwischen den Punkten A und B an dem 10 kΩ-Potentiometer ein. Teil 1: Das Testsignal (Rechteck, f = 1 kHz, u ≈ 35 mV, mit 47 Ω-Abschluß an der Schaltung), wird 1. an den Punkt P (N geerdet) 2. an den Punkt N (P geerdet) 3. an die Punkte P und N angeschlossen und es wird jeweils die resultierende Ausgangsspannung ua gemessen. Teil 2: Die so ermittelten Werte der Differenzverstärkung vD und Gleichtaktverstärkung vG werden mit den nach Gln. 1 und 2 berechneten Werten verglichen. Finden sie auch deren Verhältnis (die Gleichtaktunterdrückung) durch Formel 3 bestätigt? vD = vG vD vG = ≈ βRC βRC IC RC UC ua ≈ ≈ UT = = u 2rB 2UT 2UT 2 IB ua RC ≈− u 2RE IC RE UV = UT 2UT (1) (2) (3) Praktikum zur Vorlesung Einführung in die Elektronik“ ” 2 UV UV RC I I I RC RC T1 T2 uP ua ua uN u IP 2I I RE 2RE −UV −UV 12V 470Ω 100k 10 µ 470Ω A 100k B T1 T2 ua N P 10k 10µ 1k 6.8k 3.3k −12V Abbildung 1: Differenzverstärker: a) Prinzipschaltbild, b) Ersatzschaltung zur Berechnung der Gleichtaktverstärkung (der Kollektorwiderstand von T1 ist entbehrlich), c) Beispieldimensionierung für einen Versuch mit Signalquelle Praktikum zur Vorlesung Einführung in die Elektronik“ ” 6.2 3 Miller-Integrator (S) Der Miller-Effekt ist die unerwünschte Gegenkopplung eines Transistors bei hohen Frequenzen durch seine Kollektor-Basis Kapazität. Abbildung 2 zeigt die Schaltung eines stromgegengekoppelten Verstärkers, bei dem der Miller-Effekt zur besseren Messbarkeit durch eine externe Kapazität C (1 nF) zwischen Basis und Kollektor verstärkt wird. Teil 1: Mit Widerständen von R = 1 kΩ und R = 10 kΩ wird jeweils die Zeitkonstante τ des Impulsanstiegs oder -abfalls des Ausgangssignals gemessen. Finden sie die Formel 4, wobei Ri der Innenwiderstand C des Signalgenerators inklusive Spannungsteiler ist (vom Punkt ue zurückrechnen!) und vu = − R RE berechnet oder gemessen, bestätigt? 11 00 00 11 12V 2.2k 1 0 0u 1 1.5k 10k C 1 0 0 1 R ue a 1 0 0 1 150Ω 220Ω 11 00 00 11 Abbildung 2: Stromgegengekoppelter Verstärker mit Rechteckimpulsgenerator und externer BasisKollektor-Kapazität zur Demonstration des Miller-Effekts τ ≈ CBC (RC + Ri (1 + |vu |)) (4) Teil 2: Beobachten Sie mit R = 10 kΩ und C = 1 µF am Ausgang eine Dreiecksspannung, das Integral der Rechteckimpulse am Eingang der Schaltung (Miller-Integrator). 6.3 Gegenkopplung über zwei Transistoren Abbildung 3 zeigt die Serienschaltung eines spannungsgegengekoppelten Verstärkers T1 und eines Emitterfolgers T2 für die Verstärkung bipolarer Signale. Die Spannungsverstärkung beträgt für kleine Signale näherungsweise ua R2 v0 = ≈− (5) ue R1 Bei größeren Eingangsspannung sinkt die Verstärkung aber ab, es ergeben sich unerwünschte Nichtlinearitäten. Schließt man R2 nicht an den Kollektor von T1 sondern an den Ausgang ua an (gestrichelt dargestellt), so ergibt sich eine Gegenkopplung über zwei Transistoren. Die dadurch bewirkte Verbesserung v −v der Linearität der Schaltung soll bestimmt werden. Die Nichtlinearität ist definiert als η = 0 vU,max 0 mit der Verstärkung bei maximaler Eingangsspannung vU,max Praktikum zur Vorlesung Einführung in die Elektronik“ ” 4 12V RC 680Ω RE 470Ω u a = 6V R2 6,8k ue uy R1 T1 100Ω T2 ux= ue 2,2k 2,2k 6,8k ua R0 47k −12V 100k Feinabgleich Abbildung 3: a) Gegenkopplung über einen Transistor und (gestrichelt) über zwei Transistoren, b) Schaltung zur gewichteten Addition Gegenkopplung über den Transistor T1 : Die Spannungsverstärkung vU ist gleich dem Produkt der Verstärkungen der in Serie geschalteten Eintransistorschaltungen. Bei Vernachlässigung von Termen höherer Ordnung in 1/β erhält man R2 rB1 rB2 R2 1 rB1 1+ − (6) vU = − 1− 1+ 0 + R0 0 0 R1 β1 R0 ||R1 ||R2 ||RC R0 ||RE β2 RE C 0 0 = RE ||rC2 . Die Transistorkenngrößen rB und β verringern vU gegenüber Gl. 5 = RC ||rC1 , RE mit RC und ihre Arbeitspunktabhängigkeit führt zu Nichtlinearitäten im Prozentbereich. Teil 1: Bestimmen sie zunächst v0 , indem Sie ua über ue im x-y-Betrieb darstellen (beide Oszillographeneingänge auf AC“ 1 ). Überprüfen Sie zuvor, ob der Gleichspannungswert am Ausgang bei ca. 6 V ” liegt. Sollte dies nicht der Fall sein, kann über einen kleinen Gleichspannungsanteil am Funktionsgenerator nachgeregelt werden. Teil 2: Nun soll die Nichtlinearität η bestimmt werden. Da das Absinken des Verstärkungsfaktors nicht direkt erkennbar ist, wird folgender Ansatz verwendet: u v · u v0 − vU,max v0 − ua,max 0 e,max − ua,max ue,max + f · ua,max e,max = η = = (7) = v0 v0 v0 · ue,max ue,max mit f = |1/v0 |. Ein- und Ausgangsspannung müssen also mit dem Gewichtsfaktor f addiert werden, um den Zähler zu ergeben. Diese Addition wird mithilfe des Schaltung in Abb. 3b durchgeführt. Um genau den Gewichtungsfaktor f zu erziehlen, wird der Feinabgleich so eingestellt, dass bei der x-y-Darstellung von uy über ue im Nullpunkt (ue = uy = 0) duy /due = 0 wird (Sattelpunkt). Damit wird ue + f · ua uy = (8) 1+f 1 Bei Problemen mit den USB-Oszilloskopen bitte die Assistenten fragen. Praktikum zur Vorlesung Einführung in die Elektronik“ ” 5 Nun stellt man ue auf den Wert ue,max ein, bei dem die Sättigung von T1 einsetzt. Dann ergibt sich η aus der Beziehung uy,max η = (1 + f ) (9) ue,max Gegenkopplung über die Transistoren T1 und T2 : Teil 3: Die Analyse der linearisierten Ersatzschaltung ergibt für diesen Fall in der bei 6 verwendeten Näherung R2 rB2 R2 1− 1 + (10) vU = − 0 R1 β1 R C R0 ||R1 ||R2 Sowohl die Abweichung von 5 als auch die Nichtlinearität η werden geringer. Um welchen Faktor verbessert sich η gegenüber dem vorhergehenden Fall? 6.4 Kennlinien eines JFET’s Teil 1: Mithilfe der Schaltung nach Abb. 4 (mit Funktionsgenerator auf Dreieck, negative Spannung und relativ niedrige Frequenz) wird die Steuerkennlinie eines JFET’s √ (z.B. BF245C, typengleich mit 2N3819) oszilloskopisch dargestellt und in linearisierter Darstellung ( ID über UGS ) auf Papier übertragen. Entnehmen Sie daraus die Kenngrößen k und UP in Gl. 11. Weiter wird Smax abgelesen und mit dem Wert nach Gl. 12 verglichen. 12V 10k + uX= u GS u e < 0V − 100 R u y = R* i D Abbildung 4: Schaltung zur oszilloskopischen Darstellung der Steuerkennlinie eines JFET’s ID Smax 2 UGS 1− UP = k(UGS − UP ) = IDS dID IDS = = −2 dUGS UGS →0 UP 2 (11) (12) Teil 2: Mithilfe der Schaltung nach Abb. 5 werden einige Ausgangskennlinien des JFET’s oszilloskopisch dargestellt (z.B. UGS = 0, −1V , −2V , −3V bei maximaler uDS -Amplitude). Der Darstellung wird ein mittlerer Wert des dynamischen Drain-Source-Widerstandes rD entnommen. Teil 3: Der lineare Bereich wird vergrößert dargestellt und der minimale Kanalwiderstand RK (UGS = 0) sowie ein möglichst großer Wert RK (UGS < 0) gemessen. Dieser ist durch die oszilloskopische Darstellbarkeit begrenzt. Die Beobachtungen werden nach Einfügen von R1 = R2 = 1 MΩ, d.h. nach Verbesserung der Linearität, wiederholt (s. Gl. 13). UGS 1 = 2k − UP (13) RK 2 Praktikum zur Vorlesung Einführung in die Elektronik“ ” 6 10k 1:2 − R1 uX= u DS R2 ug + u GS 100 R u y = R* i D Abbildung 5: Schaltung zur oszilloskopischen Darstellung der Ausgangskennlinie eines JFET’s (R1 = ∞, R2 = 0) mit Demonstration der Linearitätsverbesserung (R1 = R2 = 1 MΩ) 6.5 Kenngrößen eines Sourcefolgers Die Schaltung gemäß Abb. 6a) ist in Betrieb zu nehmen. Teil 1: Bestimmen Sie folgende Größen. • Die Spannungsverstärkung vU ist oszilloskopisch zu ermitteln und mit Gl. 14 zu vergleichen. • Die Steilheit S im Arbeitspunkt (≈ 5 mA/V) kann aus den beigefügten Datenblatt entnommen werden. • Zur Bestimmung der Ausgangsimpedanz wird der Ausgang mit RL = 470 Ω belastet. Aus der Abnahme von ua ergibt sich Za . • Finden sie die Beziehung 16 bestätigt? vU = Ze = Za = S+ 1 rG (R||rD ||rG ) ≈ 1 + S(R||rD ||rG ) rG ≈ rG (1 + SR) 1 − vU R||rD ||rG 1 ≈ 1 + S(R||rD ||rG ) S+ SR 1 + SR (14) (15) 1 R (16) Teil 2: Zur Abschätzung der Eingangsimpedanz Ze wird die Aufladung eines eingangsseitigen Kondensators C am Ausgang der nach Abb. 6b) modifizierten Schaltung beobachtet. (C ist ein Kondensator mit großem Isolationswiderstand. Bei kurzgeschlossenem Eingang (Ue =0) wird zunächst die Ausgangsspannung Ua0 gemessen. Dann wird der Kurzschluß entfernt und die Dauer ∆t gemessen, in der Ua 20% des Anstieges von Ua0 auf Uaf durchgeführt hat. Näherungsweise gilt nach einer Taylor-Entwicklung der exponentiellen Ladekurve: 5vU ∆t Ze = (17) C Unter Verwendung von vU aus der ersten Teilaufgabe können Ze und mit 15 auch der dynamische GateSource-Widerstand rG berechnet werden. Praktikum zur Vorlesung Einführung in die Elektronik“ ” 1µ 33k 7 BF245C 12V ue ua 1k R 220 µ 150 Ω 1M 12V ue 12V 11 00 00 11 11 00 00 11 470 Ω 11 00 00 11 C 3.3n RL ua R 150 11 00 00 11 Abbildung 6: Sourcefolger mit JFET: a) Schaltung zur Bestimmung der Spannungsverstärkung und Ausgangsimpedanz und b) der Eingangsimpedanz Praktikum zur Vorlesung Einführung in die Elektronik“ ” 8 +12V 100k 10k 470k ue T1 ua 1µ 10k −12V 1M 10k N1 1M Abbildung 7: Stromgegengekoppelter Verstärker mit bipolarem npn-Transistor und n-Kanal-JFET als steuerbarem Emitterwiderstand zur Verstärkungsregelung 6.6 JFET als variabler Widerstand zur Verstärkungsregelung Bei dem stromgegengekoppelten Verstärker nach Abb. 7 ist der Arbeitspunkt des bipolaren Transistors T1 mit Hilfe des 100 kΩ-Reglers so einzustellen, daß bei UGS = 0 am JFET N1 (maximale Verstärkung) das Kollektorruhepotential von T1 auf +5 V liegt. Damit wird erreicht, daß die Schaltung bei Verstärkungsänderung mittels UGS im Bereich geeigneter Arbeitspunkte verbleibt und der Aussteuerbereich für bipolare Signale maximal ist. Zu untersuchen ist der Bereich einstellbarer Verstärkungen und der jeweilige Aussteuerbereich. Bei der vorgegebenen Dimensionierung und mit den Transistortypen T1 = 2N2219A, N1 = BF245C sollten sich Verstärkungsfaktoren etwa zwischen −0.5 und −50 einstellen lassen.