Langfassung

Werbung

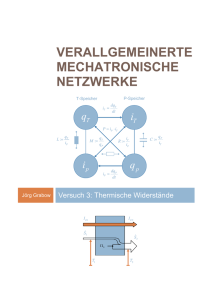

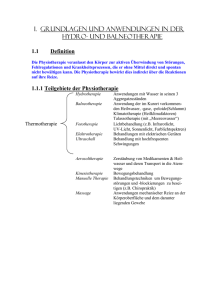

13.ASIM-Tagung Simulationstechnik, Weimar, 17.09.99, Tagungsband , 265-272 Modellierung und Simulation thermisch-elektrischer Wechselwirkungen in integrierten Schaltkreisen Peter Schwarz Fraunhofer-Institut für Integrierte Schaltungen / EAS Dresden email: [email protected] Stefan Wünsche Siemens Components Inc., Essex Junction (USA) email: [email protected] 1. Einleitung Die ständige Verkleinerung der elektronischen Bauelemente und ihrer Abstände in integrierten Schaltungen führt zu zunehmenden elektrisch-thermischen Wechselwirkungen. Während für die Simulation des elektrischen Verhaltens von Schaltungen seit langem erprobte Werkzeuge bereitstehen, wird die thermische Analyse wenig durch Tools unterstützt. Die beim Leiterplattenentwurf und der Gehäusekonstruktion angewandten Verfahren lassen sich nicht unmittelbar beim Schaltkreisentwurf einsetzen. Ein universeller Ansatz besteht in der zweioder dreidimensionalen Beschreibung der thermischen Vorgänge im Chip durch partielle Differentialgleichungen und deren numerischer Lösung mit FEM-Simulatoren wie ANSYS oder ABAQUS. Allerdings ist damit noch nicht die thermisch-elektrische Wechselwirkung erfaßt. In den letzten Jahren wurden erste Ansätze veröffentlicht, diese Wechselwirkungen zu erfassen und zu berechnen [1], [2], [3], [4], [5], [8]. Für die Berechnung der thermisch-elektrischen Wechselwirkungen gibt es zwei grundsätzliche Lösungswege: - Das elektrische und das thermische Teilsystem werden getrennt modelliert und jeweils mit unterschiedlichen Simulatoren behandelt; die Wechselwirkung wird durch eine Simulatorkopplung berücksichtigt [2], [3]. - Es wird ein gemeinsames Modell konstruiert, das mit einem Simulator simuliert wird. Hier wird der zweite Weg untersucht und ein Rechenprogramm TSMG („Thermal Solver and Model Generator“) vorgestellt, mit dessen Hilfe ein thermisches Modell für die thermischelektrische Simulation mit einem Schaltungssimulator automatisch erzeugt werden kann [6]. Im Bild 1 sind die Eingangs- und Ausgabedaten des Tools grob skizziert. Der Anwender gibt neben der elektrischen Netzliste u. a. die Layout-Koordinaten der temperaturerzeugenden und der temperatursensitiven Schaltelemente ein. Es wird dabei angenommen, daß nicht alle Elemente gleichermaßen wichtig für die Berechnung des thermischelektrischen Verhaltens sind. Die Anzahl dieser relevanten Elemente bestimmt die Größe (die Anzahl der Gleichungen) des thermischen Modells und sollte daher auf die notwendigen Schaltelemente beschränkt bleiben. Es wird zunächst nur das statische Verhalten berücksichtigt, also die Berechnung des temperaturabhängigen Arbeitspunktes der elektrischen Schaltung und die daraus resultierende Temperaturverteilung auf der Chipoberfläche. Das Werkzeug TSMG soll nicht andere, sehr genaue Tools für die Thermische Analyse ersetzen. Es soll vielmehr dem Chipdesigner helfen, temperaturkritische Schaltelementeanord- 265 nungen und Auswirkungen einer anderen Elementeplazierung schnell zu erkennen. Da der thermische Mehrpol in die für die Schaltungssimulation ohnehin benötigte Netzliste eingefügt wird, kann auch mit den üblichen Schaltungssimulatoren (ergänzt durch temperaturabhängige Schaltelementmodelle) gearbeitet werden. Q14 Q4 Q5 Q2 Q1 Q20 Q17 Q3 Isothermenplot Q6 TSMG die Bauelementelage Verlustleistung Finite-Differenzen Methode Chipgröße Gehäuseinformation Sparse-Matrix-Technik Thermisches Modell Conjugate-Gradient Methode SPICE-Format MAST HDL-A VHDL-AMS Tcl / Tk Bild 1: Thermal Solver and Model Generator 2. Lösungsweg In dieser Arbeit sollen nicht die mathematischen Lösungsalgorithmen detailliert vorgestellt werden; vielmehr soll die Anwendersicht im Vordergrund stehen. Das Verfahren und das Tool TSMG lassen sich zusammengefaßt so beschreiben: - Ausgangspunkt sind die vollständige Netzliste (also die Transistorschaltung), das Layout und Angaben zum Chip im Gehäuse. - Für das Chip wird ein dreidimensionales thermisches Modell aufgestellt. - Die geometrische Lage der temperaturerzeugenden und der temperatursensitiven Elemente wird vom Anwender vorgegeben; diese Elemente werden durch die Namen aus der Netzliste eindeutig der Schaltung zugeordnet. - Durch die Diskretisierung des partiellen Differentialgleichungssystems entsteht ein sehr großes algebraisches Gleichungssystem (einige hunderttausend Variable sind durchaus üblich!). - Aus diesem Gleichungssystem wird ein thermisches Modell abgeleitet (als Verhaltensbeschreibung oder in Form eines thermischen Netzwerkes). - Dieses Modell (ein „thermischer Mehrpol“) wird in die Netzliste der elektrischen Schaltung eingefügt und über seine Anschlüsse mit den temperaturerzeugenden und den temperatursensitiven Bauelementen verknüpft. - Dabei werden modifizierte Transistormodelle [6], [7] verwendet, die eine zusätzliche „thermische Klemme“ besitzen. - Das Chipgehäuse, der Substratträger, die Bonddrähte usw. werden durch ein vorformuliertes thermisches Ersatznetzwerk berücksichtigt, dessen Elementewerte aus konstruktiven und Materialdaten berechnet werden. - Die erweiterte Schaltung, also einschließlich thermischem Mehrpol, wird mit dem Schaltungssimulator berechnet (gekoppelte elektrisch-thermische Simulation). 266 - Die daraus resultierenden Verlustleistungen der relevanten Elemente werden benutzt, um die Temperaturverteilung auf der Chipoberfläche zu berechnen. Von anderen Ansätzen (z. B. [5], [8]) unterscheidet sich das implementierte Verfahren durch die Art der inhomogenen Diskretisierung der Chipgeometrie, die numerischen Verfahren zur Extraktion eines genauen Verhaltensmodells mit drastisch reduzierter Anzahl von Variablen und die konsequente Orientierung auf kommerziell verfügbare Schaltungssimulatoren wie SPICE, Saber oder ELDO sowie den Einsatz standardisierter Verhaltensbeschreibungssprachen für die Modellierung (das künftige VHDL-AMS und die gegenwärtigen „de-facto-Standards“ MAST und HDL-A). Ein graphisches User-Interface dient der Darstellung der Lage der für die thermisch-elektrischen Wechselwirkungen relevanten Transistoren und der Temperaturverteilung auf der Chipoberfläche in Form von Isothermen. Bild 2 zeigt vereinfacht ein elektrisch-thermisches System: im linken Teil ist ein Ausschnitt aus der elektrischen Schaltung zu sehen, im rechten Bild sind die Positionen der Wärmequellen und der temperaturempfindlichen Elemente auf dem Chip angegeben. So sind z.B. Q14 und Q20 die Bauelemente, die die meiste Wärme erzeugen, Q1 und Q2 sind temperaturempfindliche Bauelemente mit vernachlässigbarer Verlustleistung. Bei den skizzierten Isothermen wurde von einem elektrischen Arbeitspunkt ausgegangen, in dem Q20 (und nicht Q14) die überwiegende Wärme in das Chip einspeist. Es ist wichtig, mehrere Arbeitspunkte und Betriebszustände der Schaltung zu berechnen, da sich daraus sehr unterschiedliche Temperaturverteilungen ergeben können. Eine Mittelung kann dabei sehr wesentliche Effekte verdecken. Sauber zu lösen ist dieses Problems jedoch nur durch eine dynamische Analyse (s. Punkt 5). Leistungserzeugende Bauelemente Q14, Q20 Temperatursensitive Bauelemente Q1,Q2 Wärmequellen Q14, Q20 VCC=+15V Q9 Q8 Q14 Q1 Q2 Q14 Q19 T3 6 T4 Q4 Q2 Q18 Q16 Q7 Q5 Q20 Q23 Q6 Bauelement Isotherme Q5 Q1 Q20 Q17 Q3 Q6 Chip Q20 Q17 Träger Integrierte Schaltung Bild 2 Chip und Chipträger Elektrische Schaltung und zugehörige Temperaturverteilung auf dem Chip 267 3. Modellierung des thermischen Systems Im Bild 3 ist die zugrundegelegte Geometrie des Chips und des Gehäuses dargestellt. Konvektion, Strahlung Chipträger Gehäuse Chip Träger (Leadframe) Leiterplatte Wärmeleitung Konvektion, Strahlung Bild 3 Thermische Pfade der Anordnung Chip/Gehäuse/Leiterplatte Während Chipträger, Bonddrähte und andere Teile ausreichend genau durch thermische Widerstände beschrieben werden können [6], wird das Chip durch ein dreidimensionales Modell beschrieben (Bild 4). Dabei wird eine inhomogene Diskretisierung gewählt, um die im wesentlichen in den oberen Schichten des Chips konzentrierte thermisch-elektrische Wechselwirkung hinreichend genau zu modellieren. Im Bild 4 sind drei thermische Wärmequellen eingezeichnet, die elektrischen Bauelementen (Transistoren, Widerstände) mit hoher Verlustleistung entsprechen sollen. Rz faßt mehrere thermische Widerstände zusammen, die den Wärmefluß über Chipträger, Gehäuse, ... modellieren (vgl. auch Bild 7). PV1 PV2 Rz PV3 Verlustleistungsquellen der Einzelbauelemente isotherme Chipunterseite TUmgebung Bild 4 Berechnungsmodell des TSMG 268 Wenn man von folgenden Annahmen für die näherungsweise Temperaturberechnung ausgeht: - die Wärmeausbreitung erfolgt isotrop, d. h. die Wärmeleitfähigkeit im Chip ist weder ortsnoch richtungsabhängig, - die Wärmeleitfähigkeit ist nicht temperaturabhängig, - es wird nur das statische Verhalten betrachtet so läßt sich die Wärmeleitungsgleichung in Form einer POISSONschen Differentialgleichung formulieren: λ 2 2 ∂2 ∂ ∂ ∆T = λ T+ T+ T = – p ( x, y, z ) 2 2 ∂ x2 ∂y ∂z (1) Dabei ist ∆ der LAPLACE-Operator, T ( x, y, z ) die ortsabhängige Temperatur und p die an der Stelle ( x, y, z ) je Volumenelement eingespeiste Wärmemenge (die Wärmequellendichte). Zur numerischen Lösung der partiellen DG (1) wird ein „Finite-Differenzen-Verfahren“ [8], [9] eingesetzt. Es verwendet zentrale Differenzen für die ersten und zweiten Ableitungen. Die entstehenden Gleichungen lassen sich bekanntlich anschaulich als „thermisches Widerstandsnetzwerk“ deuten (im Bild 5 für äquidistante Gitterpunkte gezeichnet). z+h y+h Wärmeeinspeisung p z y x-h x+h y-h x z-h Bild 5 Thermisches Widerstandsnetzwerk Durch die Diskretisierung und den Finite-Differenzen-Ansatz entsteht ein lineares algebraisches Gleichungssystem G mit T=P (2) G = Matrix der thermischen Leitwerte T = Vektor der Temperaturen an den Gitterpunkten P = Vektor der in die Gitterpunkte eingespeisten Wärmeströme Bei der Verwendung des Ausdrucks „thermische Leitwerte“ ist die Veranschaulichung gemäß Bild 5 benutzt worden. Die Matrix G hat N Zeilen und N Spalten. Bei einer durchaus üblichen Diskretisierung von N = 100 6 100 6 5 = 50.000 Gitterpunkten entsteht also ein sehr großes Gleichungssystem, das allerdings „schwach besetzt“ ist: nur weit unter einem Prozent aller Matrixelemente ist von Null verschieden, ebenso auch nur wenige Elemente der rechten Seite P . Diese Besonderheit nutzt man bei der Implementierung des Lösungsverfahrens aus, indem nur die von Null verschiedenen Elemente gespeichert werden (sparse matrix techniques). Zur Lösung des Gls. (2) wurde das Verfahren der konjugierten Gradienten [9] mittels der Programmbibliothek [10] implementiert. Bei bekannten elektrischen Verlustleistungen der Schaltelemente kann nun die 269 Temperaturverteilung im Chip berechnet werden (Bild 6 zeigt die Temperaturverteilung auf der Oberfläche). Bild 6 Temperatur der Chipoberfläche in Isothermendarstellung 4. Modellierung der thermisch-elektrischen Wechselwirkung Für die Berechnung der elektrisch-thermischen Wechselwirkungen kann ausgenutzt werden, daß für diese Aufgabe ein reduziertes Gleichungssystem mit n Zeilen und Spalten ( n « N ) ausreichend ist: M Tr = Pr (3) n ist die Anzahl m der wärmeerzeugenden Schaltelemente + Anzahl s der temperatursensiblen Schaltelemente (wenn ein Element zu beiden Gruppen gehört, wird es nur einmal gezählt). Typische Werte von n liegen zwischen 5 und 50. Tr und Pr sind die Vektoren der Temperaturen bzw. eingespeisten Wärmeströme an diesen Gitterpunkten. M ist i. d. R. eine vollbesetzte Matrix, deren Elemente sich durch m-maliges Lösen des Gls. (2) mit speziellen rechten Seiten bestimmen lassen. M läßt sich als „thermische Admittanzmatrix“ eines thermischen Mehrpols deuten. Hier liegt auch ein wesentlicher Unterschied zu [8]: dort wird ein dem sehr großen Gls. (2) entsprechendes Ersatznetzwerk in die Schaltungssimulation einbezogen, hier wird ein um mehrere Größenordnungen kleineres und trotzdem genaues Modell verwendet. Gl. (3) beschreibt - im Rahmen der eingeführten Diskretisierung - das thermische System 270 exakt. Es hat nur deshalb eine kleinere Dimension, weil nur ausgewählte, nämlich alle „wichtigen“ Gitterpunkte benutzt werden. Im Bild 7 ist an einem Beispiel gezeigt, wie dieser thermische Mehrpol bei der Modellierung der thermisch-elektrischen Wechselwirkungen eingesetzt wird. Ein Ausschnitt aus der Schaltung zeigt einen wärmeerzeugenden Transistor Q20, dessen Temperatur T_Q20 wiederum bekannt sein muß, um den fließenden Strom berechnen zu können. Im Bild 7 ist angedeutet, daß für Q20 ein modifiziertes Transistormodell [6], [7] verwendet wird, an dessen zusätzlicher Klemme die aktuelle Temperatur anliegt und durch die die erzeugte Wärme in das thermische System eingespeist wird. Ein zweites temperatursensitives Schaltelement ist der Widerstand R1, der allerdings keinen nennenswerten Wärmestrom in das thermische System einspeist. Daher wird an der thermische Klemme des Elementes R1 auch nur die Temperatur T_R1 dem Verhaltensmodell R(T) übergeben. Elektrische Schaltung E Elektrothermische Schnittstelle Q20 R1 T E1 R(T) B C E2 T_Q20 Thermisches Chipmodell ..... T_R1 Thermischer Mehrpol T_Unterseite RChip+RKleber+RTräger Thermisches Gehäusemodell RGehäuse + RKonvektion RLücke+RPin+RLeiterplatte RKonvektion TUmgebung Bild 7 Beschaltung des thermischen Mehrpols 5. Ausblick Die ersten Erfahrungen zeigen, daß das Ziel - die thermisch-elektrischen Wechselwirkungen und die Auswirkung von modifizierten Schaltelementeanordnungen auf dem Chip rasch überschlägig zu berechnen - mit TSMG erreicht wird. Der Modellansatz kann relativ leicht durch orts- und richtungsabhängige thermische Leitfähigkeit erweitert werden. Als wesentlicher wird jedoch die Einbeziehung des dynamischen Verhaltens, also die Berücksichtigung 271 der Wärmespeicherung angesehen. Dabei ist das eigentliche Problem weniger die Erweiterung der Gls. (1), (2), sondern die Einbeziehung der dynamischen Effekte in das thermische Mehrpolmodell mit seiner erheblich reduzierten Anzahl von Variablen. Wenn es aber gelingt, auch die thermischen Zeitkonstanten in den thermischen Mehrpol einzubeziehen, lassen sich mit dem Schaltungssimulator auch die dynamischen Vorgänge in eng gekoppelten elektrischthermischen Systemen berechnen. Wir danken unseren Kollegen Dr. Joachim Haase, Gunter Kurth, Roland Martin und Frank Winkler für die Mitarbeit am Konzept und an der Implementierung von TSMG und für die Unterstützung bei der Vorbereitung dieser Veröffentlichung. 6. Literatur [1] Szekely, V.; Csendes, A.; Rencz, M.: mS-THERMANAL: An efficient thermal simulation tool for microsystem elements and MCM’s. Proc. 2nd THERMINIC Workshop, Budapest, Hungary, Sept. 25-27, 1996, 13-20. [2] Wünsche, S.: Simulator coupling for electro-thermal simulation of integrated circuits. Proc. 2nd THERMINIC Workshop, Budapest, 25.-27. September 1996, 89-93 [3] Wünsche, S.; Clauß, C.; Schwarz. P.; Winkler, F.: Electro-thermal circuit simulation using simulator coupling. IEEE Trans. VLSI- 5,(1997)3, 277-282 [4] Szekely, V.; Rencz, M.: Fast field solver for thermal and electrostatic analysis. Proc. DATE’98, Paris 1998, 518-523. [5] Willemen, J.: Elektrothermische Schaltungssimulation mit Saber unter Einbeziehung des Gehäuseeinflusses. Proc. ANALOG’99, München, Februar 1999 [6] Wünsche, S.: Ein Beitrag zur Einbeziehung thermisch-elektrischer Wechselwirkungen in den Entwurfsprozeß integrierter Schaltungen. Dissertation TU Chemnitz, Mai 1998 [7] Leitner, Th.: Electro-thermal simulation using a circuit simulator and a modified SPICE3 semiconductor model library. Proc. MIXDES’98 (5th Intern.Workshop „Mixed Design of Integrated Circuits and Systems“), Lodz, Poland, 18.-22.6.1998, pp. 189-194. [8] Digele, G.; Lindenkreuz, S.; Kasper, E.: Fully coupled dynamic electro-thermal simulation. IEEE Trans. VLSI-5(1997)3, 250-257 [9] Törnig, W.; Gipser, M.; Kaspar, B.: Numerische Lösung von partiellen Differentialgleichungen der Technik. Teubner, Stuttgart 1991 [10] Press, W.H. et al.: Numerical Recipes in C. Cambridge University Press, New York 1995 272