03.Gleichstromverhalten von CMOS

Werbung

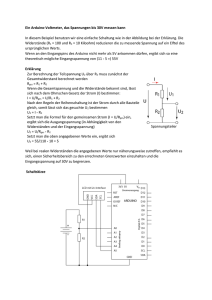

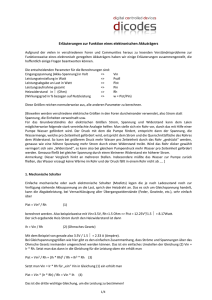

Gleichstromverhalten von CMOS-Invertern Andreas Heyer für Proseminar „Statische CMOS-Schaltungen“ im Sommersemester 2005/FSU Jena Professor Dr. Eberhard Zehendner Gliederung 1. 2. 3. 4. 5. Inverter Wirkungsweise eines CMOS-Inverters Übertragungskennlinie und Kennwerte Übersicht über Industriestandards Beispielrechnung zu den Inverterkennwerten 2 Boolsche Logik: Inverter • Boolsche Eingabevariable A • Inverter:= NOT A • Abbildung der Variablen A auf Spannungswerte • 0=L, 1=H • Verschiedene Logiklevel-Standards: TTL, CMOS A NOT A 0 1 1 0 A A 3 Inverter mit bipolarem npn-Transistor VDD A=Vout Vin =A • Eingangsspannung A • Ausgangsspannung Vout • Vout=VCE=VDD-ICER • Bei A=1=H schaltet der Transistor durch • Vout wird 0 • Bei A=0=L ist der Transistor gesperrt • Vout wird VDD 4 Nachteile • Bipolarer Transistor: Stromfluss an der Basis, ständiger Leistungsabfall • Stromfluss durch den Widerstand R • Ständiger Energieverbrauch im durchgeschaltetem Zustand, also unnötige Verluste • Integration von Widerständen in integrierten Schaltungen sehr aufwändig, zum Teil auch nicht möglich 5 Inverter mit MOSFET VDD R A=Vout Vin =A • Ersatz des npnTransistors durch MOSFET • Kein Schaltstrom mehr • Ersatz des Widerstandes R durch einen Transistor: Widerstand durch VR einstellbar • Weiterhin Stromfluss und Verluste beim Schalten des Eingangs A auf 1 6 CMOS-Inverter VDD Vin =A A=Vout • Zusammenschaltung eines nMOS- mit einem pMOS-Transistor • Wirkungsweise eines Umschalters • Hochohmiger Schalteingang • Nur geringe Leistungsabfälle beim Umschalten des Inverters 7 Nachweis der Inverterwirkung(1) • Statische Zustände ohne Berücksichtigung von Frequenzabhängigkeiten (Kapazitäten) oder Stromflüsse durch Verbraucher am Ausgang • Betrieb der Transistoren im Sperrbereich und im voll durchgeschalteten Sättigungsbereich • Strecke Drain-Source: – 500 bis 1000Ω im leitenden Zustand – 10 bis 20 MΩ im gesperrten Zustand • Vin im Bereich 0V bis VDD • VGSn=Vin • VSGp=VDD-Vin 8 Nachweis der Inverterwirkung(2) • Eingang A=1: High Level – Vin=VDD: – Mp gesperrt – Mn durchgeschaltet – Verbindung des Ausgangs Vout mit Masse – Vout≈0V – Mp wirkt als Pull-Down-Transistor 9 Nachweis der Inverterwirkung(3) • Eingang A=0: Low Level – Vin=0V: – Mn gesperrt – Mp durchgeschaltet (VGSp=Vin-VDD<0V) – Verbindung des Ausgangs Vout mit der Spannungsversorgung – Vout≈VDD – Mp wirkt als Pull-Up-Transistor 10 Nachweis der Inverterwirkung(4) A Vin NOT A Vout 0 0V 1 VDD 1 VDD 0 0V • Positive Logic • Werte für VDD und die Logiklevel durch verschiedene Schaltungsstandards festgelegt 11 Vergleich der Übertragungskennlinien verschiedener Inverter 12 Voltage-Transfer-Curve 13 Output Low Voltage • VOL: Kleinstmöglicher Spannungswert am Ausgang • Für Vin=VDD>VDD-|VTp| ist Mp gesperrt (cutoff) • Mn ist aktiv, IDn=0A (kein Verbraucher), deshalb VDSn=0V • VOL=Vout= VDSn=0V • Unvermeidliche Leckströme bewirken aber einen geringen Strom IDn im Bereich µA/nA • Damit ist VOL=Vout= VDSn≈1mV in der Realität 14 Output High Voltage • VOH: Größtmöglicher Spannungswert am Ausgang • Für Vin<VTp ist Mn gesperrt (cutoff) • Mp ist aktiv, IDp=0A (kein Verbraucher), deshalb VSDp=0V • VOH=Vout= VSDp=VDD-VSDp=VDD • Unvermeidliche Leckströme bewirken ebenfalls einen geringen Strom IDn im Bereich µA/nA • Damit ist VOH=Vout= VSDp≈VDD-1mV in der Realität 15 Output Logic Swing • VL=VOH-VOL=VDD • Ausgangsänderung über die gesamte Spannungsbreite • Ausgangswerte liegen an den Grenzen des Spannungsbereiches und weit auseinander • Dadurch wohldefinierte Logikwerte möglich und auch real unterscheidbar 16 Input Low Voltage (1) • VIL: Größtmögliche Eingangsspannung, die als logische 0 (L) interpretiert wird • Damit Vout=VOH stabil bei rund VDD und als logische 1 (H) interpretierbar • Für Vin>VIL geht die Schaltung in einen instabilen Übergangszustand, in dem beide Transistoren (teilweise) durchschalten • Damit sind sowohl die Eingangs- wie auch die Ausgangswerte in Spannungsbereichen, die keine genaue Zuordnung zu den Logikleveln ermöglichen 17 Input Low Voltage (2) • Stabilitätsbereiche aus der Übertragungskurve erkennbar • Vermeiden des Bereiches mit dem steilen Abfall • Definitionspunkt für VIL: Anstieg der Kurve hat Wert -1 • Begründung: Bei nur geringfügiger Steigerung von V über VIL änderte sich sonst Vout drastisch, also instabiles Verhalten • Es gilt: IDn=IDp • Mn im gesättigten, Mp im ungesättigten Modus 18 Input Low Voltage (3) VDSn = Vout , VGSn = Vin VSDp = VDD − Vout , VSGp = VDD − Vin I Dn = I Dp βn (Vin − VTn ) βp ( 2 VDD − Vin − VTp 2 2 Differenzieren nach Vin 2 = ) (VDD − Vout ) − (VDD − Vout ) ( β n (Vin − VTn ) = β p − (VDD − Vout ) − VDD − Vin − VTp Mit ) 2 (1) dVout dV + (VDD − Vout ) out dVin dVin dVout dVout = = −1 dVin dVIL β β Vin 1 + n = 2Vout − VDD − VTp + n VTn β βp p (2) 19 Input High Voltage (1) • VIH: Kleinstmögliche Eingangsspannung, die als logische 1 (H) interpretiert wird • Damit Vout=VOL stabil bei rund 0V und als logische 0 (L) interpretierbar • Für Vin<VIH geht die Schaltung in einen instabilen Übergangszustand, in dem beide Transistoren (teilweise) durchschalten • Damit sind sowohl die Eingangs- wie auch die Ausgangswerte in Spannungsbereichen, die keine genaue Zuordnung zu den Logikleveln ermöglichen 20 Input High Voltage (2) • Stabilitätsbereiche aus der Übertragungskurve erkennbar • Vermeiden des Bereiches mit dem steilen Abfall • Definitionspunkt für VIH: Anstieg der Kurve hat Wert -1 • Begründung: Bei nur geringfügiger Senkung von V unter VIH änderte sich sonst Vout drastisch, also instabiles Verhalten • Es gilt: IDn=IDp • Mp im gesättigten, Mn im ungesättigten Modus 21 Input High Voltage (3) VDSn = Vout , VGSn = Vin VSDp = VDD − Vout , VSGp = VDD − Vin I Dn = I Dp β βn ( 2 (Vin − VTn )Vout − Vout 2 = p VDD − Vin − VTp 2 2 Differenzieren nach Vin ) 2 (1) dVout dV + Vout + Vout out = − β p VDD − Vin − VTp dVin dVin dVout dVout Mit = −1 = dVin dVIH ( β n (Vin − VTn ) β β Vin 1 + p = 2Vout + VTn − p VDD − VTp βn βn ( ) ) (2) 22 Threshold-/Midpoint-Voltage (1) • VTH=VM: Spannung, bei der sich beide Transistoren in der Mitte der Übergangsregion der VTC befinden • Schnittpunkt der VTC mit der Geraden Vout=Vin • Ungefähre Mitte zwischen VIL und VIH • Markiert den Übergang zwischen den Logikleveln am Ein- und Ausgang • Beide Transistoren im gesättigten, leitenden Zustand 23 Threshold-/Midpoint-Voltage (2) Vout = Vin = VTH = VM I Dn = I Dp βn 2 βp (VM − VTn ) = 2 2 VDD − VTp + VM = 1+ Für ( VDD − VM − VTp ) 2 βn VTn βp βn βp βn V = 1 wird VM ≅ DD βp 2 24 Zusammenfassung: Critical Voltages • 0≤Vin≤VIL: Vout=VDD • Damit Vin als logische 0, Vout als logische 1 interpretierbar • VIH≤Vin≤VDD: Vout=0 • Damit Vin als logische 1, Vout als logische 0 interpretierbar • Immer: VIL≤VM≤VIH • Vin<VM: Eingabe möglicherweise log. 0 • Vin>VM: Eingabe möglicherweise log. 1 25 Noise Margins • Rauschgrenzen für für Spannungsfremdeinstrahlung (z.B. durch parasitäre Kopplungen) • Messwerte für die Resistenz des Inverters gegen ungewollte Umschaltungen • Für Logiklevel 0: VNML=VIL-VOL=VIL • Für Logiklevel 1: VNMH=VOH-VIH=VDD-VIH • Innerhalb dieser Grenzen bleiben die Logiklevel gewahrt 26 Critical Voltages/ Noise Margins 27 Implementierung im IC 28 TTL-Pegel • VDD=5V • Eingang: – 0 (L): Vin≤0,8V – 1 (H): Vin≥2,0V • Ausgang: – 0 (L): Vout≤0,4V – 1 (H): Vout≥2,4V • Standard-CMOS-Logik benötigt teilweise Pegelanpassung bei Verwendung mit der älteren TTL-Logik auch im 5V-Betrieb 29 Vergleich CMOS-TTL: Vorteile • Größerer Spannungsbereich (3 bis 15V) • Symmetrische und rechteckförmige Übertragungskennlinie • Symmetr. Impulsflanken und Verzögerungszeiten • Extrem niedriger Leistungsbedarf im Ruhezustand • Geringer Bedarf bei niedrigen Taktfrequenzen • Geringere Temperaturabhängigkeit • Unempfindlicher Gegenüber der Speisespannung 30 Vergleich CMOS-TTL: Nachteile • Größerer Ausgangswiderstand (bis 1kΩ) • Größere Verzögerungszeiten • Längere Impulsflanken 31 JEDEC-Standard • 1976 EIA/JEDEC-Standard für alle CMOSHersteller • Joint Electron Devices Council • Vereinheitlichung von Betriebsparametern, Datenblättern und Messmethoden • Festlegungen für Minimal- und Maximalwerte • Gilt für die 4000er Baureihe • Pufferung der Ausgänge 32 CMOS-Baureihen • • • • CD4000A: 1968-1976 CD4000/4500B: ab 1976 HEF4000B: ab 1976 High-Speed 74HC...: ab 1981 33 Literatur • Neil H. E. Weste, Kamran Eshraghian: Principles of CMOS VLSI Design, 2nd ed., Addison-Wesley, 1999 • John P. Uyemura: CMOS Logic Circuit Design, Kluwer, 1999 • Kühn: Handbuch TTL- und CMOSSchaltkreise, 2. Auflage, VEB Verlag Technik, Berlin, 1986 34